芯片設(shè)計從RTL代碼一直到最后流片的GDSII文件,都是文本文件,因此,掌握文本分析處理語言是集成電路設(shè)計的一項重要的基本功。本公眾號一直致力于推廣采用文本分析工具來提升仿真和綜合效率的方法。詳見本公眾號專輯《芯片設(shè)計課程及相關(guān)實驗》。本文是孫義雯同學(xué)采用Python語言實現(xiàn)的Vivado和Modelsim聯(lián)合仿真的自動化腳本,已經(jīng)在實際項目中經(jīng)過較長時間的檢驗,今天開源出來,供大家學(xué)習(xí),歡迎留言交流心得體會和改進(jìn)建議。同時,后續(xù)我們會陸續(xù)推出基于Python的Verilog代碼智能化分析處理文章,敬請期待。

我們在Windows系統(tǒng)下使用Vivado的默認(rèn)設(shè)置調(diào)用第三方仿真器比如ModelSim進(jìn)行仿真時,一開始仿真軟件都會默認(rèn)在波形界面中加載testbench頂層的信號波形,并自行仿真1000ns后停止。當(dāng)我們想查看對應(yīng)模塊的波形時,需要自己去手動添加,并且為了防止跑一段時間仿真后,添加新模塊或者信號卻發(fā)現(xiàn)沒有記錄波形,就要提前手動在控制臺上執(zhí)行l(wèi)og -r 。/*命令來實現(xiàn)對全部信號波形的記錄。但是每當(dāng)我們修改完代碼,關(guān)閉重啟仿真器再一次仿真時,就需要將之前的操作(刪改添加對應(yīng)模塊信號,執(zhí)行l(wèi)og -r 。/*等)重新完成一遍才能繼續(xù)跑出想看的信號波形。

盡管可以通過將仿真時添加的模塊信號保存為*.do文件,下次仿真通過執(zhí)行do *.do的形式來快速添加之前波形;但在頻繁修改代碼,需要經(jīng)常重新仿真的情況下,每次都手動去添加信號的操作會比較影響到我們的情緒,那么能否通過腳本語言比如Python來實現(xiàn)一鍵仿真并自動添加好所需要的模塊信號呢?首先我們需要對Vivado軟件實現(xiàn)第三方仿真的過程進(jìn)行分析,弄清楚其中的步驟。 Vivado軟件第三方仿真分析

1.1 Vivado調(diào)用第三方軟件方式

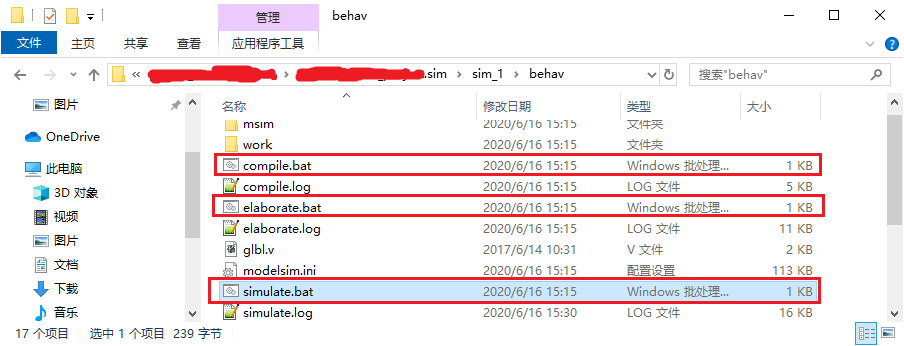

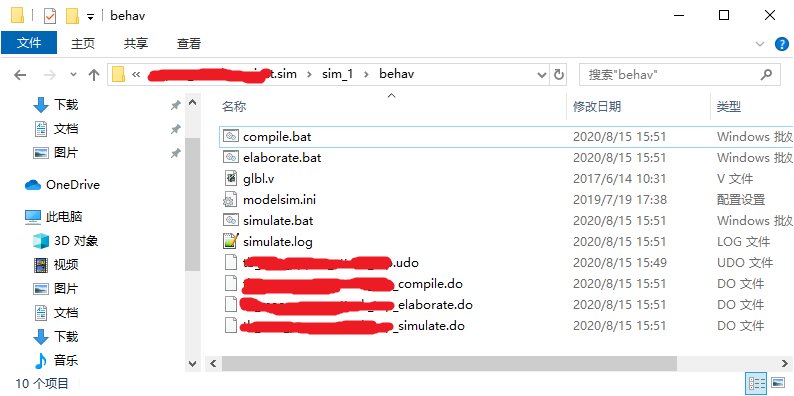

參考之前的文章:用Modelsim獨立仿真帶Vivado IP核的仿真工程,我們可以知道Vivado軟件執(zhí)行和生成仿真文件是在工程的仿真目錄工程名.sim/下,然后我們打開一個示例工程的仿真目錄,如圖所示

結(jié)合圖片和文章我們可以看出,Vivado軟件調(diào)用第三方仿真器的方式,是根據(jù)之前在工程文件中設(shè)置的仿真器路徑和聯(lián)調(diào)庫路徑等參數(shù),在工程仿真目錄下生成一系列仿真用的Tcl腳本和系統(tǒng)的批處理腳本(Linux下就是shell),通過系統(tǒng)命令執(zhí)行上面的批處理腳本(先compile,再elaborate,最后simulate),來調(diào)用第三方仿真軟件實現(xiàn)仿真功能。

1.2 Vivado仿真腳本分析

上面圖片中共有三個批處理腳本:compile.bat、elaborate.bat、simulate.bat。依次分別實現(xiàn)了三種功能:compile、elaborate、simulate。下面我們對每個批處理腳本的內(nèi)容分別進(jìn)行分析。

1.2.1 compile相關(guān)腳本

compile.bat腳本全部內(nèi)容如下:

@echo offset bin_path=C:questasim64_10.6cwin64call %bin_path%/vsim -c -do “do {xxxxxxxx_compile.do}” -l compile.logif “%errorlevel%”==“1” goto ENDif “%errorlevel%”==“0” gotoSUCCESS:ENDexit 1:SUCCESSexit 0

本工程設(shè)置的第三方仿真器為Questasim,腳本中具體功能實現(xiàn)在第2和第3行:

設(shè)置二進(jìn)制文件路徑bin_path;

調(diào)用該路徑下的vsim程序執(zhí)行do {xxxxxxxx_compile.do}命令。

其中的xxxxxxxx_compile.do是跟批處理腳本同一目錄下的Tcl腳本文件,文件內(nèi)容如下(已添加注釋):

######################################################################## File name : xxxxxxxx_compile.do# Created on: Fri Aug 14 1609 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation########################################################################新建work庫vlib work#新建msim庫vlib msim

#新建msim/xil_defaultlib庫vlib msim/xil_defaultlib

#將目前的邏輯工作庫xil_defaultlib和實際工作庫msim/xil_defaultlib映射對應(yīng)vmap xil_defaultlib msim/xil_defaultlib

#編譯verilog代碼文件(VHDL文件需要用vcom命令),編譯到xil_defaultlib庫下vlog -64 -incr -work xil_defaultlib #vivado的官方IP核提供的仿真代碼文件“。。/。。/。。/xxxxxxxxxxxx.srcs/sources_1/ip/xxxxxxxxxxxx/xxxxxxxxxxxx_sim_netlist.v” “。。/。。/。。/xxxxxxxxxxxx.srcs/sources_1/ip/xxxxxxxxxxxx/xxxxxxxxxxxx_sim_netlist.v” “。。/。。/。。/xxxxxxxxxxxx.srcs/sources_1/ip/xxxxxxxxxxxx/xxxxxxxxxxxx_sim_netlist.v” “。。/。。/。。/xxxxxxxxxxxx.srcs/sources_1/ip/xxxxxxxxxxxx/xxxxxxxxxxxx_sim_netlist.v” “。。/。。/。。/xxxxxxxxxxxx.srcs/sources_1/ip/xxxxxxxxxxxx/xxxxxxxxxxxx_sim_netlist.v” #工程中自行編寫的代碼文件“。。/。。/。。/。。/rtl/xxx/xxxxxxx.v” “。。/。。/。。/。。/rtl/xxxx/xxxxxxx.v” 以下省略若干行的代碼文件。。.。。.。。

# compile glbl modulevlog -work xil_defaultlib “glbl.v”

#強制退出quit -force

看過上述代碼和注釋,我們可以了解到compile腳本通過調(diào)用第三方仿真器執(zhí)行對應(yīng)的Tcl腳本xxxxxxxx_compile.do實現(xiàn)了對工程中代碼文件的編譯,其中xxxxxxxx_compile.do中會寫入全部工程代碼文件的路徑。

1.2.2 elaborate腳本

elaborate.bat腳本全部內(nèi)容如下:

@echo offset bin_path=C:questasim64_10.6cwin64call %bin_path%/vsim -c -do “do {xxxxxxxx_elaborate.do}” -l elaborate.logif “%errorlevel%”==“1” goto ENDif “%errorlevel%”==“0” goto SUCCESS:ENDexit 1:SUCCESSexit 0

同樣可以看出,該腳本中實現(xiàn)的具體功能為:

設(shè)置二進(jìn)制文件路徑bin_path;

調(diào)用該路徑下的vsim程序執(zhí)行do {xxxxxxxx_elaborate.do}命令。

其中xxxxxxxx_elaborate.do腳本的內(nèi)容如下(已加注釋):

######################################################################## File name : xxxxxxxx_elaborate.do# Created on: Fri Aug 14 1615 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation########################################################################vopt是在使用vcom或vlog編譯設(shè)計后對其執(zhí)行全局優(yōu)化vopt -64 +acc=npr -L xil_defaultlib -L unisims_ver -L unimacro_ver -L secureip -L xpm -work xil_defaultlib xil_defaultlib.xxxxxxxxx xil_defaultlib.glbl -o xxxxxxxxx_opt#強制退出quit -force

可以看出上述腳本主要實現(xiàn)的功能是對代碼編譯后的設(shè)計文件進(jìn)行全局優(yōu)化。

1.2.3 simulate腳本

simulate.bat腳本全部內(nèi)容如下:

@echo offset bin_path=C:questasim64_10.6cwin64call %bin_path%/vsim -do “do {xxxxxxxx_simulate.do}” -l simulate.logif “%errorlevel%”==“1” goto ENDif “%errorlevel%”==“0” goto SUCCESS:ENDexit 1:SUCCESSexit 0

該腳本中實現(xiàn)的具體功能為:

設(shè)置二進(jìn)制文件路徑bin_path;

調(diào)用該路徑下的vsim程序執(zhí)行do {xxxxxxxx_simulate.do}命令。

其中xxxxxxxx_simulate.do腳本的內(nèi)容如下(已加注釋):

######################################################################## File name : xxxxxxxx_simulate.do# Created on: Fri Aug 14 1622 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation########################################################################指定vsim查找設(shè)計單元的默認(rèn)工作庫為xil_defaultlib,并對指定的優(yōu)化后的設(shè)計開始仿真vsim -lib xil_defaultlib xxxxxxxx_opt

#設(shè)置變量NumericStdNoWarnings為1,即禁用在加速的numeric_std和numeric_bit包中生成的警告set NumericStdNoWarnings 1#設(shè)置變量StdArithNoWarnings為1,即禁用在加速Synopsys標(biāo)準(zhǔn)軟件包中生成的警告set StdArithNoWarnings 1

#執(zhí)行xxxxxxxx_wave.do文件中的tcl指令do {xxxxxxxx_wave.do}

#打開wave窗口view wave#打開structure窗口view structure#打開signals窗口view signals

#執(zhí)行xxxxxxxx.udo文件中的tcl指令do {xxxxxxxx.udo}

#仿真1000nsrun 1000ns

該腳本中實現(xiàn)了調(diào)用第三方仿真軟件對優(yōu)化后的設(shè)計開始仿真,調(diào)出仿真界面,執(zhí)行xxxxxxxx_wave.do腳本,打開仿真相關(guān)窗口,并繼續(xù)執(zhí)行xxxxxxxx.udo腳本。下面我們接著給出xxxxxxxx_wave.do腳本的內(nèi)容:

######################################################################## File name : `xxxxxxxx_wave.do# Created on: Fri Aug 14 1622 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation########################################################################添加當(dāng)前模塊內(nèi)(即仿真頂層模塊)信號add wave *#添加GSR(全局復(fù)置位信號)add wave /glbl/GSR

可知xxxxxxxx_wave.do腳本文件主要功能是實現(xiàn)對仿真波形的添加。而另一個xxxxxxxx.udo腳本中無實際內(nèi)容:

######################################################################## File name : xxxxxxxx.udo# Created on: Wed Jun 10 1649 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation#######################################################################

說明在默認(rèn)設(shè)置下,Vivado是不通過xxxxxxxx.udo腳本執(zhí)行命令的。

1.2.4 仿真腳本總結(jié)

至此,我們基本弄清楚了這三個腳本的功能以及與其他腳本文件之間的關(guān)系:

compile.bat腳本主要實現(xiàn)對仿真代碼文件的編譯;

elaborate.bat腳本主要對編譯后的設(shè)計進(jìn)行全局的優(yōu)化,并生成優(yōu)化后的結(jié)果;

simulate.bat腳本則是具體調(diào)出仿真軟件界面對優(yōu)化后的設(shè)計進(jìn)行仿真,控制仿真軟件相關(guān)窗口的顯示、模塊信號的添加等等其他與最終波形仿真相關(guān)的操作。

于是,如果想通過python腳本實現(xiàn)仿真自動化添加波形等的操作,那么就需要在simulate.bat腳本及其相關(guān)的do腳本文件上做文章。

1.3 Vivado仿真功能選項

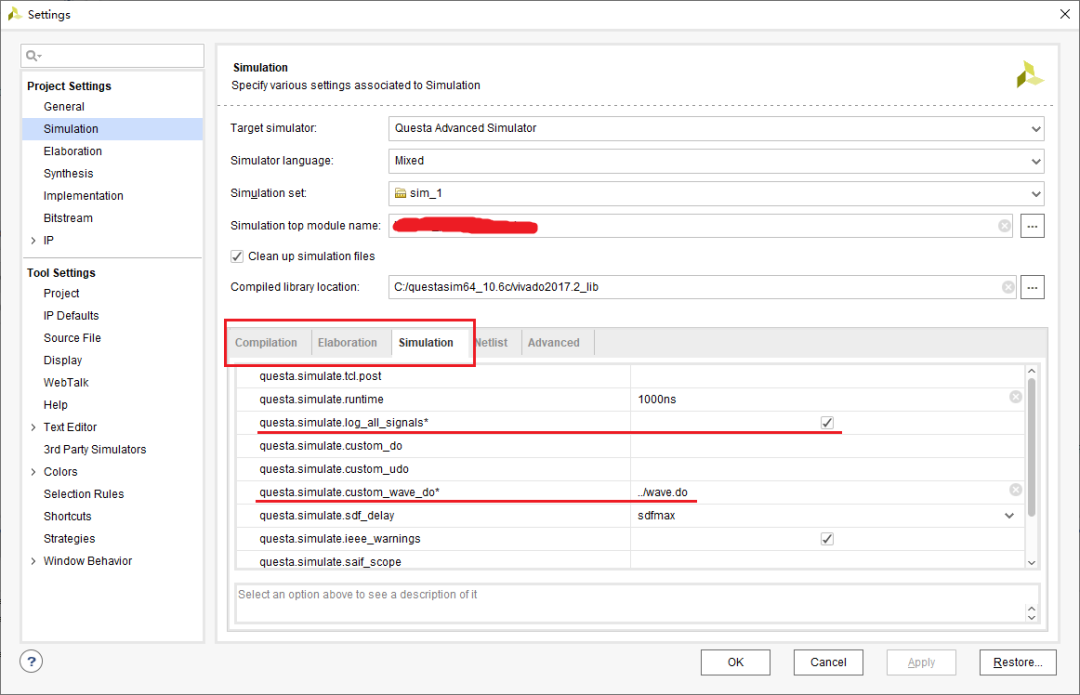

在進(jìn)一步分析Vivado仿真操作,思考如何使用python腳本實現(xiàn)我們想要的自動化之前,我們可以先問這樣一個問題:難道Vivado軟件真的沒有提供仿真自動添加自定義波形等等方便仿真操作的功能嗎?關(guān)于這個問題,我們可以先去查看Vivado軟件仿真功能自帶的仿真選項,就在設(shè)置第三方仿真器路徑和聯(lián)調(diào)庫路徑的地方,如圖所示:

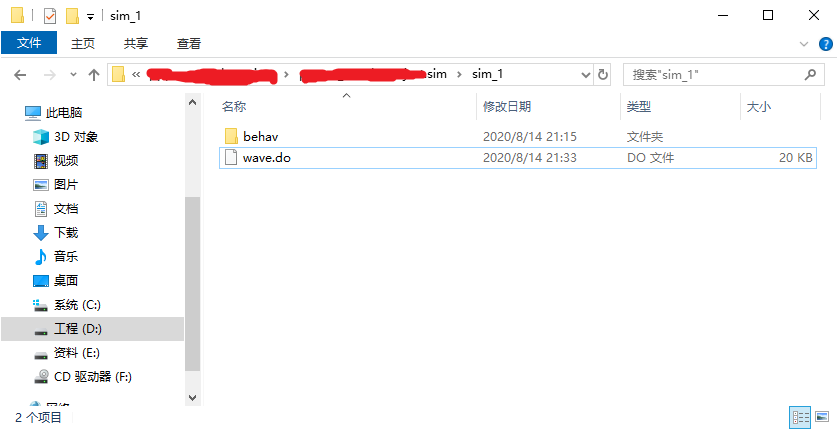

可以看到在下面紅框中有三個標(biāo)簽頁Compilation、Elaboration、Simulation,分別對應(yīng)仿真時的三個步驟和生成的相關(guān)腳本文件。打開Simulation標(biāo)簽頁,我們可以看到下面有多行選項,其中就有runtime仿真時間,默認(rèn)是1000ns。然后下一行紅橫線上內(nèi)容是log_all_signals,“記錄全部信號”,那這個是仿真自動執(zhí)行l(wèi)og -r 。/*命令的選項嗎?我們先將該選項打勾。然后接著向下看,有個custom_wave_do的選項,在上面腳本分析中我們知道xxxxxxxx_wave.do腳本文件實現(xiàn)的是仿真添加模塊信號的功能,那這里是仿真添加自定義信號的選項嗎?這里我將之前該工程仿真保存的一版信號文件wave.do拷貝到仿真腳本所在behave目錄的上一級目錄下:

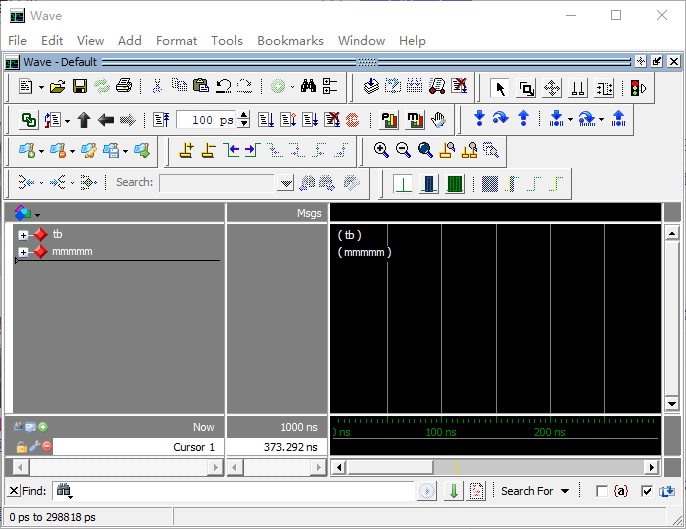

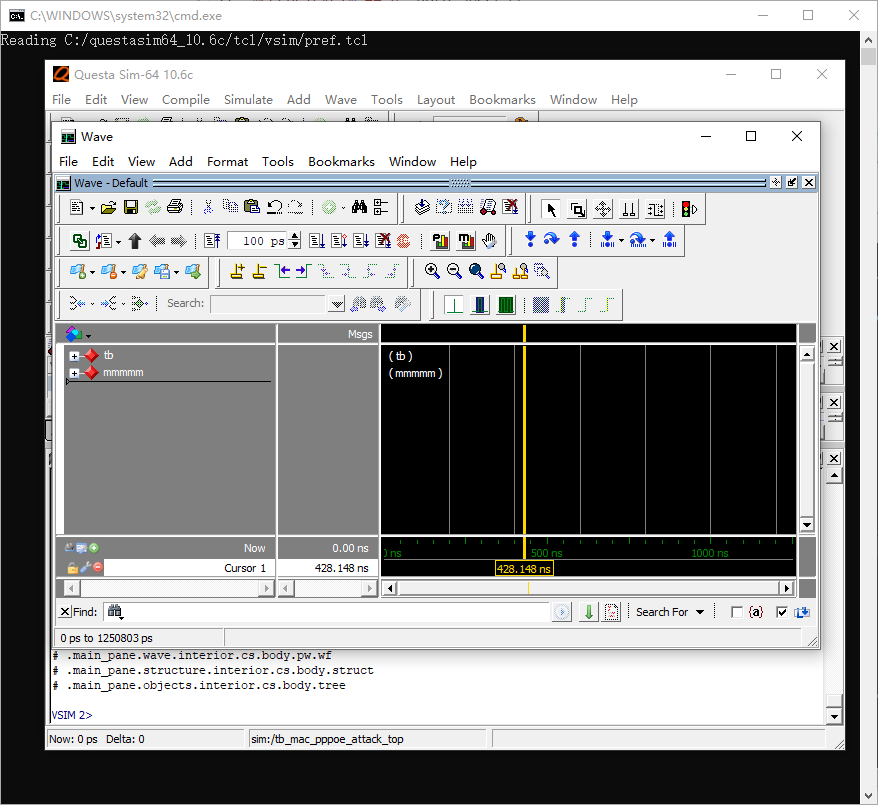

然后如上面仿真選項圖中所示寫入custom_wave_do選項的路徑為:。。/wave.do,然后重新開始仿真。出現(xiàn)仿真波形界面如圖:

該界面中添加的信號分組與。。/wave.do文件中設(shè)置的信號相同,說明這里實現(xiàn)了對自定義信號的自動添加。接著我們再打開仿真目錄下的xxxxxxxx_simulate.do腳本查看,其內(nèi)容如下:

######################################################################## File name : xxxxxxxx_simulate.do# Created on: Fri Aug 14 2140 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation#######################################################################vsim -lib xil_defaultlib xxxxxxxx_opt

set NumericStdNoWarnings 1set StdArithNoWarnings 1

do {。。/wave.do}

view waveview structureview signals

log -r /*

do {xxxxxxxx.udo}

run 1000ns

可以看到在Vivado生成的該腳本中第14行和第20行,已經(jīng)自動添加上了do {。。/wave.do}和log -r /*的命令,說明的確在仿真時就可以實現(xiàn)自動記錄全部信號波形和自動添加自定義信號的操作。因此,Vivado本身就已經(jīng)提供了這樣方便的仿真操作選項,如果只是想實現(xiàn)自動記錄全部信號波形和自動添加保存的自定義信號波形操作的話,我們直接設(shè)置修改仿真選項中的log_all_signals和custom_wave_do兩個選項的內(nèi)容即可。但是初出茅廬的我并沒有想到向Vivado提出問題,而是按照自己的想法開始了Python腳本的折騰之路。

初步設(shè)想功能的Python實現(xiàn)在1.2節(jié)對仿真腳本的分析中,我們知道了如果想實現(xiàn)仿真自動添加和記錄信號的功能,就需要對仿真最后一步simulate.bat相關(guān)的腳本進(jìn)行對應(yīng)的修改。但首先,這些腳本都是Vivado仿真時自動生成的,那如果一開始沒有腳本,或者我們添加了一些代碼文件后,腳本需要更新怎么辦?(compile.bat相關(guān)的.do腳本中沒有新加入的代碼文件的路徑,自然就無法去編譯新的代碼)因此我們就需要首先讓Vivado來產(chǎn)生仿真相關(guān)的最新腳本,再去實現(xiàn)對腳本的更改。

2.1 Vivado軟件仿真腳本生成

參考實驗室張仲禹同學(xué)的這篇文章

實驗室自研工具Vivado Batch Mode Tool介紹!

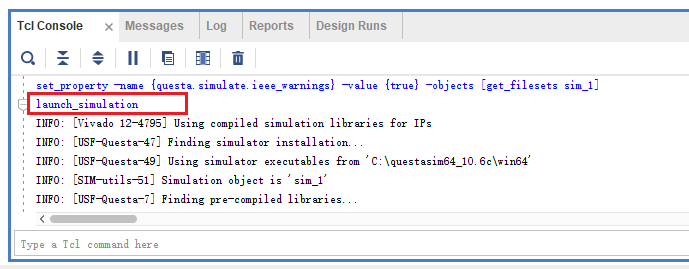

https://mp.weixin.qq.com/s/EcrZl8iM0SZbpLrlXUJ6CA,我們可以了解到Vivado軟件在運行上提供了批處理模式batch mode,通過批處理模式和Tcl腳本可以讓Vivado軟件對特定工程執(zhí)行具體功能。因此這里只要利用批處理模式讓Vivado軟件對當(dāng)前工程生成仿真腳本即可。那么如何去查找生成仿真腳本的對應(yīng)指令呢?當(dāng)我們點擊Vivado工程GUI界面的仿真按鈕時,界面底部的控制臺Tcl Console便會立刻顯示并執(zhí)行l(wèi)aunch_simulation的命令,如圖所示:

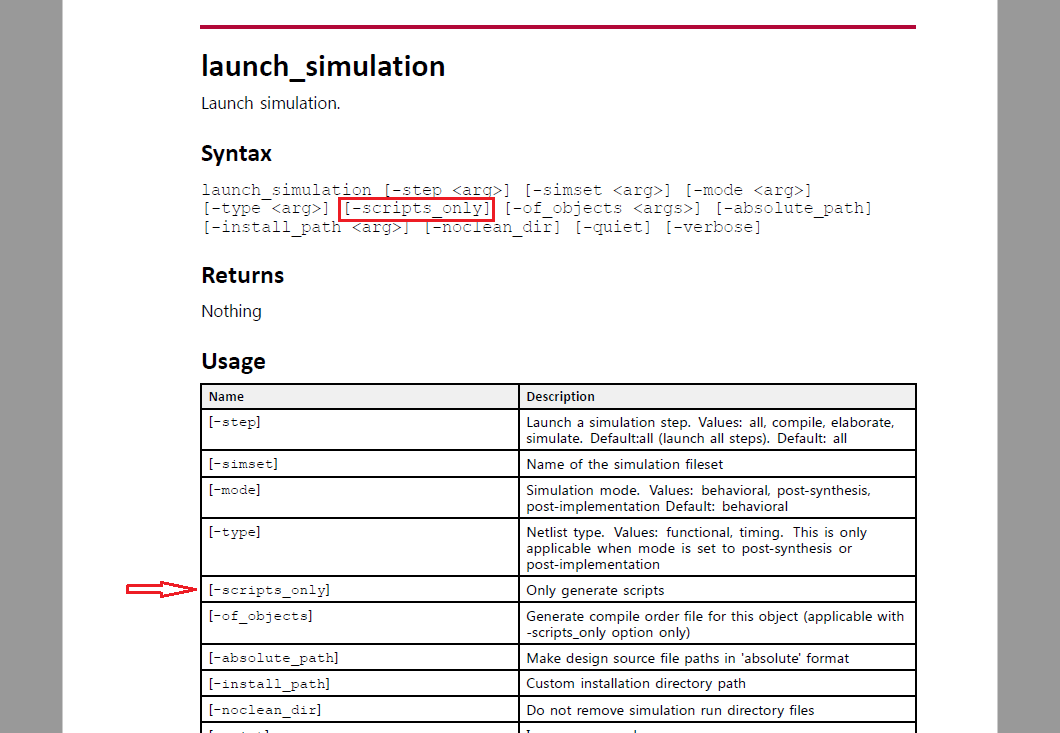

我們打開Vivado的Tcl命令手冊UG835,查找到launch_simulation命令詞條如下:

launch_simulation命令是運行仿真的命令,可以看到語法中有一個-scripts_only選項,其描述是:僅生成腳本。這里的腳本自然是相關(guān)的仿真腳本。只要利用這個命令選項就能實現(xiàn)對工程仿真腳本的生成。當(dāng)然,我們想實現(xiàn)的是功能仿真,因此在執(zhí)行該命令時,最好在上面的-mode選項中選擇behavioral。那么,實現(xiàn)對功能仿真腳本生成功能的命令就應(yīng)該是:launch_simulation -mode behavioral -scripts_only,為了驗證命令正確性,我們可以利用Vivado工程的GUI界面提前進(jìn)行測試,在刪除仿真目錄下的文件后,在命令控制臺Tcl Console輸入并執(zhí)行該命令,執(zhí)行完后檢測仿真目錄下是否生成了相關(guān)腳本,經(jīng)過驗證,該命令可以生成仿真腳本。

2.2 功能實現(xiàn)思路

至此,我們針對功能的實現(xiàn)思路做如下總結(jié):

使用Python調(diào)用Vivado軟件的批處理模式batch mode執(zhí)行l(wèi)aunch_simulation -mode behavioral -scripts_only命令,來生成當(dāng)前工程的功能仿真腳本;

利用python可以對生成的simulate.bat相關(guān)的腳本內(nèi)容進(jìn)行修改,添加log -r 。/*以實現(xiàn)自動記錄全部信號波形,添加執(zhí)行自定義wave.do腳本命令或?qū)⑾胩砑拥男盘栁募?nèi)容替換進(jìn)默認(rèn)生成的xxxxxxxx_wave.do腳本中,完成仿真時對自定義信號的自動化添加;

使用python中的系統(tǒng)函數(shù)庫依次執(zhí)行compile.bat、elaborate.bat、simulate.bat腳本,調(diào)出仿真界面執(zhí)行仿真。

2.3 具體實現(xiàn)

2.3.1 使用Python調(diào)用Vivado軟件生成仿真腳本

具體實現(xiàn)代碼和注釋如下:

import os

# 指定工程xpr文件路徑XprFilePath = ‘xxxxxxxx_project.xpr’# 指定Tcl腳本路徑SimTclFilePath = ‘sim.tcl’

# 命令-在使用命令行調(diào)用Vivado軟件前需要運行的批處理文件SourceSettingsFileCmd = ‘call C:/Xilinx/Vivado/2017.2/settings64.bat’ # 命令-調(diào)用Vivado軟件的batch mode打開當(dāng)前工程文件并執(zhí)行Tcl腳本中的生成仿真腳本命令VivadoBatchModeScriptsCmd = ‘vivado -mode batch -source ’ + SimTclFilePath + ‘ -nojournal -nolog ’ + XprFilePath

# 組合前兩條命令并調(diào)用系統(tǒng)函數(shù)依次執(zhí)行os.system(SourceSettingsFileCmd + ‘ && ’ + VivadoBatchModeScriptsCmd)

其中上面代碼中用到的sim.tcl文件內(nèi)容為:

#僅生成仿真腳本launch_simulation -mode behavioral -scripts_only

將兩個腳本放置于工程xpr文件的同目錄下,使用Python3執(zhí)行,執(zhí)行后仿真目錄結(jié)果如下:

接下來我們依次對生成的腳本進(jìn)行檢查,查看本次使用Vivado的batch mode生成的仿真腳本與第一章中腳本內(nèi)容是否存在差別。經(jīng)過對比,發(fā)現(xiàn)除了xxxxxxxx_simulate.do文件和simulate.bat腳本存在一點差別外,其他腳本內(nèi)容完全相同,存在差別的腳本內(nèi)容如下xxxxxxxx_simulate.do內(nèi)容:

######################################################################## File name : xxxxxxxx_simulate.do# Created on: Sat Aug 15 1541 +0800 2020## Auto generated by Vivado for ‘behavioral’ simulation#######################################################################vsim -lib xil_defaultlib xxxxxxxx_opt

set NumericStdNoWarnings 1set StdArithNoWarnings 1

do {xxxxxxxx_wave.do}

view waveview structureview signals

do {xxxxxxxx.udo}

run 1000ns

quit -force

內(nèi)容差別在最后一行,相比Vivado的GUI界面下點擊仿真按鈕生成的腳本,batch mode下使用仿真選項-scripts_only生成腳本xxxxxxxx_simulate.do的最后一行額外添加了強制退出的命令quit -force,這會導(dǎo)致調(diào)出的仿真程序在執(zhí)行完全部的仿真命令后,立刻關(guān)閉界面并退出程序,所以仿真時,我們需要在該腳本執(zhí)行前刪除掉該命令。simulate.bat內(nèi)容:

@echo offset bin_path=C:questasim64_10.6cwin64call %bin_path%/vsim -c -do “do {xxxxxxxx_simulate.do}” -l simulate.logif “%errorlevel%”==“1” goto ENDif “%errorlevel%”==“0” goto SUCCESS:ENDexit 1:SUCCESSexit 0

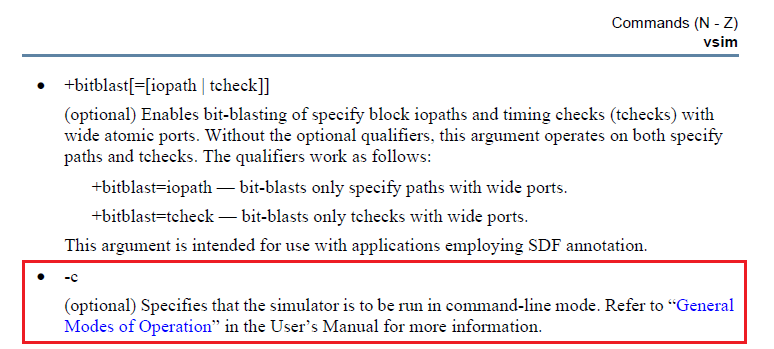

內(nèi)容差別在第三行,在vsim命令后多出了一個-c的選項,查找QuestaSim命令手冊中vsim詞條的-c選項描述如圖:

可以看出-c選項是以命令行模式command-line mode執(zhí)行vsim命令,也就是說,該選項執(zhí)行后打開的不是仿真軟件的GUI界面,而是黑乎乎的命令行界面,這將導(dǎo)致我們無法實時查看跑出的仿真波形,所以在仿真時,-c也需要刪除掉。內(nèi)容差別總結(jié)因此,在后續(xù)對腳本的處理中,我們除了添加log -r 。/*命令和將想添加的信號替換進(jìn)xxxxxxxx_wave.do腳本中之外,還需要額外刪除腳本xxxxxxxx_simulate.do最后一行的quit -force,以及腳本simulate.bat中vsim命令后的-c。

2.3.2 使用Python修改并執(zhí)行仿真腳本

具體實現(xiàn)代碼和注釋如下:

import os

# 仿真目錄路徑SimDirPath = ‘xxxxxxxx.sim/sim_1/behav/’# compile批處理腳本名稱CompileBatName = ‘compile.bat’# elaborate批處理腳本名稱ElaborateBatName = ‘elaborate.bat’# simulate批處理腳本名稱SimulateBatName = ‘simulate.bat’# 由于所執(zhí)行的腳本內(nèi)容里存在一些相對路徑,所以在執(zhí)行腳本前,需要將系統(tǒng)路徑切換到所執(zhí)行腳本所在的目錄下# 執(zhí)行Compile腳本os.system(‘cd ’ + SimDirPath + ‘ && ’ + ‘call ’ + CompileBatName)# 執(zhí)行Elaborate腳本os.system(‘cd ’ + SimDirPath + ‘ && ’ + ‘call ’ + ElaborateBatName)

# 修改xxxxxxxx_simulate.do腳本,刪除run 1000ns和quit -force,添加log -r 。/*SimulateDoFile = open(SimDirPath + ‘xxxxxxxx_simulate.do’, ‘r’)SimulateDoFileAllLines = SimulateDoFile.readlines()SimulateDoFile.close()SimulateDoFile = open(SimDirPath + ‘xxxxxxxx_simulate.do’, ‘w’)for EachLine in SimulateDoFileAllLines: if EachLine.find(‘run 1000ns’) == -1 and EachLine.find(‘quit -force’) == -1: SimulateDoFile.writelines(EachLine)SimulateDoFile.writelines(‘

log -r 。/*

’)SimulateDoFile.close()

# 刪除simulate.bat腳本中的-c選項內(nèi)容SimulateBatFile = open(SimDirPath + SimulateBatName, ‘r’)SimulateBatFileAllLines = SimulateBatFile.readlines()SimulateBatFile.close()SimulateBatFile = open(SimDirPath + SimulateBatName, ‘w’)for EachLine in SimulateBatFileAllLines: if EachLine.find(‘%bin_path%/vsim -c -do’) != -1: EachLine = EachLine.replace(‘%bin_path%/vsim -c -do’, ‘%bin_path%/vsim -do’) SimulateBatFile.writelines(EachLine)SimulateBatFile.close()

# 將當(dāng)前目錄下信號文件wave.do中的內(nèi)容覆寫到仿真目錄下的xxxxxxxx_wave.do文件中SimWaveDoFile = open(‘wave.do’, ‘r’)SimWaveDoFileAllLines = SimWaveDoFile.readlines()SimWaveDoFile.close()SimWaveDoFile = open(SimDirPath + ‘xxxxxxxx_wave.do’, ‘w’)SimWaveDoFile.writelines(SimWaveDoFileAllLines)SimWaveDoFile.close()

# 執(zhí)行Simulate腳本os.system(‘cd ’ + SimDirPath + ‘ && ’ + ‘call ’ + SimulateBatName)

上述代碼中涉及到的信號文件wave.do依舊是之前第1.3節(jié)測試仿真選項時使用的文件,將其放置在腳本所在的目錄下,然后使用Python3運行腳本,運行結(jié)果截圖如下:

可以看到成功實現(xiàn)了對仿真軟件的調(diào)用以及波形的自動添加,而且在使用時也不需要打開Vivado工程的GUI界面。2.4 實現(xiàn)總結(jié)與展望上述代碼功能的具體實現(xiàn)主要分以下幾個步驟:

使用Python系統(tǒng)函數(shù)調(diào)用Vivado的batch mode對當(dāng)前工程執(zhí)行sim.tcl腳本中的launch_simulation -mode behavioral -scripts_only命令,生成功能仿真的相關(guān)腳本;

使用Python系統(tǒng)函數(shù)在仿真目錄下依次執(zhí)行生成的compile.bat和elaborate.bat腳本,實現(xiàn)對仿真代碼文件的編譯和后續(xù)的全局優(yōu)化;

讀取生成的xxxxxxxx_simulate.do腳本文件內(nèi)容,刪除其中的run 1000ns和quit -force,并添加上log -r 。/*后重新覆寫xxxxxxxx_simulate.do腳本;

讀取生成的simulate.bat腳本文件內(nèi)容,刪除其中vsim命令后的-c選項后,重新覆寫simulate.bat腳本;

讀取Python腳本所在目錄下wave.do文件的內(nèi)容,覆寫到仿真目錄下xxxxxxxx_wave.do腳本文件中,實現(xiàn)在仿真時對自定義信號的添加;

使用Python的系統(tǒng)函數(shù)在仿真目錄下執(zhí)行simulate.bat腳本,調(diào)出仿真程序界面。

至此,我們就用總計約60行不到的Python代碼外加1行的Tcl代碼實現(xiàn)了最初設(shè)想的目標(biāo)。但是,這樣的腳本還存在著許多粗糙的缺陷或有待發(fā)展之處:

代碼各種變量如工程文件路徑、軟件版本路徑、仿真目錄路徑等的賦值都是固定賦值,那么在將腳本遷移到另一個工程下使用時,就需要根據(jù)版本和工程目錄名等環(huán)境自行去修改腳本,無法做到傻瓜式操作;

代碼從調(diào)用Vivado的batch mode生成仿真腳本,再到compile、elaborate,最后到simulate,總共的耗時較長,對于簡單的修改代碼后進(jìn)行仿真,不涉及到代碼文件添加或IP核添加時,是不需要重新生成仿真腳本的,直接從compile開始就行;而對于無代碼修改的情況,直接執(zhí)行simulate腳本進(jìn)行最后一步即可,就更不需要前面這些花費時間較長的步驟;

除去仿真功能外,我們平時進(jìn)行Vivado開發(fā)時,還存在許多本可以用腳本自動化實現(xiàn)的繁瑣操作,這些均可以整合進(jìn)一個或一組腳本中。

優(yōu)化功能的Python實現(xiàn)第二章最后總結(jié)給出了初始腳本的缺陷和有待發(fā)展之處,其中第二項缺陷可以通過提供多種條件選項的方式,實現(xiàn)多種仿真步驟,解決較為簡單。本章將主要針對第二章總結(jié)的第一項缺陷進(jìn)行分析,并加以解決。

3.1 優(yōu)化功能分析

我們期望將腳本拷貝到另一版工程時,可以不經(jīng)修改直接運行,這就要求腳本可以自動提取到其運行所需的一系列參數(shù),從而直接對環(huán)境進(jìn)行匹配。首先讓我們總結(jié)一下初步功能的Python實現(xiàn)中的具體缺陷,有哪些地方在遷移到另一工程后需要修改。

3.1.1 參數(shù)分析

這里以流水賬的形式,對初步功能的Python代碼中用到的全部參數(shù)進(jìn)行羅列和分析:

3.1.1.1 指定的工程xpr文件路徑

# 指定工程xpr文件路徑XprFilePath = ‘xxxxxxxx.xpr’

該參數(shù)的作用是能夠讓Vivado軟件針對當(dāng)前指定的工程實現(xiàn)具體功能,每當(dāng)腳本拷貝到另一個不同的工程時,該參數(shù)基本肯定會改變,所以最好能進(jìn)行自動識別。每個工程在其工程目錄下默認(rèn)都只有一個xpr文件,而Python也提供了返回指定系統(tǒng)目錄下文件名列表的函數(shù)os.listdir,可以很方便的實現(xiàn)對特定文件名稱的獲取,只需對文件名進(jìn)行判別是否是xpr文件即可實現(xiàn)自動識別。

3.1.1.2 指定的Tcl腳本路徑

# 指定Tcl腳本路徑SimTclFilePath = ‘sim.tcl’

由于指定Tcl腳本是跟隨Python腳本一起的,與實際仿真哪個工程無關(guān),名稱和位置都固定,因此這里可以繼續(xù)使用固定賦值。

3.1.1.3 執(zhí)行的系統(tǒng)命令

# 命令-在使用命令行調(diào)用Vivado軟件前需要運行的批處理文件SourceSettingsFileCmd = ‘call C:/Xilinx/Vivado/2017.2/settings64.bat’ # 命令-調(diào)用Vivado軟件的batch mode打開當(dāng)前工程文件并執(zhí)行Tcl腳本中的生成仿真腳本命令VivadoBatchModeScriptsCmd = ‘vivado -mode batch -source ’ + SimTclFilePath + ‘ -nojournal -nolog ’ + XprFilePath

可以將執(zhí)行的系統(tǒng)命令中新用到的路徑分解為以下幾部分:

系統(tǒng)執(zhí)行腳本命令:call

Xilinx軟件的安裝目錄:C:/

Vivado工程的版本:2017.2

需要調(diào)用的settings腳本名稱:settings64.bat

第二個生成仿真腳本命令VivadoBatchModeScriptsCmd涉及到的Tcl腳本路徑和工程xpr文件路徑已經(jīng)說過。此處暫時只考慮Windows系統(tǒng)實現(xiàn),因此上述分解部分中可以考慮自動識別的是:安裝目錄C:/和工程版本2017.2其中安裝目錄在同一個系統(tǒng)中都是固定的,不需要頻繁修改,所以此處僅需要讀取xpr工程文件內(nèi)容,實現(xiàn)版本的自動識別。

3.1.1.4 仿真目錄路徑(Vivado 2017.2)

# 仿真目錄路徑SimDirPath = ‘xxxxxxxx.sim/sim_1/behav/’

對上述路徑進(jìn)行分解得:

工程名:xxxxxxxx

仿真集名稱:sim_1

仿真腳本所在目錄(2017.2版本):behav

同樣由于工程名與xpr工程文件名默認(rèn)相同,并且在工程目錄下默認(rèn)只有一個后綴名為.sim的目錄,因此同樣可以很容易的實現(xiàn)對該目錄名的識別;對于仿真集名稱,由于同一版工程中可以設(shè)置多個不同的仿真集,但在xpr文件內(nèi)容中對當(dāng)前有效的仿真集有專門的參數(shù)表示,因此可以通過解析xpr文件內(nèi)容的形式識別出當(dāng)前仿真集名稱;值得注意的是:不同版本的VIvado在仿真子目錄的路徑上存在一些差別,例如2017.2的仿真腳本全部生成在behav目錄下,但2018.2版本則在behav目錄下還有針對每個仿真器的子目錄,目錄名為小寫的仿真器名稱,所以我們還需要讀取xpr文件內(nèi)容,識別出當(dāng)前設(shè)置的目標(biāo)仿真器,才能最終實現(xiàn)對仿真目錄的正確組合。

3.1.1.5 批處理腳本名稱

# compile批處理腳本名稱CompileBatName = ‘compile.bat’# elaborate批處理腳本名稱ElaborateBatName = ‘elaborate.bat’# simulate批處理腳本名稱SimulateBatName = ‘simulate.bat’

在同一類型的系統(tǒng)下,Vivado軟件默認(rèn)生成的仿真相關(guān)批處理腳本的名稱均為固定,因此此處無需修改。

3.1.1.6 總結(jié)

在初步功能代碼實現(xiàn)的基礎(chǔ)上,我們至少要對如下參數(shù)實現(xiàn)自動識別:

工程xpr文件路徑(主要是工程名)

工程文件版本

工程有效仿真集名稱

工程當(dāng)前仿真器名稱

3.1.2 xpr文件解析

3.1.2.1 xpr文件結(jié)構(gòu)介紹xpr文件是包含了Vivado工程核心配置內(nèi)容的文本文件,采用的是xml的內(nèi)容格式,下面給出一個xpr文件結(jié)構(gòu)示例:

《?xml version=“1.0” encoding=“UTF-8”?》《!-- Product Version: Vivado v2017.2 (64-bit) --》《!-- --》《!-- Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. --》

《Project 。。.。。.。。.。。.。》 《Configuration 》 。。.。。.。。.。。.。 《/Configuration》 《FileSets 》 。。.。。.。。.。。.。 《/FileSets》 《Simulators 》 。。.。。.。。.。。.。 《/Simulators》 《Runs 》 。。.。。.。。.。。.。 《/Runs》《/Project》

可以看到整個xpr文件內(nèi)容基本全部包含在一個根節(jié)點Project內(nèi),根節(jié)點內(nèi)部又包含四個子節(jié)點Configuration、FileSets、Simulators、Runs。經(jīng)過對實際的工程xpr文件內(nèi)容進(jìn)行分析,我們可以了解到四個子節(jié)點的主要內(nèi)容為:

Configuration:Vivado工程的一系列配置參數(shù),例如:FPGA芯片型號、仿真聯(lián)調(diào)庫路徑、目標(biāo)仿真器等等;

FileSets:添加進(jìn)該工程的全部代碼、IP核或約束文件路徑,及一系列相關(guān)的文件屬性:設(shè)定的頂層模塊名稱、代碼是否用于綜合、實現(xiàn)、仿真等;

Simulators:包含對當(dāng)前類型系統(tǒng)下能夠使用的仿真器的描述等;

Runs:包含需要進(jìn)行Synthesis、Implementation的IP核文件、代碼設(shè)計的一系列參數(shù)配置。

下面我們結(jié)合上一節(jié)優(yōu)化分析的結(jié)論,對所需要的xpr文件內(nèi)容進(jìn)行進(jìn)一步的分析和查找。需要解析xpr得到的參數(shù)有:工程版本、有效仿真集名稱、當(dāng)前仿真器名稱。

3.1.2.2 工程版本

經(jīng)過一番查找,在根節(jié)點Project中并沒有發(fā)現(xiàn)跟Vivado版本相關(guān)的參數(shù),唯一與版本相關(guān)的內(nèi)容僅出現(xiàn)在內(nèi)容第二行:

《?xml version=“1.0” encoding=“UTF-8”?》《!-- Product Version: Vivado v2017.2 (64-bit) --》《!-- --》《!-- Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. --》

因此我們只能將該行Vivado v后的內(nèi)容2017.2提取為版本號使用。

3.1.2.3 有效仿真集名稱

表示當(dāng)前工程的仿真集的參數(shù)名為ActiveSimSet,在子節(jié)點Configuration中,示例內(nèi)容如下:

《Option Name=“ActiveSimSet” Val=“sim_1”/》

3.1.2.4 當(dāng)前仿真器名稱

內(nèi)容中表示當(dāng)前仿真器名稱的參數(shù)名為TargetSimulator,同樣在子節(jié)點Configuration中,示例內(nèi)容如下:

《Option Name=“TargetSimulator” Val=“Questa”/》

在具體針對xml格式文件的解析上,Python提供了一個xml函數(shù)庫,使用其中的parse函數(shù)可以對xml文本進(jìn)行簡單高效的處理。

3.2 功能實現(xiàn)思路

根據(jù)上述分析,總結(jié)優(yōu)化功能的實現(xiàn)思路如下:

利用Python的os庫函數(shù)實現(xiàn)對特定路徑下工程文件尤其是xpr文件的查找;

在查找到xpr工程文件后,讀取文件內(nèi)容獲取版本號;

使用Python的xml庫函數(shù)對查找到的xpr文件文本內(nèi)容進(jìn)行解析,提取出有效仿真集名稱和當(dāng)前仿真器名稱;

根據(jù)上述步驟獲取到的信息,組合相關(guān)參數(shù),繼續(xù)完成第二章實現(xiàn)的功能。

3.3 具體實現(xiàn)

首先利用Python的os庫中的相關(guān)函數(shù)實現(xiàn)對工程文件路徑的查找,相關(guān)代碼和注釋如下:

import os

# 獲取并返回對應(yīng)文件或目錄路徑名列表def getProjFilePathList(Path = ‘。/’, FilePartName = ‘.xpr’): # 判斷傳入?yún)?shù)是否為字符串 if type(Path) != str or type(FilePartName) != str: print(‘Error: The type of parameter is wrong! Please ensure each input parameter is a string!’) return [] # 判斷傳入的路徑參數(shù)是否存在 if os.path.isdir(Path) == False: print(‘Error: The path does not exist!’) return [] # 查找目標(biāo)文件,并將查找結(jié)果路徑記錄到FilePathList的列表中

FilePathList = [] for FileName in os.listdir(Path): if FileName.find(FilePartName) != -1: FilePathList.append(Path + FileName) # 判斷是否查找到對應(yīng)文件或目錄路徑 if len(FilePathList) == 0: print(‘Error: Can not find any file or dir whose name including “’ + FilePartName + ‘” in “’ + Path + ‘”’) return FilePathList

# 獲取并返回對應(yīng)文件或目錄路徑名列表中的第一個路徑def getProjFilePath(Path = ‘。/’, FilePartName = ‘.xpr’): # 獲取并返回對應(yīng)文件或目錄路徑名列表 FilePathList = getProjFilePathList(Path, FilePartName) # 返回列表中第一個元素 if len(FilePathList) == 0: return ‘’ else: return FilePathList[0]

然后根據(jù)查找到的xpr工程文件路徑,讀取內(nèi)容,從中提取版本號:

# 獲取并返回當(dāng)前工程版本def getProjVersion(XprFilePathName): VivadoProjVerLine = ‘’ VivadoProjVer = ‘’ VivadoProjVerLoc = -1 # 打開工程文件查找版本號所在行 XprFile = open(XprFilePathName, “r”) for string in XprFile.readlines(): if string.find(‘Product Version: Vivado v’) != -1:

VivadoProjVerLoc = string.find(‘Product Version: Vivado v’) + len(‘Product Version: Vivado v’) VivadoProjVerLine = string break XprFile.close() if VivadoProjVerLoc == -1: VivadoProjVer = ‘’ print(‘Error: Can not find the version of proj, please ensure the xpr file is ok!’)

return VivadoProjVer # 判斷查找到的版本號字符串是否合法 for CharVer in VivadoProjVerLine[VivadoProjVerLoc :]: if CharVer == ‘ ’ and VivadoProjVer != ‘’: break elif CharVer 》= ‘0’ and CharVer 《= ‘9’: VivadoProjVer = VivadoProjVer + CharVer elif CharVer == ‘。’: VivadoProjVer = VivadoProjVer + CharVer else: VivadoProjVer = ‘’ print(‘Error: Can not identify the version of this xpr file!’) return VivadoProjVer return VivadoProjVer

使用Python的xml庫函數(shù)解析xpr文件,提取出有效仿真集名稱ActiveSimSet和當(dāng)前仿真器名稱TargetSimulator:

from xml.dom.minidom import parse

# 解析xpr工程文件doc = parse(XprFilePath)root = doc.documentElement# 記錄解析出的四個節(jié)點Configuration = root.getElementsByTagName(‘Configuration’)[0]FileSets = root.getElementsByTagName(‘FileSets’)[0]Simulators = root.getElementsByTagName(‘Simulators’)[0]Runs = root.getElementsByTagName(‘Runs’)[0]# 創(chuàng)建節(jié)點

Configuration中Option的關(guān)鍵詞字典,初始化為空

ConfigurationOptionDict = {}# 創(chuàng)建并初始化節(jié)點Configuration中Option的Name關(guān)鍵詞集合

ConfigurationOptionNameSet = {‘Part’, ‘CompiledLibDir’, ‘TargetSimulator’, ‘ActiveSimSet’, ‘DefaultLib’}# 查找xpr工程文件中Configuration節(jié)點中的關(guān)鍵詞并記錄到關(guān)鍵詞字典中Options = Configuration.getElementsByTagName(‘Option’)for Option in Options:

if Option.hasAttribute(‘Name’) and Option.hasAttribute(‘Val’): for keyword in ConfigurationOptionNameSet: if Option.getAttribute(‘Name’) == keyword: ConfigurationOptionDict[keyword] = Option.getAttribute(‘Val’)

至此我們就完成了對優(yōu)化功能的實現(xiàn),與第二章的代碼進(jìn)行整合,就可以自行實現(xiàn)對不同版本不同名稱工程的自動識別,并進(jìn)行仿真。

后記

前一、二、三章主要按照時間順序,詳細(xì)介紹了使用Python腳本實現(xiàn)對仿真自動化操作功能時,一系列的學(xué)習(xí)研究過程。對整個過程中所涉及到的關(guān)鍵點都進(jìn)行了說明與分析。當(dāng)然,按照上述過程最終編寫出的腳本還是較為粗糙,實現(xiàn)的功能也很有限。在后續(xù)的學(xué)習(xí)中,筆者根據(jù)使用體驗對該腳本做了重構(gòu)和多次迭代,加入了一些新的功能,同時也拓寬了使用場景,增強了可擴展性。當(dāng)然受限于筆者的個人水平,目前為止腳本仍然很粗糙,不過已經(jīng)可以為項目中Vivado工程開發(fā)的特殊需求提供一個簡單的輔助框架,可以比較自由地添加一些簡單功能,筆者打算結(jié)合后續(xù)項目開發(fā)中遇到的問題和使用體驗,繼續(xù)對其進(jìn)行優(yōu)化,爭取讓其能成為一個比較可依賴的好助手。

原文標(biāo)題:【源碼】手把手教你用Python實現(xiàn)Vivado和ModelSim仿真自動化

文章出處:【微信公眾號:FPGA開源工作室】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

仿真

+關(guān)注

關(guān)注

51文章

4245瀏覽量

135368 -

ModelSim

+關(guān)注

關(guān)注

5文章

174瀏覽量

47953 -

python

+關(guān)注

關(guān)注

56文章

4825瀏覽量

86268 -

Vivado

+關(guān)注

關(guān)注

19文章

831瀏覽量

68307

原文標(biāo)題:【源碼】手把手教你用Python實現(xiàn)Vivado和ModelSim仿真自動化

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Ethercat轉(zhuǎn)Profinet網(wǎng)關(guān)如何用“協(xié)議翻譯術(shù)”打通自動化產(chǎn)線任督二脈

HFSS 自動化建模工具

基于 Docker 與 Jenkins 實現(xiàn)自動化部署

通用自動化測試軟件 - TAE

自動化創(chuàng)建UI并解析數(shù)據(jù)

Python環(huán)境下的代理服務(wù)器搭建與自動化管理

LMX2595EVM如何實現(xiàn)自動化控制?

使用modelsim時的問題分析

如何使用python調(diào)起UDE STK5.2進(jìn)行下載自動化下載呢?

使用TPS2116實現(xiàn)建筑自動化應(yīng)用的高能效

開關(guān)電源自動化測試設(shè)備:如何實現(xiàn)自動化測試?

如何用Python實現(xiàn)Vivado和ModelSim仿真自動化?

如何用Python實現(xiàn)Vivado和ModelSim仿真自動化?

評論