Xilinx zynq系列FPGA實現(xiàn)神經(jīng)網(wǎng)絡(luò)評估

本篇目錄

1. 內(nèi)存占用

1.1 FPGA程序中內(nèi)存的實現(xiàn)方式

1.2 Zynq的BRAM內(nèi)存大小

1.3 一個卷積操作占用的內(nèi)存

2. PipeCNN可實現(xiàn)性

PipeCNN論文解析:用OpenCL實現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速

2.1 已實現(xiàn)的PipeCNN資源消耗

3. 實現(xiàn)大型神經(jīng)網(wǎng)絡(luò)的方法

4. Virtex-7高端FPGA概覽、7系列FPGA相關(guān)文檔

正文

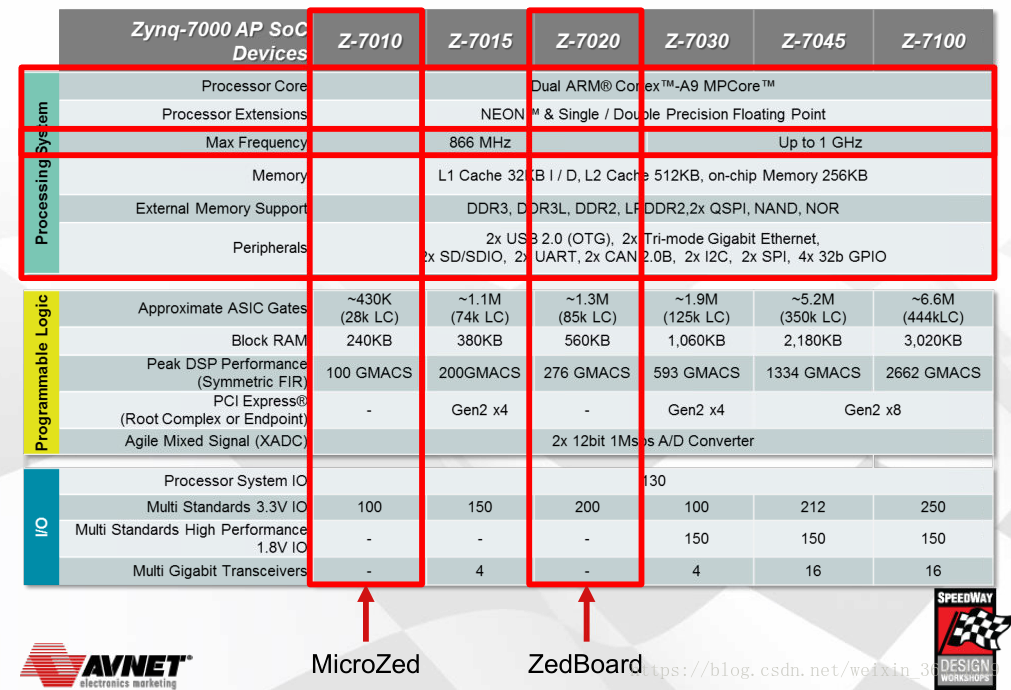

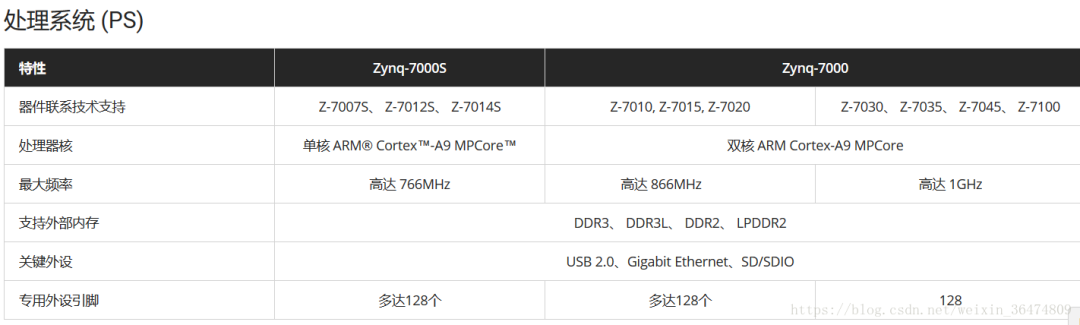

0Zynq7000系列概覽

1內(nèi)存占用

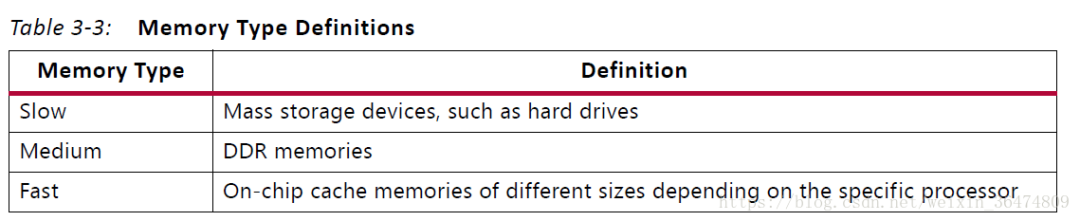

1.1 FPGA程序中內(nèi)存的實現(xiàn)方式

參閱xilinx文檔UG998

FPGA并沒有像軟件那樣用已有的cache,F(xiàn)PGA的HLS編譯器會在FPGA中創(chuàng)建一個快速的memory architecture以最好的適應(yīng)算法中的數(shù)據(jù)樣式(data layout)。因此FPGA可以有相互獨立的不同大小的內(nèi)部存儲空間,例如寄存器,移位寄存器,F(xiàn)IFOs和BRAMs。

寄存器:最快的內(nèi)存結(jié)構(gòu),集成在在運算單元之中,獲取不需要額外的時延。

移位寄存器:可以被當(dāng)作一個數(shù)據(jù)序列,每一個數(shù)據(jù)可以在不同的運算之中被重復(fù)使用。將其中所有數(shù)據(jù)移動到相鄰的存儲設(shè)備中只需要一個時鐘周期。

FIFO:只有一個輸入和輸出的數(shù)據(jù)序列,通常被用于循環(huán)或循環(huán)函數(shù),細(xì)節(jié)會被HLS編譯器處理。

BRAM:集成在FPGA fabric模塊中的RAM,每個xilinx的FPGA中集成有多個這樣的BRAM。可以被當(dāng)作有以下特性的cache:1.不支持像處理器cache中那樣的緩存一致性(cache coherency,collision),不支持處理器中的一些邏輯類型。2.只在設(shè)備有電時保持內(nèi)存。3.不同的BRAM塊可以同時傳輸數(shù)據(jù)。

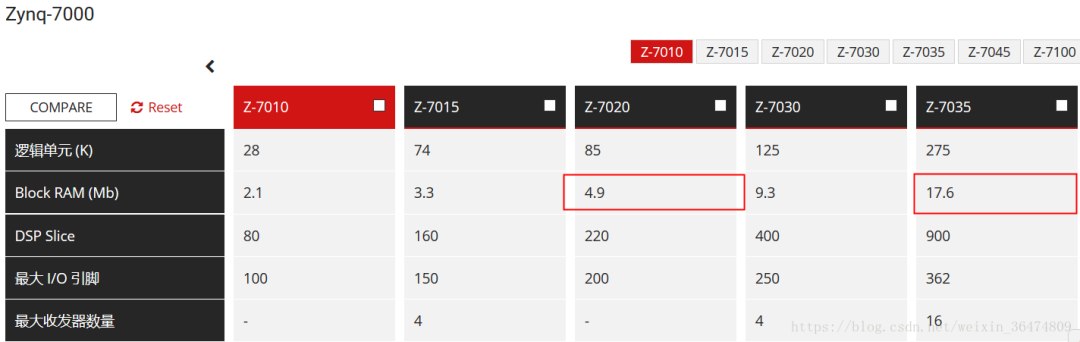

1.2 Zynq的BRAM內(nèi)存大小

zynq 7z020的BRAM為4.9Mb,7z035的BRAM為17.6Mb(2.2MB)

1.3 一個卷積操作占用的內(nèi)存

例如,我們實現(xiàn)的卷積函數(shù),輸入27×600,卷積核16×27,輸出16×600,數(shù)據(jù)類型為float。

//convolution operation for (i = 0; i 《 16; i++) { for (j = 0; j 《 600; j++) { result = 0; for (k = 0; k 《 27; k++) { temp = weights[i*27+k] * buf_in[k*600+j]; result += temp; } buf_out[i*600+j] = result; } }

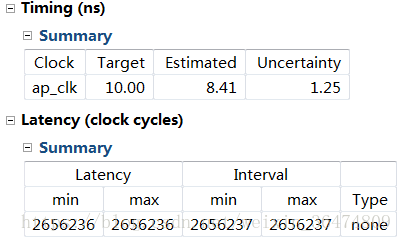

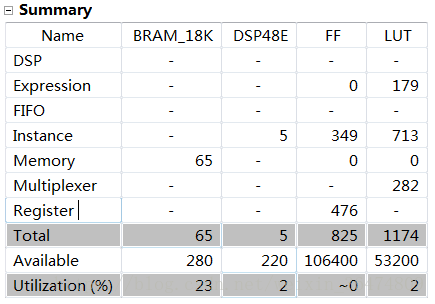

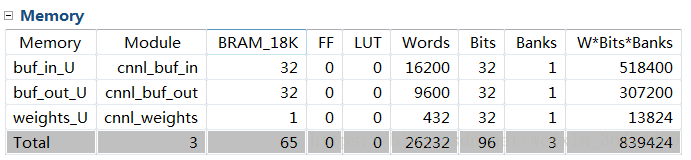

在HLS中生成的IPcore占用硬件資源為:

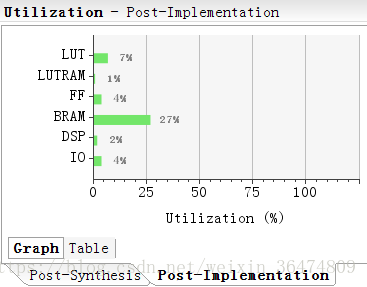

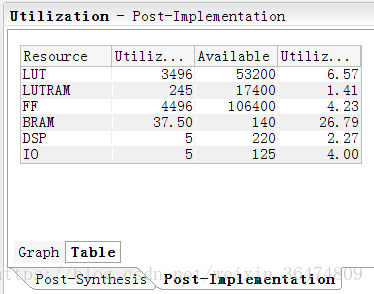

在vivado中搭建好系統(tǒng),占用的資源為:

2PipeCNN可實現(xiàn)性

PipeCNN是一個基于OpenCL的FPGA實現(xiàn)大型卷積網(wǎng)絡(luò)的加速器。

PipeCNN解析文檔:

PipeCNN論文解析:用OpenCL實現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速

github地址:https://github.com/doonny/PipeCNN#how-to-use

2.1 已實現(xiàn)的PipeCNN資源消耗

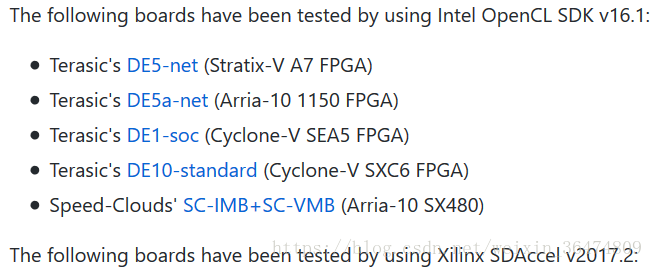

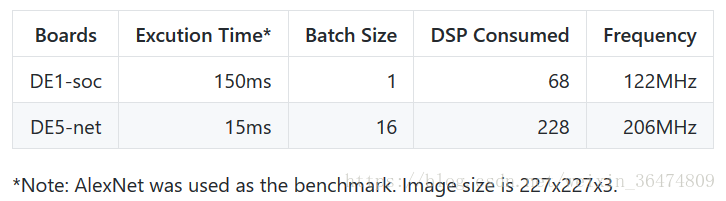

對于Altera FPGA,運用 Intel‘s OpenCL SDK v16.1 toolset.

對于Xilinx FPGAs, the SDAccel development environment v2017.2 can be used.

Xilinx’s KCU1500 (XCKU115 FPGA)(已經(jīng)有xilin的板子實現(xiàn)過pipeCNN,但是型號比zynq高很多)

硬件資源可以被三個宏調(diào)控,device/hw_param.cl. Change the following macros

VEC_SIZE

LANE_NUM

CONV_GP_SIZE_X

消耗資源為:

3實現(xiàn)大型神經(jīng)網(wǎng)絡(luò)的方法

方案一:壓縮模型到《2.2MB,可實現(xiàn)在BRAM中

優(yōu)點:1.速度快 2.實現(xiàn)方便

缺點:1.模型壓縮難度 2.難以實現(xiàn)大型網(wǎng)絡(luò)

方案二:用FPGA調(diào)用DDR

優(yōu)點:1.速度中等 2.可實現(xiàn)大型網(wǎng)絡(luò)

缺點:調(diào)用DDR有難度,開發(fā)周期長

方案三:用片上單片機調(diào)用DDR(插入SD卡)分包傳入IPcore運算

優(yōu)點:可實現(xiàn)大型網(wǎng)絡(luò)

缺點:速度較慢

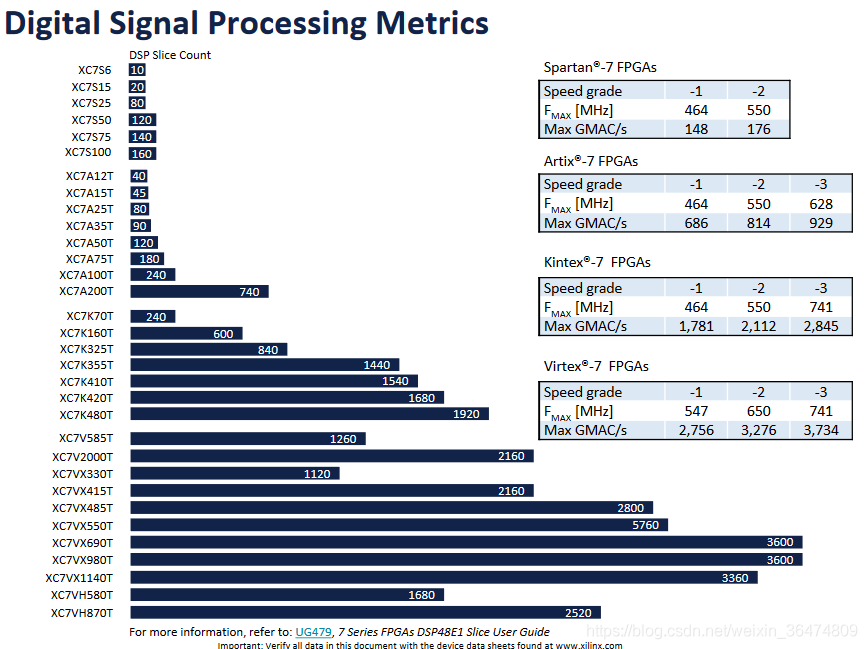

4Virtex-7高端FPGA概覽

Virtex-7為高端FPGA,比Zynq高了一個檔次。

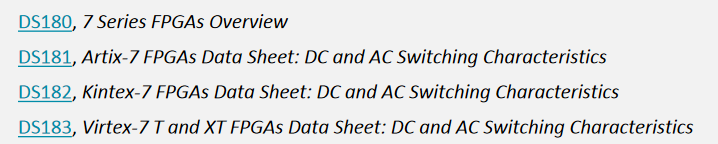

7系列FPGA相關(guān)文檔:

原文標(biāo)題:Xilinx Zynq系列FPGA實現(xiàn)神經(jīng)網(wǎng)絡(luò)中相關(guān)資源評估

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1646文章

22069瀏覽量

619674 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4814瀏覽量

104042

原文標(biāo)題:Xilinx Zynq系列FPGA實現(xiàn)神經(jīng)網(wǎng)絡(luò)中相關(guān)資源評估

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于FPGA的壓縮算法加速實現(xiàn)

如何使用MATLAB實現(xiàn)一維時間卷積網(wǎng)絡(luò)

BP神經(jīng)網(wǎng)絡(luò)與卷積神經(jīng)網(wǎng)絡(luò)的比較

FPGA圖像處理基礎(chǔ)----實現(xiàn)緩存卷積窗口

如何用OpenCL實現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速?

如何用OpenCL實現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速?

評論