項目簡述

本次項目我們主要是為了講解DDS,所以我們使用了混頻這個小項目來講解。DDS自己手寫是比較簡單且靈活,但是Xilinx給我們提供了相應的IP核,那么這次我們將直接講解使用IP來產生不同頻率的正弦波。這篇博客我們也首次引入了Xilinx中block design的設計方法,由于AXI4總線的出現,我們使用block design的設計概念特別簡單。本次的項目主要是:利用兩個DDS產生兩個不同頻率的正弦波,然后進行***相乘***混頻,利用Modelsim進行仿真驗證我們實驗的正確性。本次實驗所用到的軟硬件環境為:

1、VIVADO 2019.1軟件環境

2、Modelsim仿真環境

DDS IP的定制及講解

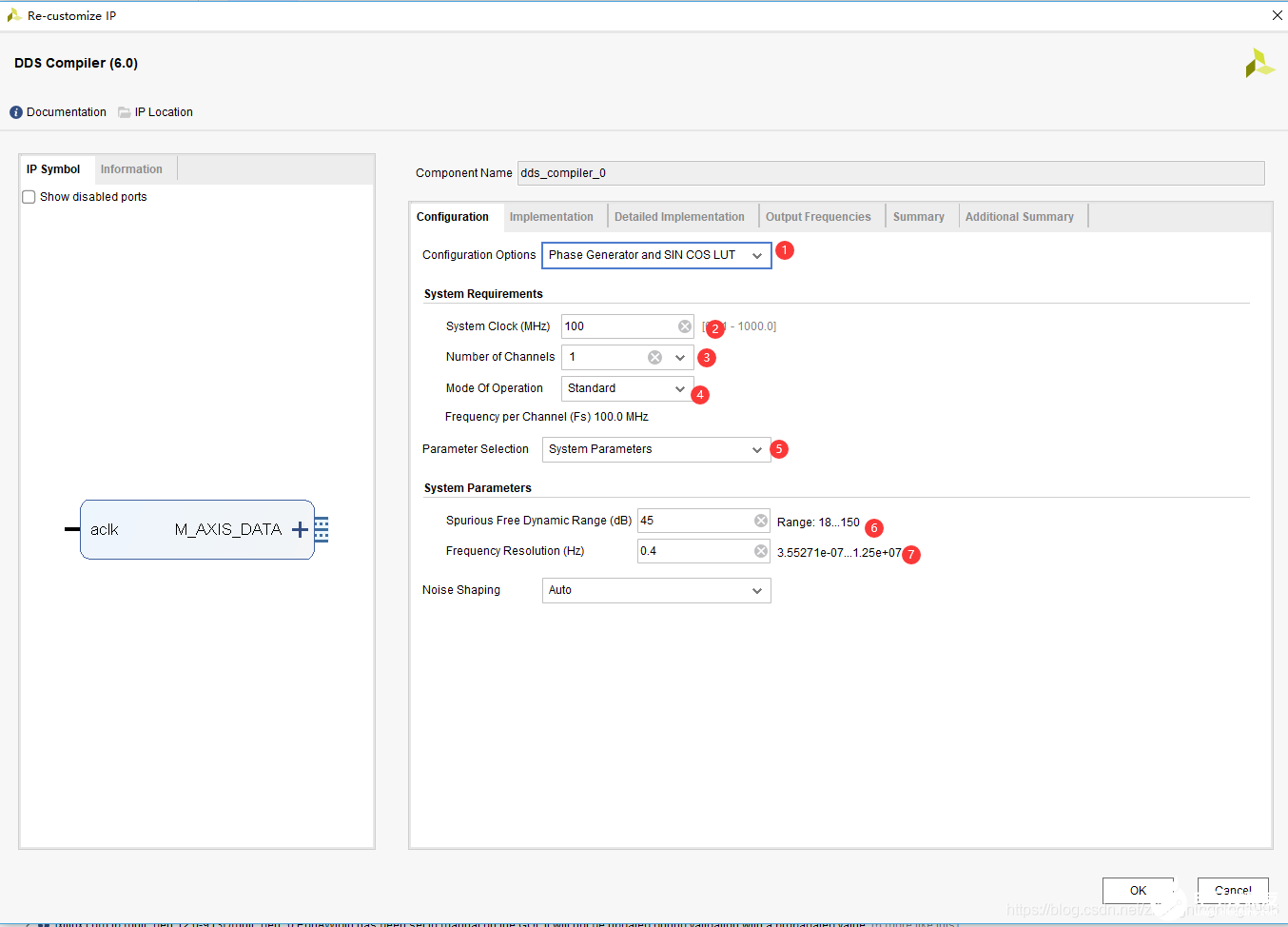

1、我們選擇波形與相位同時存在的情況。

2、選擇DDS IP輸入的系統時鐘頻率,這里我們選擇100MHz。

3、DDS通道的數目,我們這里選擇一個。

4、整個IP配置的模式,我們這里選擇標準模式即可。

5、參數選擇的模式,我們這里選擇系統參數,這個選擇主要影響IP的定制界面所涉及到的參數。

6、頻率的動態范圍,主要和DDS內部RAM的數據位寬有關,計算方法是20log2n,其中n為RAM的位寬。

7、選擇DDS的最小的頻率分辨率。

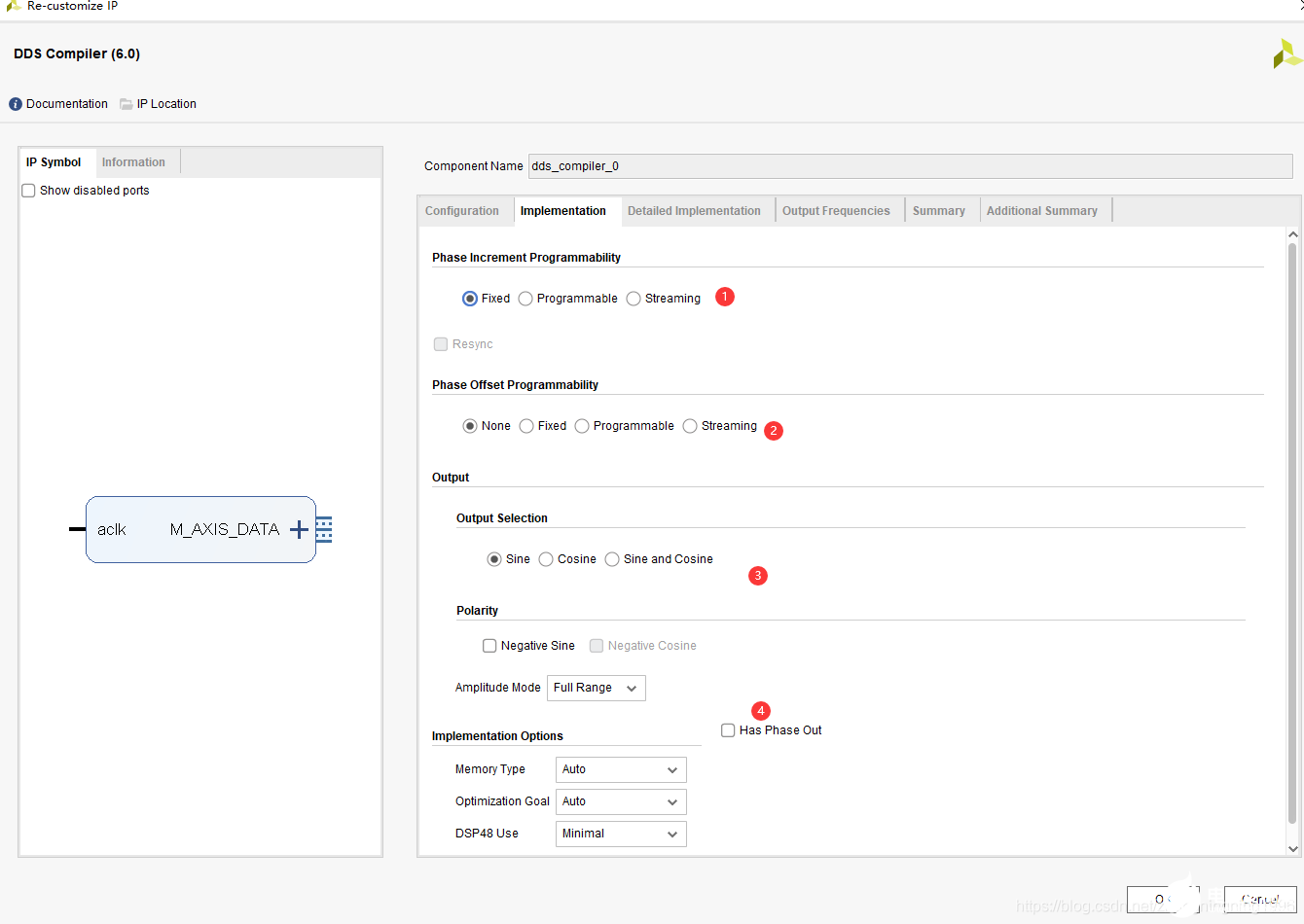

1、相位增量我們選擇固定

2、相位偏執我們也選擇成固定,這兩個參數可以動態控制輸出的頻率。

3、我們這里產生正弦波

4、因為我們只考慮正弦波的頻率,座椅這里不再輸出相位信息

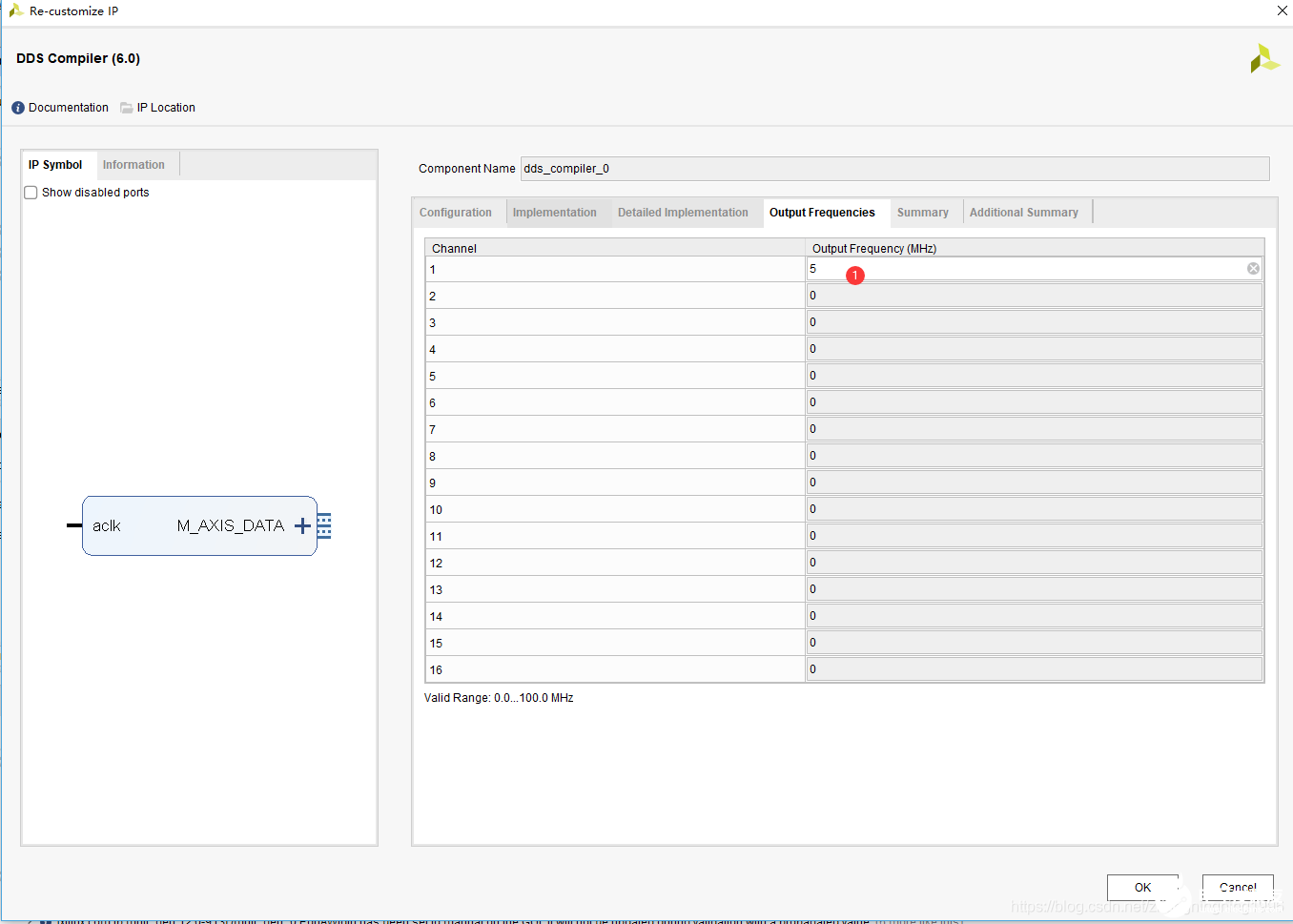

1、輸入我們需要DDS輸出的頻率,這里我們輸入5MHz。

其余選項,我們選擇默認即可。這樣,我們便定制了一個完整的DDS IP核,接下來的博客我們會自己手寫相應的DDS的功能,感興趣的同學可以保持關注。

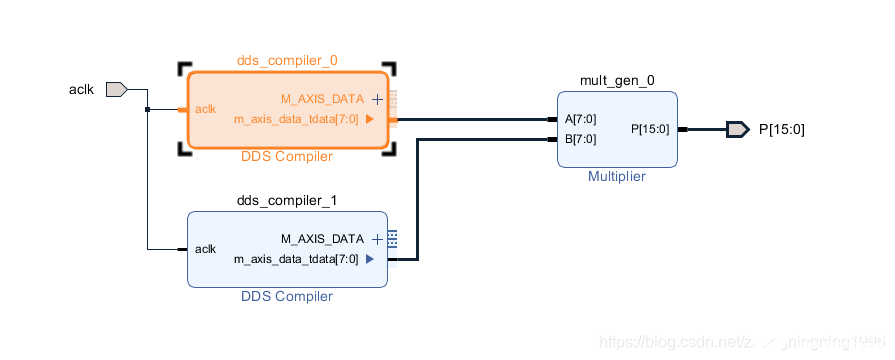

Block Design涉及

我們這邊博客首次引入了block design的設計方法,但是這個設計方法特別重要,希望同學們可以好好學習。進行block design的連線圖如下:

然后驗證設計的有效性,產生輸出工程,生成相應的top文件,供我們接下來的設計使用。

測試文件代碼

這里我們為了驗證我們實驗的正確性,給出相應的測試模塊。

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2020/04/03 22:39:17 // Design Name: // Module Name: tb // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module tb; wire [15:0] P ; reg aclk ; initial begin aclk = 1‘b0; end always #5 aclk = ~aclk; system_wrapper system_wrapper_inst( .P (P ), .aclk (aclk ) ); endmodule

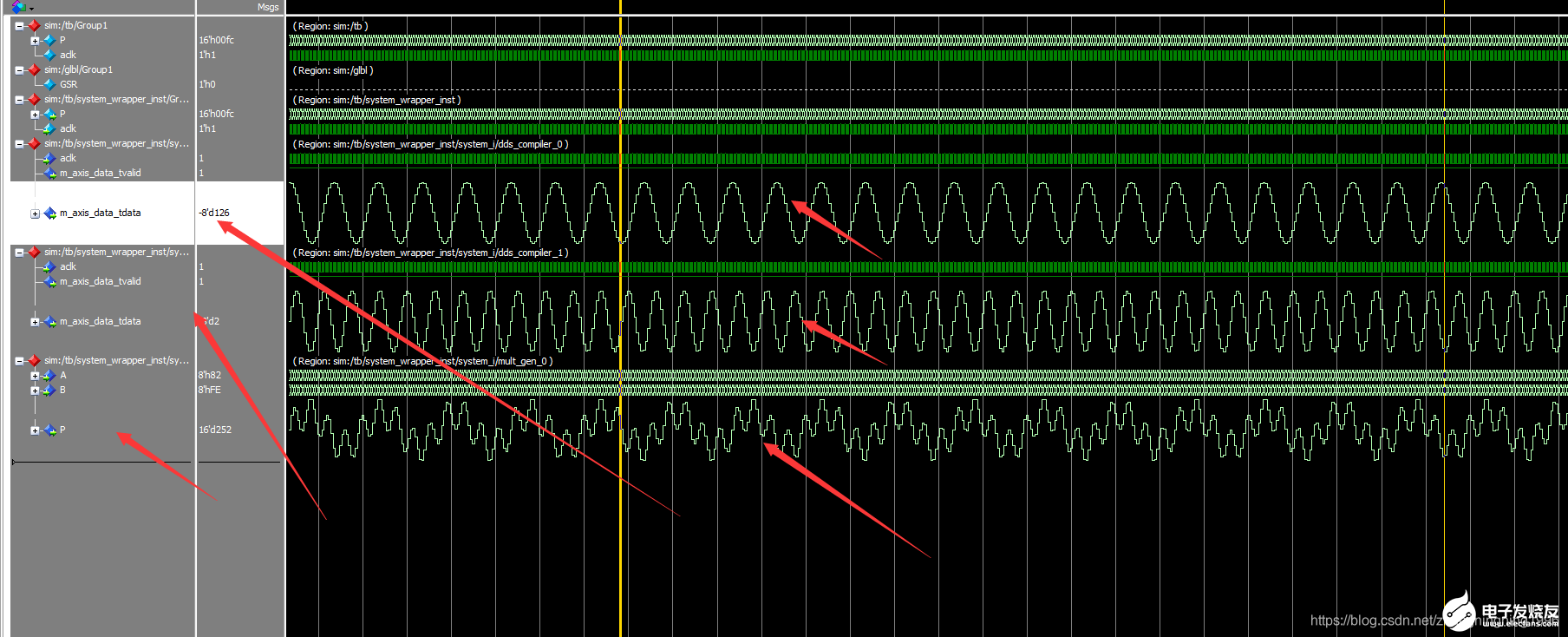

仿真結果

我們進行Modelsim仿真測試的結果如下:

從上面的仿真波形可以驗證我們實驗的準確性。

編輯:lyn

-

Xilinx

+關注

關注

73文章

2183瀏覽量

124472 -

IP

+關注

關注

5文章

1789瀏覽量

151510 -

DDS

+關注

關注

22文章

671瀏覽量

154106

發布評論請先 登錄

服務與數據的雙螺旋:從SOME/IP到DDS看汽車電子架構的進化之路

Xilinx Shift RAM IP概述和主要功能

詳解Xilinx的10G PCS PMA IP

Vivado FIR IP核實現

DDS傳遞簇與大型數組的教程

如何理解芯片設計中的IP

Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明

Xilinx DDS IP核的使用和參數配置

DDS通信中間件——DCPS規范(上)

關于Xilinx中DDS IP的運用與講解

關于Xilinx中DDS IP的運用與講解

評論