設計之前先了解基本知識和工作原理

概述:SPI(Serial Perripheral Interface),中文是串行外圍設備接口,由Motorola 公司開發并推出的一種串行通訊接口,一般主要應用在MCU和外圍設備之間的通訊,廣泛應用在Flash,模數轉換器,通訊模塊等外圍芯片或者模塊與MCU之間的通訊。

特點:高速(1.受限于最大時鐘頻率2.受限于CPU處理SPI數據的能力;3受限于PCB走線);

全雙工(兩個數據線可以同時收發);

主從模式(既可當主機又可當從機工作);

提供頻率可編程時鐘;

接口:SCK: Serial Clock,作用是主設備往從設備傳輸時鐘信號,控制數據交換及速率;

SS/CS:Slave Select/Chip Select,用于主設備片選從設備,由主設備控制;

SDO/MOSI:Serial Data Output/Master Out Slave In,作用是SPI設備發送數據;

SDI/MISO: Serial Data Input/Master In Slave Out,作用是SPI設備接收數據;

工作模式:有四種工作模式,工作模式是根據CPOL和CPHA邏輯配置而定的。

SPI主模塊和與之通信的外設備時鐘相位和極性應該一致。

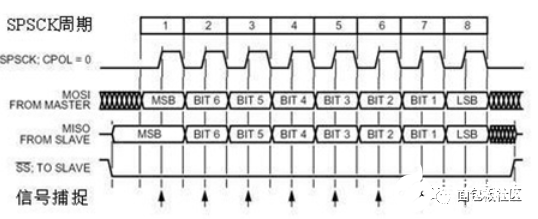

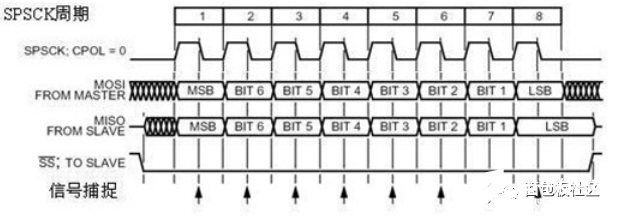

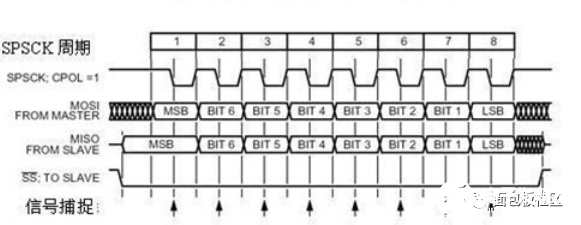

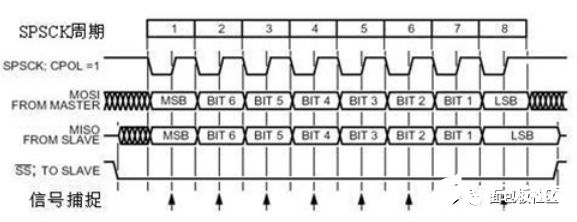

時鐘極性CPOL(Clock POLarity):配置為0時SPI總線空閑為低電平,配置為1時SPI

總線空閑為高電平;

時鐘相位CPHA(Clock PHAse):配置為0時在SCK第一個跳變沿采樣(上升或下降),

配置為1時在SCK第二個跳變沿采樣(上升或下降);

工作模式0:當CPHA=0、CPOL=0時

工作模式1:當CPHA=1、CPOL=0時

工作模式2:當CPHA=0、CPOL=1時

工作模式3:當CPHA=1、CPOL=1時

硬件電路設計

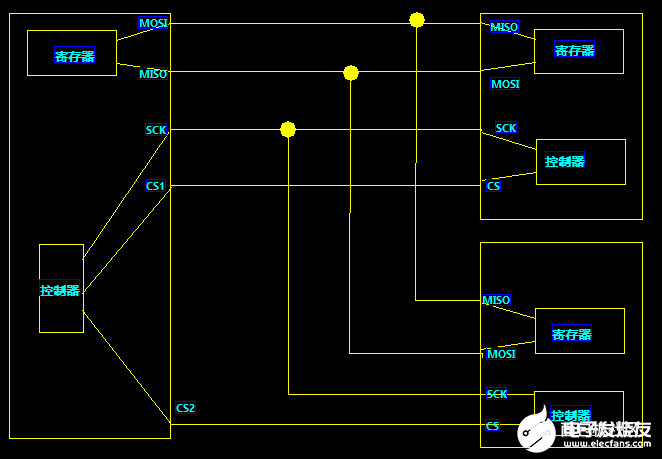

系統物理連接:SCK—SCK SDO/MOSI—SDI/MISO SS/CS—SS/CS

實際電路設計:

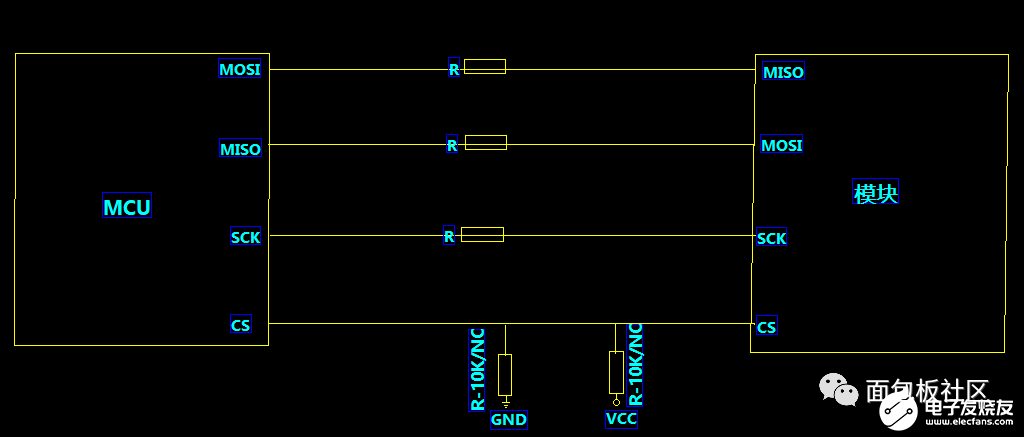

1.信號線和時鐘線串電阻:終端阻抗匹配:高速信號一般在電路的終端串接小電阻用于阻抗的匹配,TTL

信號阻抗約13,串接33Ω即可,防信號完整性問題;

過ESD測試:用于過ESD測試;

接口防護:當信號線連接外部接口時,在接插件拔插瞬間可能會有高壓,串接電阻可保護IO;

2. 片選信號:是否要接上拉電阻或者下拉電阻,看具體規格書要求;

3. 線能粗則粗,能短則短。減小線路寄生電容,電感(走線長度小于波長的20分之一,最長不要超過75cm;

4. 可以走弧形線就走弧形線;

5. 嚴格用地包絡屏蔽;

6. 如果要求嚴格的話,可以把時鐘線和數據線分開;

信號測試:

1.高低電平值;

2.最大和最新的過沖;

3.正回沖和負回沖;

編輯:lyn

-

接口

+關注

關注

33文章

8997瀏覽量

153695 -

SPI

+關注

關注

17文章

1804瀏覽量

95881 -

硬件電路設計

+關注

關注

4文章

33瀏覽量

21721

發布評論請先 登錄

IGBT驅動與保護電路設計及 應用電路實例

硬件設備的開機密鑰:電路設計深度解析

跟著華為學硬件電路設計,華為全套硬件電路設計學習資料都在這里了!

直流電機基本知識彩色PDF來啦

《典型電子電路設計與測試》閱讀體驗

硬件電路設計的思路介紹

輔助電源的工作原理

自舉電路的工作原理 自舉電路的作用是什么

退耦電路工作原理是什么

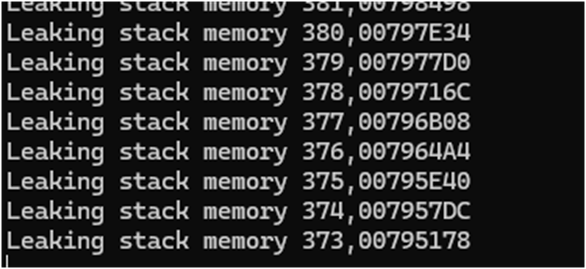

堆棧和內存的基本知識

關于SPI基本知識和工作原理及硬件電路設計淺析

關于SPI基本知識和工作原理及硬件電路設計淺析

評論