引言

軟件無線電是一種基于寬帶A/D、高速DSP芯片、以軟件為核心的嶄新體系結(jié)構(gòu)。其基本思想是將寬帶A/D盡可能靠近射頻天線,以便將接收到的模擬信號(hào)盡可能早地?cái)?shù)字化,盡量通過軟件來實(shí)現(xiàn)接收機(jī)的各種功能。通過運(yùn)行不同的算法,實(shí)時(shí)地配置信號(hào),以提供多模式、多頻段的功能。與傳統(tǒng)的模擬方式相比,軟件無線電具有靈活性、適應(yīng)性和開放性等特點(diǎn),被譽(yù)為無線電領(lǐng)域的又一次革命。目前軟件無線電技術(shù)已在通信系統(tǒng)中得到廣泛應(yīng)用。

全數(shù)字化接收機(jī)是軟件無線電中的一個(gè)重要基礎(chǔ),其硬件平臺(tái)可以用可編程的通用DSP或者可重構(gòu)的專用DSP來實(shí)現(xiàn)。目前,由于硬件水平的限制,直接射頻數(shù)字化還有一定困難。一般是先模擬下變頻至合適的中頻,在中頻直接數(shù)字化,然后經(jīng)數(shù)字下變頻至基帶。模擬下變頻完成初步的頻率選擇,中頻采樣后經(jīng)數(shù)字下變頻完成第二次頻率變換。其中,數(shù)字下變頻的設(shè)計(jì)是關(guān)鍵技術(shù),它的實(shí)現(xiàn)方式有兩種,一種是在FPGA內(nèi)設(shè)計(jì)實(shí)現(xiàn),另一種是采用專用的數(shù)字下變頻芯片來實(shí)現(xiàn)。本文將對(duì)INTERSIL公司生產(chǎn)的四通道數(shù)字下變頻器ISL5216的功能特點(diǎn)進(jìn)行詳細(xì)介紹,并結(jié)合自行研制的中頻通用接收平臺(tái),重點(diǎn)介紹利用其實(shí)現(xiàn)數(shù)字信號(hào)的抽取濾波以降低信號(hào)速率的設(shè)計(jì)要點(diǎn),并給出了設(shè)計(jì)實(shí)例。

1 ISL5216簡介

1.1 ISL5216的功能特點(diǎn)

ISL5216是INTERSIL公司生產(chǎn)的可編程四通道數(shù)字下變頻器(PDC),它的基本功能是從輸入的寬帶信號(hào)中提取窄帶信號(hào),并將其下變頻為數(shù)字基帶信號(hào),以便后續(xù)DSP處理。

該芯片的主要特點(diǎn)如下:

一 輸入信號(hào)速率達(dá)95MSPS;

一 具有四個(gè)獨(dú)立可編程的下變頻器通道;

一 具有四個(gè)16-bit定點(diǎn)或17-bit浮點(diǎn)模式的并行輸入通道;

一 帶有32-bit可編程載頻數(shù)控振蕩器(NCO),無雜散動(dòng)態(tài)范圍(SFDR)大于115dB;

一 具有110dB的帶外衰減;

一 抽取因子范圍為4~65 536;

一 含有24-bit內(nèi)部數(shù)據(jù)通道;

一 內(nèi)含增益容限可達(dá)96dB的數(shù)字AGC;

一 具有多種濾波器功能(其中包括:1到5級(jí)CIC濾波器、半帶抽取與插入FIR濾波器、可編程FIR濾波器和重采樣FIR濾波器);

一 可通過串聯(lián)濾波獲得附加帶寬;

一 具有四個(gè)獨(dú)立的串行輸出通道;

一 采用2.5V內(nèi)核電壓、3.3V外圍電壓工作。

1.2 ISL5216的內(nèi)部結(jié)構(gòu)及工作機(jī)理

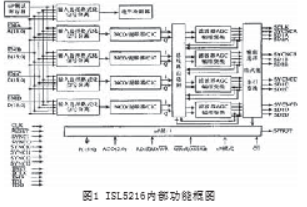

ISL5216具有很大的動(dòng)態(tài)范圍和靈活性。在四個(gè)通道中,每一個(gè)通道都是由前端的載頻數(shù)控振蕩器(NCO)、數(shù)字混頻器和級(jí)聯(lián)積分梳狀濾波器CIC以及后端的FIR濾波器、AGC和直角坐標(biāo)到極坐標(biāo)轉(zhuǎn)換器構(gòu)成。四個(gè)通道中的每個(gè)通道的參數(shù)都可以獨(dú)立通過微處理器進(jìn)行編程。圖1是ISL5216的內(nèi)部功能框圖。A(15∶0)、B(15∶0)、C(15∶0)和D(15∶0)分別為四條并行的數(shù)據(jù)輸入總線。SDXA、SDXB、SDXC和SDXD為四對(duì)串行數(shù)據(jù)輸出線。每一個(gè)輸入都可以連接到任意一個(gè)或所有的內(nèi)部信號(hào)處理通道中去,每一個(gè)通道的輸出都可以接到任何一個(gè)串行輸出端。如果多路通道是同步的,那么這些通道可以復(fù)用到一個(gè)共同的輸出端。四個(gè)通道共用同一個(gè)輸入時(shí)鐘和同一個(gè)串行輸出時(shí)鐘。但是輸出信號(hào)速率既可以是同步的也可以是異步的。位于前端和后端之間的總線多路轉(zhuǎn)換器可以為后端串聯(lián)的濾波器提供靈活的路由,或者為多相濾波提供從一個(gè)前端到多個(gè)后端的路由。電平檢測(cè)器把每一條并行數(shù)據(jù)輸入總線上的信號(hào)電平提供給監(jiān)視器,從而使得微處理器增益控制優(yōu)于A/D轉(zhuǎn)換器。

每個(gè)通道的前端部分都包括有正交數(shù)控振蕩器(NCO)、數(shù)字混頻器、桶形移位寄存器和級(jí)聯(lián)積分梳狀濾波器(CIC)。NCO具有32-bit頻率控制字,可用于信道的分選和載波跟蹤,其頻率分辨率可達(dá)16.3MHz(輸入信號(hào)速率為70MSPS)。NCO的無虛假信號(hào)動(dòng)態(tài)范圍(SFDR)大于115dB。桶形移位寄存器可提供介于2-45到2-14之間的增益以防止CIC的溢出。CIC濾波器的級(jí)數(shù)介于1到5級(jí)之間,并且是可編程的,同時(shí),CIC的抽取因子也是可編程的,第5級(jí)的抽取因子為5到512,第4級(jí)的抽取因子為4到2048,第3級(jí)的抽取因子為4到32768,第1級(jí)和第2級(jí)的抽取因子為4到 65536。

每個(gè)通道的后端部分包括有FIR處理模塊、AGC和直角坐標(biāo)到極坐標(biāo)轉(zhuǎn)換器。FIR處理模塊是一個(gè)靈活的濾波器計(jì)算機(jī),它可用于單一或一組串行抽取的濾波,單一濾波器的階數(shù)可達(dá)256,一組串行抽取濾波器的總階數(shù)可達(dá)384。FIR支持像抽取、重采樣、內(nèi)插等各種類型的濾波器。可編程的數(shù)字濾波器系數(shù)的寬度為22-bit,ROM中提供的此系數(shù)可用于幾種半帶濾波器響應(yīng)或重采樣器。而AGC部分則可提供增益高達(dá)96dB的固定或自動(dòng)增益控制。自動(dòng)增益控制具有兩種設(shè)置模式和兩組環(huán)增益。AGC環(huán)使用的直角坐標(biāo)到極坐標(biāo)的轉(zhuǎn)換器輸出也可以用于AM或FM解調(diào)。

ISL5216支持定點(diǎn)和浮點(diǎn)并行輸入模式,其輸出結(jié)果可在4-bit定點(diǎn)到32-bit浮點(diǎn)中選取,并可通過微處理器接口進(jìn)行編程。另外,所有同步通道的輸出數(shù)據(jù)也都通過微處理器接口來讀取。

1.3 ISL5216的設(shè)計(jì)要點(diǎn)

ISL5216主要實(shí)現(xiàn)3個(gè)功能,即數(shù)字正交混頻、數(shù)據(jù)降速率處理和數(shù)據(jù)成形濾波。其參數(shù)配置直接關(guān)系到系統(tǒng)的性能,主要參數(shù)選擇有:總的抽取因子及其在各部分的分配、CIC中的階數(shù)選擇、可編程FTR濾波參數(shù)的選擇、半帶濾波器個(gè)數(shù)的選擇。

總的抽取因子選擇主要取決于最終的輸出數(shù)據(jù)率和ADC的中頻采樣率。最終輸出數(shù)據(jù)率是由所需基帶信號(hào)的帶寬決定的,根據(jù)抽樣定理,輸出數(shù)據(jù)率至少為信號(hào)帶寬的兩倍。ADC采樣率的選擇對(duì)于整個(gè)系統(tǒng)的參數(shù)設(shè)計(jì)有著十分重要的作用,適當(dāng)?shù)倪^采樣對(duì)于提高系統(tǒng)的性能會(huì)有一定好處。我們從公式 SNR=6.02N+1.7dB+10log(fs/2B)即可得出結(jié)論,式中,N為ADC:的位數(shù),fs為采樣速率,B為信號(hào)帶寬。可見,要獲得高信噪比,可以提高系統(tǒng)的采樣率。但采樣率過高,那么最終的抽取因子必然選得很大,這對(duì)于抽取前端的抗混疊濾波器來講,勢(shì)必增加其階數(shù)和計(jì)算量;采樣率過低,會(huì)增加采樣前端抗混疊濾波器的階數(shù),從而造成設(shè)計(jì)和制造上的困難。所以,要根據(jù)實(shí)際情況來確定ADC:采樣率。

CIC濾波器是由5級(jí)積分器和梳狀濾波器組成的抽取濾波器,其階數(shù)和抽取因子可以分別在1~5和4~65 536中選擇,這是根據(jù)ISL5216數(shù)據(jù)手冊(cè)中抽取因子與混疊抑制比的關(guān)系來決定的。

可編程FIR濾波器是整個(gè)ISL5216中最靈活的部分,可實(shí)現(xiàn)抽取,也可單獨(dú)進(jìn)行濾波而不抽取。其階數(shù)和系數(shù)的選擇是根據(jù)ISL5216本身的系統(tǒng)資源和可用時(shí)鐘數(shù)來決定的。

抽取鏈中單個(gè)FIR濾波器階數(shù)可以達(dá)到256階,多個(gè)FIR濾波器的總階數(shù)可以達(dá)到384階。半帶濾波器的選擇是靈活的:若抽取率較高,可用半帶濾波器實(shí)現(xiàn)抽取,最后使用非抽取可編程FIR濾波器來進(jìn)行均衡;若抽取率較低,可以通過可編程FIR濾波器直接實(shí)現(xiàn)抽取濾波而不選用半帶濾波器,這是因?yàn)榘霂V波器的階數(shù)少,濾波幅頻特性較差。

ISL5216參數(shù)的設(shè)計(jì)思路是:首先確定中頻采樣的采樣率和最終輸出的數(shù)據(jù)率,根據(jù)兩者的要求來確定可用的時(shí)鐘數(shù)和總抽取因子;然后進(jìn)行總抽取因子的分配,包括根據(jù)CIC:抽取因子與抗混疊抑制比的關(guān)系確定CIC部分的抽取因子,同時(shí)也確定了后續(xù)可編程FIR濾波器和半帶濾波器的抽取因子;最后再根據(jù)可用的時(shí)鐘數(shù)和所需的抽取因子計(jì)算出FIR濾波器的階數(shù)、系數(shù)及半帶濾波器的個(gè)數(shù);最后核算所使用的資源和時(shí)鐘數(shù)是否滿足要求。

2 ISL5216的設(shè)計(jì)實(shí)例

在中頻通用接收平臺(tái)中,接收的中頻信號(hào)經(jīng)A/D采樣后直接進(jìn)入ISL5216的輸入端進(jìn)行處理。ISL5216的串行輸出都接入FPGA中,進(jìn)行串并轉(zhuǎn)換并存入FIF0,由DSP讀取以進(jìn)行后續(xù)的處理。通過這樣一個(gè)確定的硬件平臺(tái),只需要修改QDDC的內(nèi)部寄存器參數(shù)就能夠?qū)崿F(xiàn)對(duì)解調(diào)中心頻率、輸出速率、濾波器帶寬等參數(shù)的軟件控制,實(shí)現(xiàn)需要的解調(diào)功能。下面將根據(jù)使用中的實(shí)例來說明QDDC參數(shù)配置的主要流程。

2.1 FM信號(hào)解調(diào)

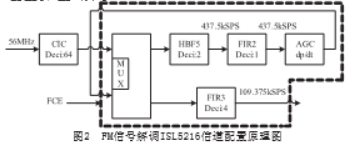

對(duì)一個(gè)采樣頻率為56MHz的FM信號(hào)進(jìn)行解調(diào),在鑒頻器后需要再加一級(jí)濾波器,這時(shí)QDDC某一通道的配置原理圖如圖2所示。

信號(hào)首先通過抽取因子為64的CIC濾波器,將56MHz的信號(hào)速率降低到875kHz。然后HBF5進(jìn)行抽取因子為2的抽取,接著通過抽取因子為1的 FIR2,這時(shí)信號(hào)的速率已經(jīng)降為437.5kSPS。FIR2是一個(gè)帶寬為260kHz的低通濾波器,用來降低帶外噪聲干擾。FIR2輸出的信號(hào)在通過 AGC和鑒頻器后并不直接輸出,而是反饋回FCE(濾波器計(jì)算引擎)進(jìn)入FIR3,濾波后的信號(hào)才會(huì)輸出FCE。FIR3是一個(gè)帶寬為20kHz的低通濾波器,抽取因子為4,其信號(hào)輸出速率為109.375kHz。如有需要可以在輸出之前、FIR3之后連接重采樣濾波器,進(jìn)行分?jǐn)?shù)抽取因子的抽取,使輸出的信號(hào)速率能與后續(xù)處理設(shè)備的速率相匹配。FIR濾波器的系數(shù)使用Matlab中的fdatool工具來設(shè)計(jì),將系數(shù)按照濾波器文件格式制作成*.imp文件格式。使用ISL5216配置軟件對(duì)ISL5216的內(nèi)部寄存器進(jìn)行設(shè)置。設(shè)置如圖3所示。

FIR2的輸出需要反饋回FCE以進(jìn)行最后一級(jí)的濾波,但I(xiàn)SL5216配置軟件并不支持反饋設(shè)置,必須自己修改寄存器的值。地址為*108的指令寄存器必須進(jìn)行修改。FIR2對(duì)應(yīng)的指令寄存器為*108~*10B,其中地址為*108的寄存器的比特位28∶18需要進(jìn)行修改,由290Cxxxx改為 2A8Cxxxx,作用是使能AGCLF,Pamvth(1∶0)設(shè)為”01”,OS停止,F(xiàn)B設(shè)為1。最后在串行輸出的時(shí)候,應(yīng)將輸出格式選為Q2。

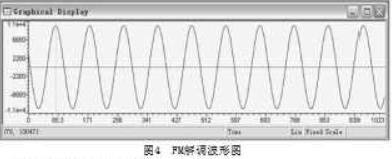

載波頻率70MHz,頻偏15kHz,調(diào)制信號(hào)頻率1kHz的FM信號(hào)解調(diào)后的波形如圖4所示。

2.2 寬帶信號(hào)解調(diào)

ISL5216單通道的輸出帶寬可達(dá)到1MHz,更寬的帶寬可通過多通道串聯(lián)或多相濾波來獲得。下面我將根據(jù)使用中的實(shí)例來說明這種情況下濾波器的結(jié)構(gòu)及 QDDC參數(shù)配置的主要流程。例如:輸入速率:56MSPS(10x),輸出速率:14MSPS(2.5x),輸出帶寬:5.6MHz。

這種情況要使用全部四個(gè)通道才能實(shí)現(xiàn)。QDDC濾波器的結(jié)構(gòu)如圖5所示。

通常,最好是CIC濾波器的抽取因子盡可能地大,這樣,向FCE中寫數(shù)據(jù)所用的時(shí)鐘周期就少,但是這又受到混疊衰減的限制。在本例中CIC的抽取因子為 4,混疊衰減大于60dB(fs/R=0.5/2.5=0.2)。

通道0的輸出分別輸入到通道l、2、3構(gòu)成三個(gè)分支的脈動(dòng)陣列(systolic avrray)。每個(gè)分支都要經(jīng)過一個(gè)19階的濾波器。通道0、1、2、3濾波器的輸入分別延時(shí)0、1、2、3個(gè)采樣時(shí)鐘,使得通道3輸出第一個(gè)數(shù)據(jù)而通道0輸出最后一個(gè)數(shù)據(jù)。由于從輸入到輸出的總抽取數(shù)為4×4=16,每個(gè)通道可以輸出16位的數(shù)據(jù)。在這種結(jié)構(gòu)中需要一個(gè)外部的多路復(fù)用器來組合輸出數(shù)據(jù),即先讀取D路數(shù)據(jù),然后是C、B,最后是A路。

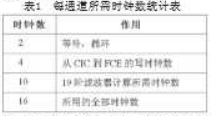

通道0、1、2、3每個(gè)輸出可提供的時(shí)鐘數(shù)為4×4=16,每個(gè)通道所需的時(shí)鐘數(shù)如表l所示,即通道0、1、2、3使用了該通道可提供的每一個(gè)時(shí)鐘。

使用ISL5216配置軟件對(duì)ISL5216的內(nèi)部寄存器進(jìn)行設(shè)置。設(shè)置如圖6所示。

其中第26項(xiàng),每個(gè)通道的延時(shí)各不相同。地址為F801的寄存器低17位的設(shè)置需要注意一下,主要是各通道AGC和FIR輸入輸出路徑的選擇。

3 結(jié)束語

本文講述了四通道數(shù)字下變頻器ISL5216的功能特點(diǎn)及設(shè)計(jì)要點(diǎn),并從工作實(shí)際出發(fā),詳細(xì)介紹了針對(duì)FM信號(hào)解調(diào)鑒頻器后的濾波器設(shè)計(jì)和利用多通道串聯(lián)來實(shí)現(xiàn)寬帶信號(hào)處理的具體的設(shè)計(jì)方法。該兩種設(shè)計(jì)方法在不同的實(shí)際應(yīng)用中均性能良好,達(dá)到了預(yù)期的指標(biāo)。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

555文章

8120瀏覽量

354009 -

變頻器

+關(guān)注

關(guān)注

253文章

6746瀏覽量

147798 -

無線電

+關(guān)注

關(guān)注

60文章

2161瀏覽量

117418

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

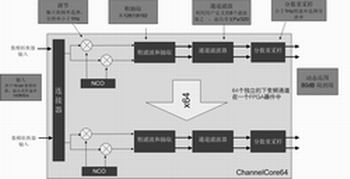

使用一個(gè)FPGA便可實(shí)現(xiàn)的64通道下變頻器

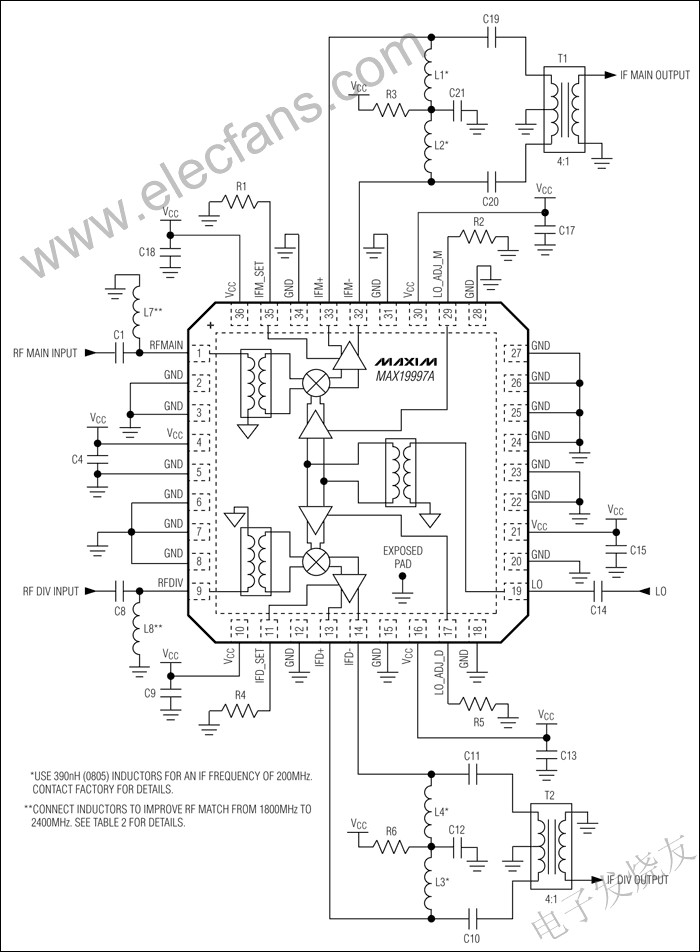

MAX19997A 雙通道下變頻混頻器

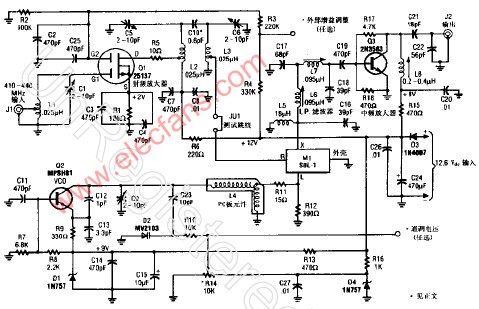

基于FPGA的數(shù)字下變頻器的設(shè)計(jì)與實(shí)現(xiàn)

數(shù)字上/下變頻器簡介:VersaCOMM?可重構(gòu)數(shù)字轉(zhuǎn)換器

AD6636:150 MSPS、寬帶、數(shù)字下變頻器(DDC)數(shù)據(jù)表

基于FPGA的數(shù)字下變頻器(DDC)的設(shè)計(jì)

數(shù)字下變頻器是怎么回事

通道數(shù)字下變頻器ISL5216的功能特點(diǎn)及應(yīng)用研究

通道數(shù)字下變頻器ISL5216的功能特點(diǎn)及應(yīng)用研究

評(píng)論