由于平時我們工作中,F(xiàn)IFO都是直接調(diào)用IP核,對于FIFO深度選擇并沒有很在意,而在筆試面試過程中,經(jīng)常被問及的問題之一就是如何計算FIFO深度。

當(dāng)讀數(shù)據(jù)的速率小于寫數(shù)據(jù)的速率時,我們需要先將數(shù)據(jù)緩存下來,那么我們需要開多大的空間緩存這些數(shù)據(jù)呢?緩存開大了會浪費資源,開小了會丟失數(shù)據(jù),如何去計算最小FIFO深度是本文的重點。

本文涵蓋了FIFO最小深度計算所有情況:

假如模塊A不間斷的往FIFO中寫數(shù)據(jù),模塊B同樣不間斷的從FIFO中讀數(shù)據(jù),不同的是模塊A寫數(shù)據(jù)的時鐘頻率要大于模塊B讀數(shù)據(jù)的時鐘頻率,那么在一段時間內(nèi)總是有一些數(shù)據(jù)沒來得及被讀走,如果系統(tǒng)一直在工作,那么那些沒有被讀走的數(shù)據(jù)會越累積越多,那么FIFO的深度需要是無窮大的;

但是若寫操作是連續(xù)的數(shù)據(jù)流,那么再大的FIFO都無法保證數(shù)據(jù)不溢出。因此可以認(rèn)為這種情況下寫數(shù)據(jù)的傳輸是“突發(fā)Burst”的,即寫操作并不連續(xù);

要確定FIFO的深度,關(guān)鍵在于計算出在突發(fā)讀寫這段時間內(nèi)有多少個數(shù)據(jù)沒有被讀走。即FIFO的最小深度就等于沒有被讀走的數(shù)據(jù)個數(shù)。

Case1 fa》fb with no idle cycles in both write and read

即寫時鐘快于讀時鐘,寫和讀的過程中沒有空閑周期;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=80MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

在突發(fā)傳輸過程中,數(shù)據(jù)都是連續(xù)讀寫的

那么:

寫一個數(shù)據(jù)所需要的時間 = 1/80MHz = 12.5ns

突發(fā)傳輸中,寫完所有數(shù)據(jù)所需要的時間 = 120*12.5ns = 1500ns

讀一個數(shù)據(jù)所需要的時間 = 1/50MHz = 20ns

所以寫完所有的突發(fā)傳輸數(shù)據(jù)需要花費1500ns

在1500ns內(nèi)能夠讀走的數(shù)據(jù)個數(shù) = 1500ns/20ns = 75

所以在1500ns內(nèi)還沒有被讀走的數(shù)據(jù)個數(shù) = 120-75 = 45

因此FIFO的最小深度為45

Case2 fa》fb with two clock cycle delay between two successive read and write

即寫時鐘頻率大于讀時鐘頻率,但在讀寫的過程中存在空閑周期;

Case2在Case1的基礎(chǔ)上增加了一個假設(shè),即讀比寫慢兩拍。這種假設(shè)是真正存在的,在異步FIFO設(shè)計中,我們需要去判斷FIFO的空滿來保證邏輯的正確性,判斷空滿標(biāo)志需要去比較讀寫指針,而讀指針與寫指針處在不同的時鐘域中,我們需要采用格雷碼和兩級同步寄存器去降低亞穩(wěn)態(tài)的概率,而兩級同步必然會導(dǎo)致空滿標(biāo)志位的判斷至少延遲2個cycle。對于空標(biāo)志位來說,將寫指針同步到讀時鐘域至少需要花費2個時鐘,而在同步這段時間內(nèi)有可能還會寫入新的數(shù)據(jù),因此同步后的寫指針一定小于或等于(當(dāng)且僅有同步時間內(nèi)沒有新數(shù)據(jù)寫入的情況下才會等于)當(dāng)前的寫指針,所以此時判斷不一定是真空;同理,對于滿標(biāo)志位來說,將讀指針同步到讀時鐘域至少需要花費2個時鐘,而在同步這段時間內(nèi)有可能還會讀出新的數(shù)據(jù),因此同步后的讀指針一定小于或等于當(dāng)前讀指針,所以此時判斷并不一定是真滿。

通過上述討論可以知道Case2的FIFO最小深度應(yīng)該比場景1的FIFO最小深度45略大。

Case3 fa 》 fb with idle cycles in both write and read

即寫時鐘頻率大于讀時鐘頻率,但在讀寫的過程中存在空閑周期;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=80MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

連續(xù)寫入之間的空閑周期為1。

連續(xù)讀取之間的空閑周期為3。

那么:

兩個連續(xù)寫之間的空閑周期為1個時鐘周期。它的意思是,在寫入一個數(shù)據(jù)后,模塊A等待一個時鐘周期,開始下一個寫入。因此,可以理解為每兩個時鐘周期,一個數(shù)據(jù)被寫入;

兩個連續(xù)讀取之間的空閑周期為3個時鐘周期。即讀取一個數(shù)據(jù)后,B模塊等待3個時鐘周期,開始下一次讀取。因此,我們可以理解,每四個時鐘周期,讀取一個數(shù)據(jù);

寫一個數(shù)據(jù)所需要的時間 = 2*1/80MHz = 25ns

突發(fā)傳輸中,寫完所有數(shù)據(jù)所需要的時間 = 120*25ns = 3000ns

讀一個數(shù)據(jù)所需要的時間 = 4*1/50MHz = 80ns

所以寫完所有的突發(fā)傳輸數(shù)據(jù)需要花費3000ns

在3000ns內(nèi)能夠讀走的數(shù)據(jù)個數(shù) = 3000ns/80ns = 37.5

所以在3000ns內(nèi)還沒有被讀走的數(shù)據(jù)個數(shù) = 120-37.5 = 82.5

因此FIFO的最小深度為83

Case4 fa 》 fb with duty cycles given for wr_enb and rd_enb.

即寫時鐘頻率大于讀時鐘頻率,給定wr_enb和rd_enb的占空比;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=80MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

寫使能信號占整個burst時間比重為1/2

讀使能信號占整個burst時間比重為1/4

那么:

此場景與前一個場景(場景3)沒有任何不同,因為在本例中,一個數(shù)據(jù)項將在2個時鐘周期內(nèi)寫入,而一個數(shù)據(jù)項將在4個時鐘周期內(nèi)讀取。

因此FIFO的最小深度也為83

Case5 fA 《 fB with no idle cycles in both write and read ( the delay between two consecutive writes and reads is one clock cycle)

即寫時鐘頻率小于讀時鐘頻率,且讀寫過程中沒有空閑周期;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=30MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

在突發(fā)傳輸過程中,數(shù)據(jù)都是連續(xù)讀寫的

那么:

由于讀數(shù)據(jù)比寫數(shù)據(jù)要快,這種情況下永遠(yuǎn)也不會發(fā)生數(shù)據(jù)丟失的,因此FIFO只起到過時鐘域的作用,F(xiàn)IFO的最小深度為1即可;

Case6 fa 《 fb with idle cycles in both write and read(duty cycles of wr_enb and rd_enb can also be given in these type of questions)。

即寫時鐘頻率小于讀時鐘頻率,給定wr_enb和rd_enb的占空比;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=40MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

連續(xù)寫入之間的空閑周期為1。

連續(xù)讀取之間的空閑周期為3。

那么:

兩個連續(xù)寫之間的空閑周期為1個時鐘周期。它的意思是,在寫入一個數(shù)據(jù)后,模塊A等待一個時鐘周期,開始下一個寫入。因此,可以理解為每兩個時鐘周期,一個數(shù)據(jù)被寫入;

兩個連續(xù)讀取之間的空閑周期為3個時鐘周期。即讀取一個數(shù)據(jù)后,B模塊等待3個時鐘周期,開始下一次讀取。因此,我們可以理解,每四個時鐘周期,讀取一個數(shù)據(jù);

寫一個數(shù)據(jù)所需要的時間 = 2*1/40MHz = 50ns

突發(fā)傳輸中,寫完所有數(shù)據(jù)所需要的時間 = 120*50ns = 6000ns

讀一個數(shù)據(jù)所需要的時間 = 4*1/50MHz = 80ns

所以寫完所有的突發(fā)傳輸數(shù)據(jù)需要花費6000ns

在6000ns內(nèi)能夠讀走的數(shù)據(jù)個數(shù) = 6000ns/80ns = 75

所以在6000ns內(nèi)還沒有被讀走的數(shù)據(jù)個數(shù) = 120-75 = 45

因此FIFO的最小深度為45

Case7 fA = fB with no idle cycles in both write and read ( the delay between two consecutive writes and reads is one clock cycle)。

即寫時鐘頻率等于讀時鐘頻率,且讀寫過程中沒有空閑周期;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=50MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

讀和寫都沒有空閑周期,這意味著突發(fā)中的所有項都將以連續(xù)的時鐘周期寫入和讀取

那么:

如果clkA和clkB之間沒有相位差,則不需要FIFO;

如果clkA和clkB之間存在相位差,深度“1”的FIFO就足夠了。

Case8 fA = fB with idle cycles in both write and read (duty cycles of wr_enb and rd_enb can also be given in these type of questions)。

即寫時鐘頻率等于讀時鐘頻率,給定wr_enb和rd_enb的占空比;

假設(shè):

寫數(shù)據(jù)時鐘頻率fa=50MHz

讀數(shù)據(jù)時鐘頻率fb=50MHz

突發(fā)長度= number of data to be transferred = 120

連續(xù)寫入之間的空閑周期為1。

連續(xù)讀取之間的空閑周期為3。

那么:

兩個連續(xù)寫之間的空閑周期為1個時鐘周期。它的意思是,在寫入一個數(shù)據(jù)后,模塊A等待一個時鐘周期,開始下一個寫入。因此,可以理解為每兩個時鐘周期,一個數(shù)據(jù)被寫入;

兩個連續(xù)讀取之間的空閑周期為3個時鐘周期。即讀取一個數(shù)據(jù)后,B模塊等待3個時鐘周期,開始下一次讀取。因此,我們可以理解,每四個時鐘周期,讀取一個數(shù)據(jù);

寫一個數(shù)據(jù)所需要的時間 = 2*1/50MHz = 40ns

突發(fā)傳輸中,寫完所有數(shù)據(jù)所需要的時間 = 120*40ns = 4800ns

讀一個數(shù)據(jù)所需要的時間 = 4*1/50MHz = 80ns

所以寫完所有的突發(fā)傳輸數(shù)據(jù)需要花費4800ns

在4800ns內(nèi)能夠讀走的數(shù)據(jù)個數(shù) = 4800ns/80ns = 60

所以在4800ns內(nèi)還沒有被讀走的數(shù)據(jù)個數(shù) = 120-60 = 60

因此FIFO的最小深度為60

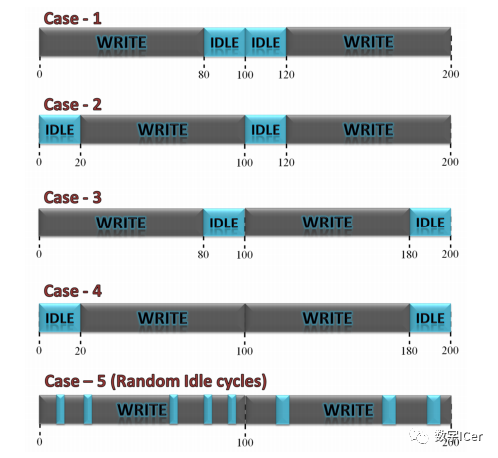

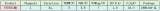

Case9 如果數(shù)據(jù)速率如下所示

在前面幾種場景中,我們給的條件都是每隔幾個時鐘讀寫一次,這種周期性讀寫在實際中很常見。但是在工程設(shè)計中還存在這樣一種情形,只給出數(shù)據(jù)在一段時間內(nèi)的讀寫速率,怎么讀寫完全隨機,這種情況我們需要考慮最壞的一種情況避免數(shù)據(jù)丟失。

對于最壞的情況,讀寫之間的數(shù)據(jù)速率差異應(yīng)該是最大的。因此,對于寫操作,應(yīng)該考慮最大數(shù)據(jù)速率,對于讀操作,應(yīng)該考慮最小數(shù)據(jù)速率。

寫數(shù)據(jù)時鐘頻率fa=讀數(shù)據(jù)時鐘頻率fb

在寫時鐘周期內(nèi),每100個周期就有80個數(shù)據(jù)寫入FIFO

在讀時鐘周期內(nèi),每10個周期可以有8個數(shù)據(jù)讀出FIFO

以下是一些可能性:

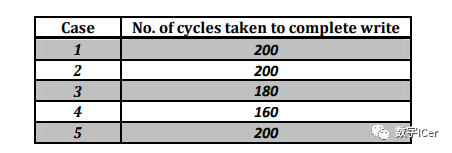

下面是從上圖中觀察到的情況:

寫操作的最大數(shù)據(jù)速率在上表格中case - 4。(寫操作在最小的時間內(nèi)完成)。因此,考慮case - 4來進(jìn)行進(jìn)一步的計算。

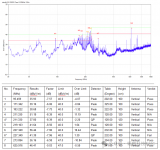

首先這里沒有給出數(shù)據(jù)的突發(fā)長度,從假設(shè)中可以得出每100個周期就有80個數(shù)據(jù)寫入FIFO,這里可能就有人會說突發(fā)長度就是80個數(shù)據(jù),其實不是這樣的,因為數(shù)據(jù)是隨機寫入FIFO的,我們需要考慮做壞的情形,即寫速率最大的情形,只有如下圖背靠背的情形才是寫速率最高的情形,burst length為160;

在讀時鐘周期內(nèi),每10個周期可以有8個數(shù)據(jù)讀出FIFO;即一個周期可以寫入 8/10 數(shù)據(jù)

所以160個時鐘讀了160*8/10 = 128個數(shù)據(jù);

考慮背靠背(20個clk不發(fā)數(shù)據(jù)+80clk發(fā)數(shù)據(jù)+80clk發(fā)數(shù)據(jù)+20clk不發(fā)數(shù)據(jù)的共200個clk)

因此FIFO的最小深度=160 - 128 = 32

總結(jié)

從上面分析來看,求FIFO的最小深度主要有以下要點:

在求解之前需要驗證一下在允許的最大時間長度內(nèi)寫入的數(shù)據(jù)量是否等于讀出的數(shù)據(jù)量,保證有解;

求FIFO深度需要考慮最壞的情形,讀寫的速率應(yīng)該相差最大,也就是說需要找出最大的寫速率和最小的讀速率;

不管什么場景,要確定FIFO的深度,關(guān)鍵在于計算出在突發(fā)讀寫這段時間內(nèi)有多少個數(shù)據(jù)沒有被讀走;

由于FIFO空滿標(biāo)志位的判斷延遲,在實際應(yīng)用中需要預(yù)留一些余量。

下面我們來推導(dǎo)一下FIFO深度的求解公式,假設(shè):

寫時鐘周期為clkw

讀時鐘周期為clkr

在讀時鐘周期內(nèi),每x個周期內(nèi)可以有y個數(shù)據(jù)讀出FIFO,即讀數(shù)據(jù)的讀數(shù)率

在寫時鐘周期內(nèi),每m個周期內(nèi)就有n個數(shù)據(jù)寫入FIFO

背靠背“的情形下是FIFO讀寫的最壞情形,burst長度 B = 2*n

由上得到:FIFO的最小深度為 B - B * (clkr/clkw) * (y/x)

原文標(biāo)題:FIFO深度計算

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

fifo

+關(guān)注

關(guān)注

3文章

400瀏覽量

44649

原文標(biāo)題:FIFO深度計算

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

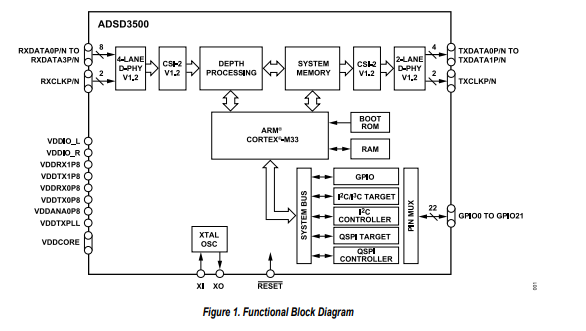

ADSD3500飛行時間深度成像信號處理器技術(shù)手冊

智多晶FIFO_Generator IP介紹

AXI接口FIFO簡介

海光信息技術(shù)團(tuán)隊完成模型與DCU國產(chǎn)化適配

FIFO IP核的使用教程

請問DAC5682z內(nèi)部FIFO深度為多少,8SAMPLE具體怎么理解?

DVI接口的ESD保護(hù)方案

矢量網(wǎng)絡(luò)分析儀(VNA)基礎(chǔ)解析與應(yīng)用指南

DAC3482內(nèi)部的FIFO作用是什么?

DAC3482在按字寬度輸入模式下,為啥SYNC信號每16*n個FIFO采樣重復(fù)一次?

顯示器視頻接口的ESD保護(hù)器件選擇指南

脫毛儀產(chǎn)品的EMI整改案例

FIFO Generator的Xilinx官方手冊

FIFO的深度應(yīng)該怎么計算

Efinity FIFO IP仿真問題 -v1

FIFO最小深度計算所有情況

FIFO最小深度計算所有情況

評論