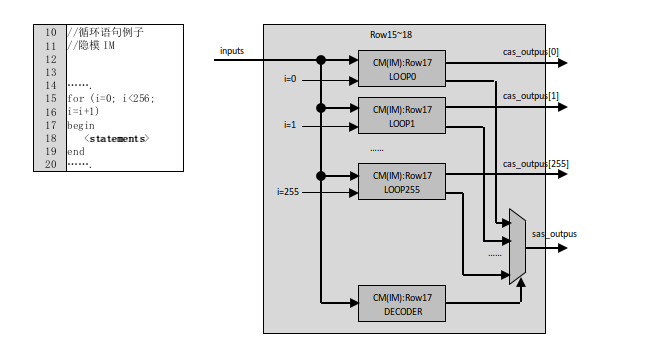

在HDL的循環(huán)語句中,在指定的循環(huán)過程中,其代碼塊(循環(huán)體)輸出同名信號,則構(gòu)成順序-循環(huán)(SAS-LOOP),其代碼塊(循環(huán)體)輸出不同名信號,則構(gòu)成并發(fā)-循環(huán)(CAS-LOOP)。

包括循環(huán)語句(含循環(huán)體)組成的代碼塊,EDA稱為循環(huán)框架(Loop Frame)。

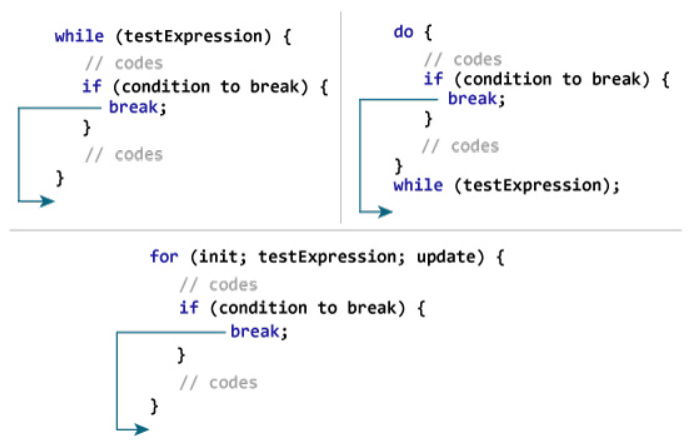

在這里,HDL循環(huán)語句與算法語言的循環(huán)語句的差異:

1.HDL的循環(huán)變量i是以常量進入循環(huán)體。算法語言則是以變量進入循環(huán)體。

2.HDL的循環(huán)體并不被循環(huán)執(zhí)行,而是被重復(fù)描述(多次重復(fù)綜合),從而實現(xiàn)建模的效率。算法語言的循環(huán)體則一定是被循環(huán)執(zhí)行。

循環(huán)語句可綜合性的“數(shù)學(xué)歸納法”

數(shù)學(xué)歸納法常用于證明數(shù)學(xué)序列,它的要點是:

1.首先證明序列的基數(shù)成立

2.假設(shè)序列為N時成立

3.證明序列的N+1成立

HDL的循環(huán)語句是否可綜合,可以借用這個方法:

1.首先將循環(huán)語句的循環(huán)次數(shù)修改為一個很小的基數(shù)。由于在很小的基數(shù)時,其電路一定可以用結(jié)構(gòu)化方法直接描述(不使用循環(huán)語句)

2.將基數(shù)加1,仍然可以是結(jié)構(gòu)化描述,并加以驗證

3.將基數(shù)修改為LPM參數(shù)可定制,使用循環(huán)語句描述,并加以驗證

4.修改LPM定制參數(shù),將其加1,觀察其綜合結(jié)果(驗證)

通過以上步驟,可以證明所編寫的HDL循環(huán)語句是可綜合的,并且具有很高的綜合效率。

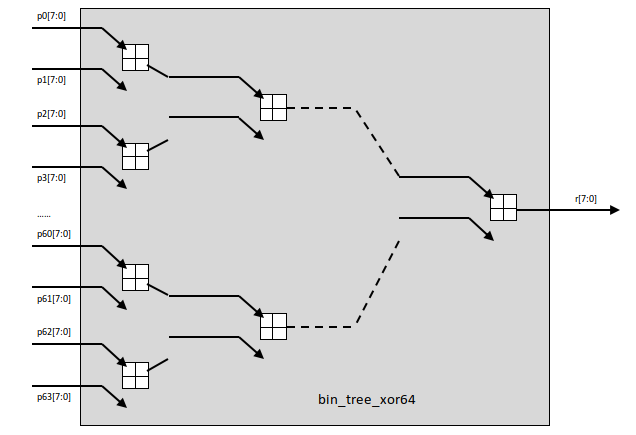

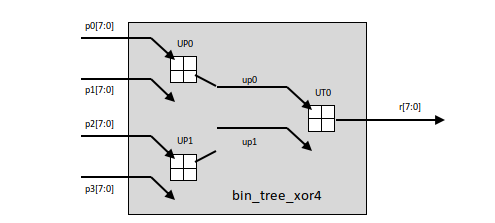

循環(huán)語句設(shè)計例子:具有64個輸入端口的8位異或電路:

使用“數(shù)學(xué)歸納法”為其使用循環(huán)語句建模和驗證:

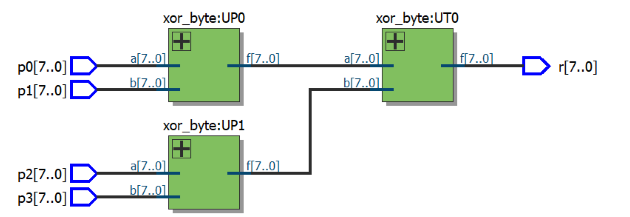

1.將基數(shù)(端口數(shù))設(shè)定為4,得到:

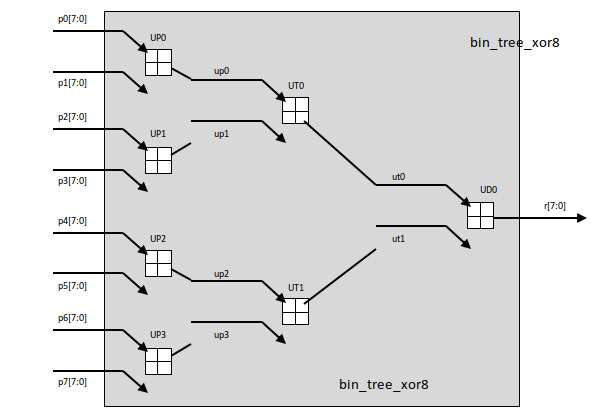

RTL視圖(驗證過程):

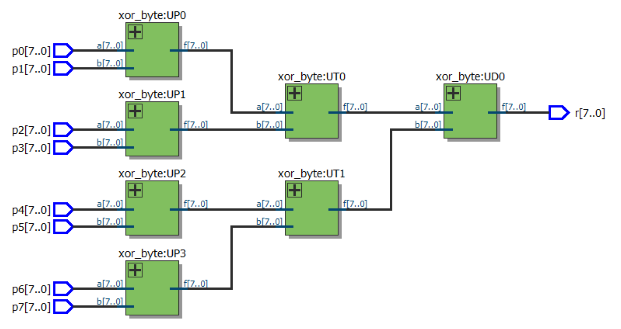

2.將基數(shù)加1,這里將端口數(shù)修改為8,得到:

RTL視圖(驗證過程):

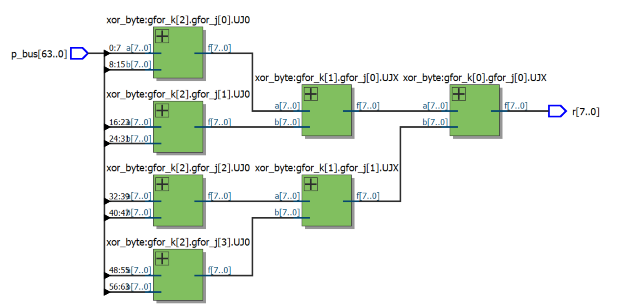

修改為端口數(shù)可定制的LPM模型

其RTL視圖:

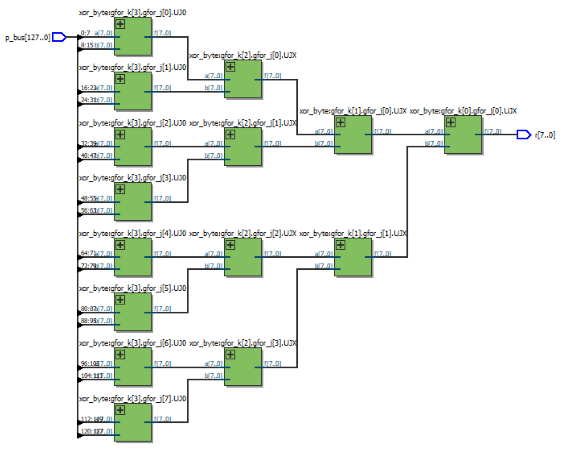

現(xiàn)在將LPM的基數(shù)+1(修改端口指數(shù)PortNum_Power為4)

其RTL視圖:

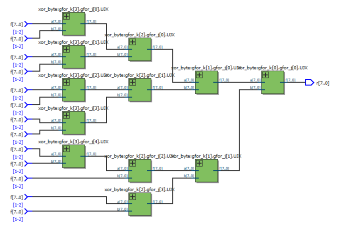

以上就是循環(huán)語句構(gòu)成二叉樹異或門的過程,為了得到最終結(jié)果(64端口),將端口指數(shù)PortNum_Power=6,得到:

這里由于端口數(shù)過多,EDA的自動繪圖需要中間過程,故首層僅展示如上部分。

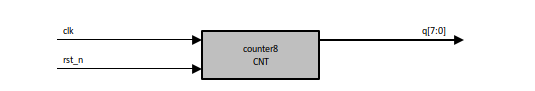

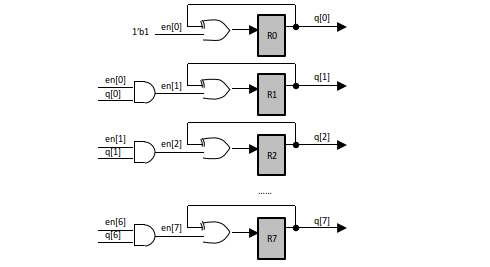

循環(huán)語句可綜合性的設(shè)計例子二:同步計數(shù)器的結(jié)構(gòu)化設(shè)計

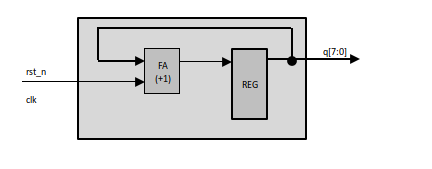

1.頂層框圖

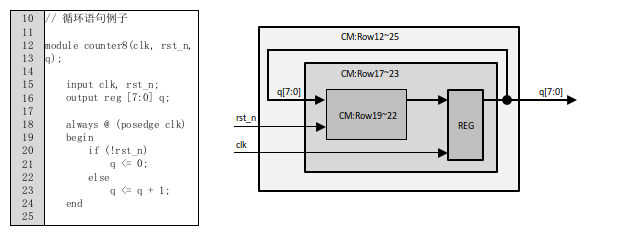

2.代碼和代碼模型分析

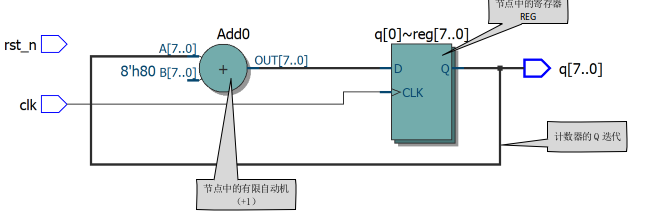

其RTL視圖:

以上視圖中,當(dāng)rst_n=0時,多路器指向常數(shù)0;當(dāng)rst_n=1時,多路器指向加法器的輸出;注意加法器是寄存器的輸出q與1相加。

根據(jù)代碼模型和RTL視圖,可以得到等效節(jié)點模型:

若將復(fù)位信號的條件語句描述屏蔽,則得到RTL視圖更接近節(jié)點等效:

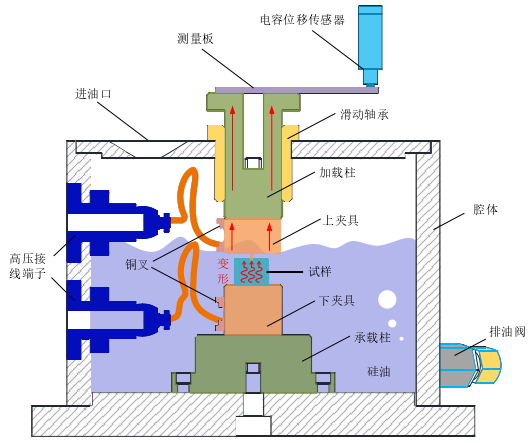

3.計數(shù)器的數(shù)學(xué)模型

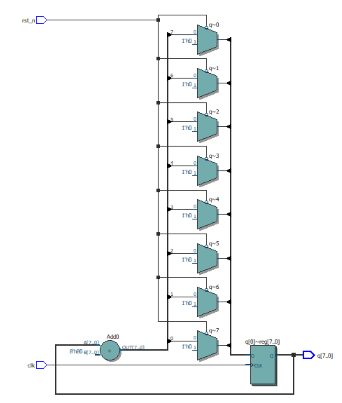

在RTL視圖中,計數(shù)器有限自動機的加法器執(zhí)行q+1(的描述),其真實的電路是得到優(yōu)化和簡化的一個數(shù)學(xué)模型:

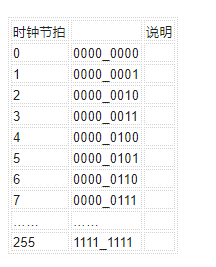

若Q序列表示為:

在時鐘離散時刻,Q的變化為:

觀察表格,能夠發(fā)現(xiàn)Q的每一個比特位翻轉(zhuǎn)的規(guī)律:

()

(, )

(, )

……

(, )

將觸發(fā)翻轉(zhuǎn)的條件(前級全部為1)采用級聯(lián)以減少面積:

(,)

(, )

(, )

……

(, )

式中:

…….

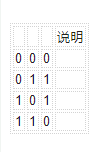

注意位翻轉(zhuǎn)的一般表達式:(, )

其真值表為:

其SOP為:

代入序列中,得到:

……

根據(jù)數(shù)學(xué)模型得到的代碼模型為:

編輯:jq

-

eda

+關(guān)注

關(guān)注

71文章

2900瀏覽量

176589 -

HDL

+關(guān)注

關(guān)注

8文章

330瀏覽量

47843 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60725 -

代碼

+關(guān)注

關(guān)注

30文章

4891瀏覽量

70305 -

LPM

+關(guān)注

關(guān)注

0文章

11瀏覽量

10088

原文標(biāo)題:FPGA學(xué)習(xí):循環(huán)語句的可綜合性

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

深入理解C語言:C語言循環(huán)控制

如何綜合性測試一款電源芯片?——以ASP3605芯片為例

NVIDIA Isaac 是英偉達推出的綜合性機器人開發(fā)平臺

FPGA Verilog HDL語法之編譯預(yù)處理

比斯特BT-100V20C100F 電池組綜合性能測試機:多領(lǐng)域的鋰電池性能檢測能手

技術(shù)干貨驛站 ▏深入理解C語言:嵌套循環(huán)與循環(huán)控制的底層原理

可靠性溫度循環(huán)試驗至少需要幾個循環(huán)?

深入理解C語言:循環(huán)語句的應(yīng)用與優(yōu)化技巧

高壓放大器在壓電材料綜合性能測試中的應(yīng)用

深入解析電池組綜合性能測試機的工作原理

Verilog HDL的基礎(chǔ)知識

FPGA Verilog HDL有什么奇技巧?

引領(lǐng)電池組綜合性能測試新紀(jì)元|比斯特自動化

打造綜合性產(chǎn)業(yè)新高地,海博思創(chuàng)南通“四中心一基地”項目開工

簡述HDL中循環(huán)語句的可綜合性

簡述HDL中循環(huán)語句的可綜合性

評論