最近五年來,功率性能領域(和成本)的提高主要是通過晶體管的尺寸縮放來實現的。晶體管縮放超過納米閾值后,從16/12 nm,10 nm,7 nm,5 nm,3 nm,2 nm,1.4 nm到納米以下,半導體行業將做什么?這些先進的邏輯技術是否會繼續提供未來計算系統所需的能效?新的應用程序和計算工作負載是否需要新的設備技術并將其集成到未來的系統中?這些都是當今半導體行業面臨的一些最緊迫的問題。

未來IC技術發展的道路不再是一條直線。開箱即用的解決方案的需求將迎來創新的黃金時代。未來的電子系統將需要計算架構以及設備和封裝技術的共同創新。那么,全球晶圓代工龍頭臺積電為了將代工這活兒做到極致,又在探索哪些新技術?

無懈可擊的臺積電

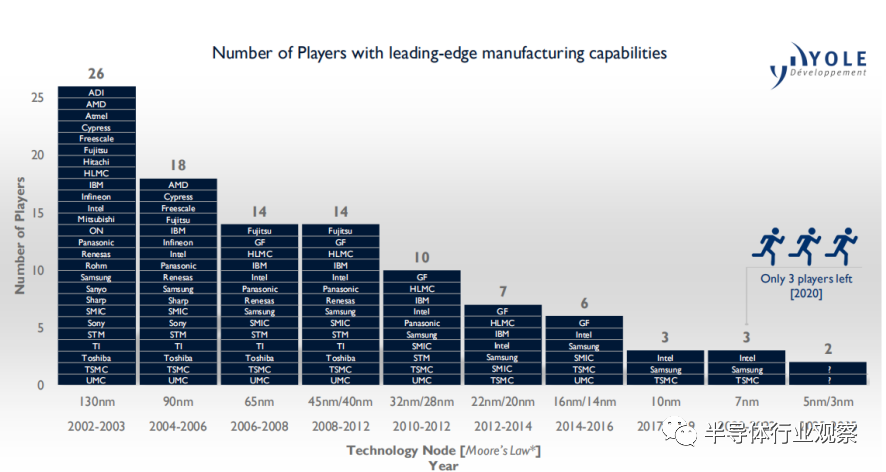

據Yole發布的一份調研報告中顯示,在過去的幾十年里(自1965年以來),摩爾定律一直指導著全球半導體行業,在這個演進的過程中,先進制程的發展提高了性能和成本,大浪淘沙,2002年的26家角逐的廠商最后僅剩臺積電和三星兩家“孤獨者”。在短短的20年間,全球代工廠以放棄而聞名,先進制程玩家減少了近九成。

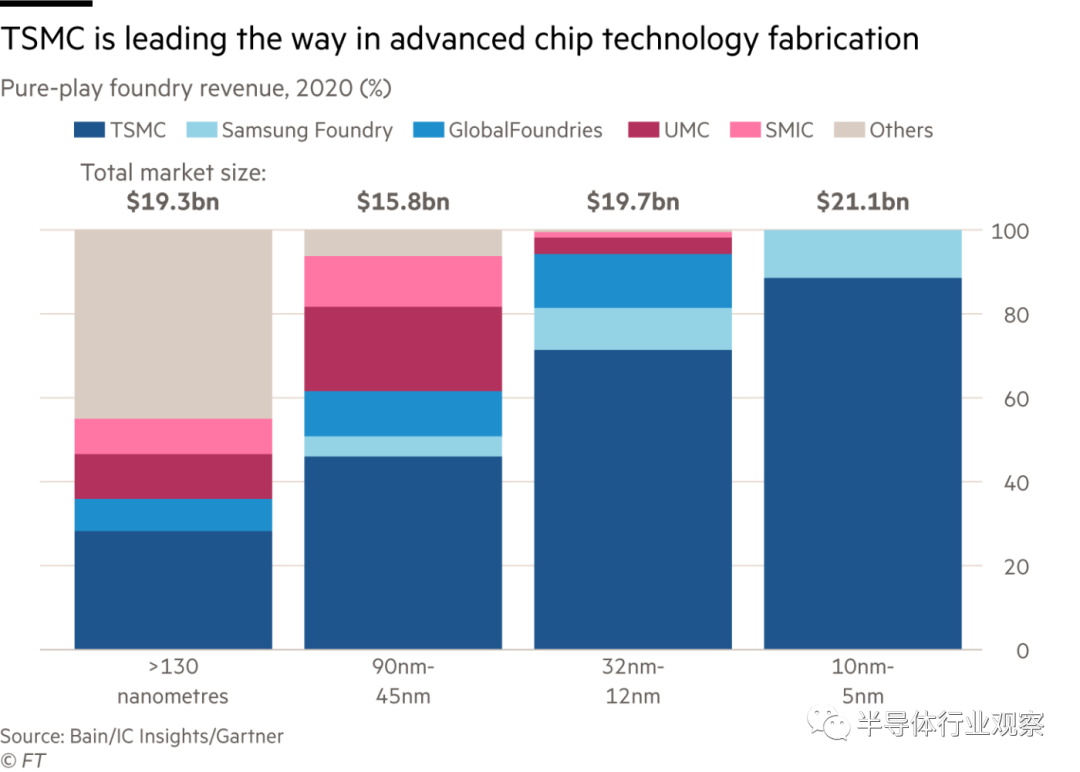

如今臺積電在每個新的工藝技術節點上都變得越來越占主導地位:盡管它僅占28-65nm類別中用于生產大多數汽車芯片的節點的收入的40%至65%,但它幾乎占據了市場的90%當前生產中最先進的節點。

臺積電(TSMC)今年將其資本投資預期上調至高達250億至280億美元,可能比2020年增加63%,領先于英特爾和三星。分析人士認為,這至少包括臺灣制造商向英特爾提供產品所需的產能投資。

邏輯上多管齊下

臺積電一直走在先進CMOS邏輯技術的前沿,在這種技術中,密集晶體管是兩個基本的構建模塊之一,另一個是密集互連堆棧。給定邏輯技術的內在計算能力直接與晶體管互連的數量及其在典型負載下的開關速度有關,這些負載由晶體管或門驅動,以及相關的互連電阻和電容電路負載。在邏輯領域,臺積電主要研究在晶體管結構、高遷移率通道以及低尺寸材料和器件方面的計算。

臺積電CMOS邏輯技術一直依賴于平面晶體管結構,直到2014年其16納米技術就將FinFET引入生產。FinFET結構解決了平面器件縮放的根本限制,即在較短的柵極長度下對溝道的不良靜電控制。FinFET還使晶體管密度縮放與器件有效寬度縮放能夠部分解耦,這是獲得增加的每單位晶體管足跡的晶體管電流的重要功能。與平面晶體管相比,這些FinFET特性可顯著降低電源電壓。FinFET還為功率性能優化提供了新的自由度,從而極大地提高了從16nm到5nm技術節點的能效。

臺積電的研發工作繼續探索下一代結構,例如堆疊納米線或堆疊納米片,以期在未來技術節點的計算性能和能源效率方面達到新的高度。

直到其7nm節點為止,硅一直是所有CMOS技術世代中選擇的晶體管通道材料。臺積電(TSMC)積極探索替代晶體管溝道材料,以在高性能和低功率器件的設計中增加自由度。硅鍺和鍺是臺積電探索性研究工作的例子,該研究工作已被廣泛發表,在某些情況下被公認為國際會議的亮點。臺積電的5nm技術是第一項以SiGe為p型FinFET的溝道材料的先進邏輯生產技術。

此外,臺積電(TSMC)的晶體管研究團隊也在研究以具有固有2D或1D載流子傳輸(低維傳輸)的材料為基礎的器件。過渡金屬二鹵化物,石墨烯納米帶和碳納米管等都在理論和實驗上得到了研究。

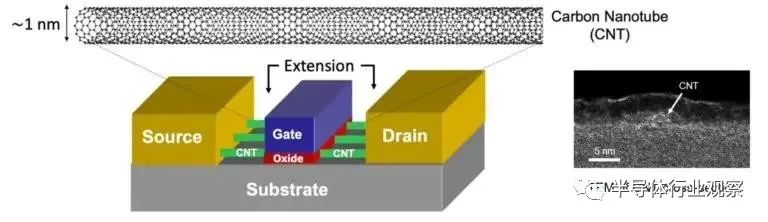

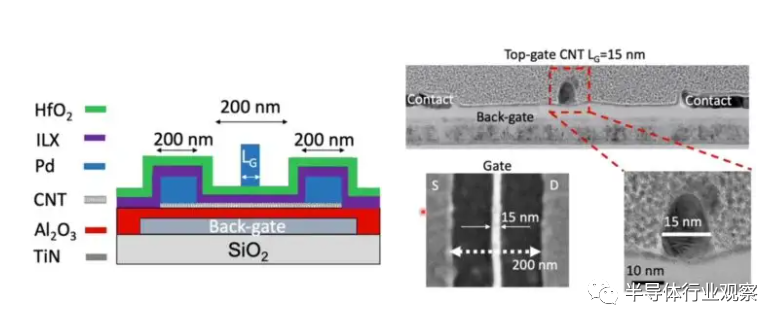

如在最近的IEDM會議上,臺積電提供了有關談納米管器件制造進展的更新。臺積電開發了獨特的工藝流程來為CNT器件提供“高K”電介質等效柵極氧化物,類似于當前硅FET的HKMG處理。隨后,添加高K HfO2膜的原子級沉積(ALD),采用了獨特的“頂柵加背柵”拓撲。

上面的TEM圖說明了CNT的橫截面。為了與獨特的碳表面兼容,需要沉積初始界面電介質(Al2O3)–即,需要在碳上對該薄層進行適當的成核和整合

采用了獨特的“頂柵加背柵”拓撲

使用2D和1D材料的好處包括原子厚度的高遷移率,出色的柵極控制以及低功率和高性能器件的潛在應用。因此,可以擴大晶體管的縮放比例。在最近的報道中,臺積電成功地證明了晶圓級h-氮化硼單層膜的生長,該膜層能夠有效地保護通道2D半導體免受工藝損傷以及相鄰電介質中電荷雜質的擴散。一維半導體碳納米管具有與生產線后端(BOEL)制造溫度(《400℃)兼容的工藝,是實現單片3D IC的潛在組件。在臺積電的28nm CMOS技術芯片上,碳納米管晶體管的概念驗證整體集成也得到了驗證。

在互連上的探索

互連對于系統性能至關重要。它們是將兩個或多個電路元件(例如晶體管)電連接在一起的結構。在過去,互連通常被稱為集成電路的片上互連。如今,互連通常既包括集成電路的片上互連又包括異構系統集成中的片外互連。在互連設計中,幾何尺寸(寬度,厚度,間距,長寬比,間距),材料,過程控制和設計布局對于適當的互連功能,性能,功率效率,可靠性和制造良率都是至關重要的。

首先來看片上互連,當今的片上互連基于銅線/低k布線,在當今的芯片中,銅線可能超過100公里。臺積電使用新穎的銅間隙填充解決方案來制造更小的導線。新開發的材料和工藝可以大大減少線路和通孔電阻,從而改善芯片性能。集成方案,低k材料和具有選擇性沉積的低k工藝的全面創新套件進一步提高了性能(通過減小電容)和可靠性。除了銅互連之外,臺積電內部以及其學術合作伙伴也正在探索單一金屬元素,二元和三元合金以及用于未來互連材料的2D材料。

然后是片外互連技術。要知道,硅中介層,高密度細間距扇出RDL和無凸點鍵合是創新的先進異構集成技術(HIT)上芯片間互連的三大支柱。每種互連技術在AI和5G網絡各自的領域中提供最佳的PPACC(PPACC:功耗,性能,面積(尺寸),成本,上市周期),并且與晶圓級異構集成技術(即HPC和移動應用系統中的CoWoS,InFO和SoIC)緊密相關。

臺積電也在片外互聯技術上不斷努力以實現更好的PPACC:硅中介層具有高互連密度,高比電容密度和大標線片尺寸,可用于百億分之一的HPC / AI;扇出時具有較高的互連密度和較大的光罩尺寸,可在HPC /網絡AI中實現成本和性能;在SoIC上,高3D互連密度和超低鍵合延遲,適用于節能計算系統。

對新興存儲技術的探索

內存也是臺積電發展的一大重點,現代社會,每天生成的數據超過2.5億字節,需要處理的數據非常多,而內存在數據流中起著關鍵作用。邏輯與內存之間的差距是系統性能的瓶頸。為了優化成本和性能之間的權衡,市面上已開始采用分層存儲系統。

最近出現的新技術正在迅速發展,以將處理任務帶到內存附近或內存中,以提高計算效率并啟用新功能。新興的NVM使用新型的材料和機制來存儲數據。它們有望用于混合內存層次結構以提高整體性能。此外,它們的獨特特性為啟用新應用程序(例如神經形態計算)和新穎的體系結構(例如3D集成)提供了巨大的潛力。

臺積電這些年正在積極探索新興存儲技術。臺積電的非易失性存儲器解決方案包括閃存,自旋轉移力矩磁性隨機存取存儲器(STT-MRAM)和電阻式隨機存取存儲器(RRAM)。臺積電還積極探索相變隨機存取存儲器(PCRAM)和自旋軌道扭矩MRAM(SOT-MRAM)元件,以及支持更高密度交叉點陣列架構必不可少的選擇器設備。

臺積電已經開發并提供STT-MRAM解決方案,以克服嵌入式Flash技術的擴展限制。臺積公司正在積極探索SOT-MRAM和VC-MRAM,并與外部研究實驗室、財團和學術合作伙伴合作。臺積電的SOT-MRAM的探索是由高速(《2ns)二進制存儲器解決方案驅動的,這種解決方案比傳統的6T-SRAM解決方案密度大得多,同時也更節能。

MRAM之外,臺積電與技術伙伴合作,在40nm CMOS邏輯主干上開發了RRAM內存技術,以支持特定應用需求。臺積電還在繼續探索新穎的RRAM材料組合及其密度驅動的集成,以及可變感知電路設計和程序設計,以實現高密度內嵌RRAM的解決方案,以供AIoT應用。

相變隨機存儲器(PCRAM)是一種基于硫族玻璃的非易失性存儲器。PCRAM電阻通過控制焦耳加熱和淬火在非晶態(高電阻)和結晶態(低電阻)之間過渡。存儲器的電阻狀態與非晶區大小及其可控性和穩定性有很大關系。這使得PCRAM細胞具有獨特的存儲多種狀態(電阻)的能力,因此比傳統的二進制存儲器具有更高的有效細胞密度的潛力。PCRAM可以支持陣列配置,包括一個晶體管與一個存儲器(1T1R)陣列和一個選擇器與一個存儲器(1S1R)陣列。臺積電一直在探索PCRAM材料、細胞結構和專用電路設計,以實現AI和ML的近內存和內存計算。

結語

在新技術短缺和超級大國競爭的時候,臺積電在芯片生產中的主導地位凸顯。而觀看其對先進技術的不懈探索,不由發問,代工廠的秘訣在哪里?想要追趕臺積電的英特爾前面又有多少攔路虎?三星估計也在想,我與臺積電究竟差哪了?

責任編輯:lq

-

臺積電

+關注

關注

44文章

5755瀏覽量

169806 -

晶圓代工

+關注

關注

6文章

868瀏覽量

49209 -

汽車芯片

+關注

關注

10文章

937瀏覽量

44037

原文標題:臺積電正在研究的先進技術

文章出處:【微信號:半導體科技評論,微信公眾號:半導體科技評論】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子與臺積電合作推動半導體設計與集成創新 包括臺積電N3P N3C A14技術

臺積電披露:在美國大虧 在大陸大賺 臺積電在美投資虧400億臺幣

全球芯片產業進入2納米競爭階段:臺積電率先實現量產!

臺積電加速美國先進制程落地

臺積電擴大先進封裝設施,南科等地將增建新廠

臺積電設立2nm試產線

臺積電2025年起調整工藝定價策略

臺積電熊本工廠正式量產

臺積電CoWoS封裝A1技術介紹

臺積電又在探索哪些新技術?

臺積電又在探索哪些新技術?

評論