1 概述

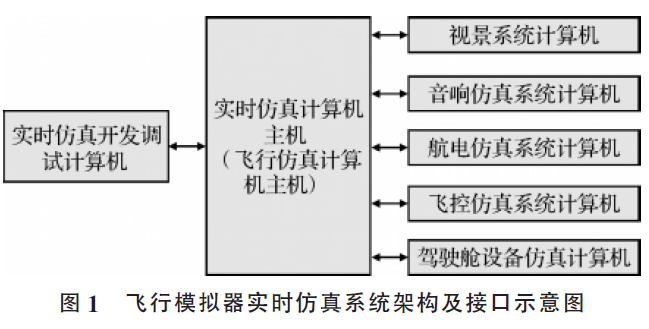

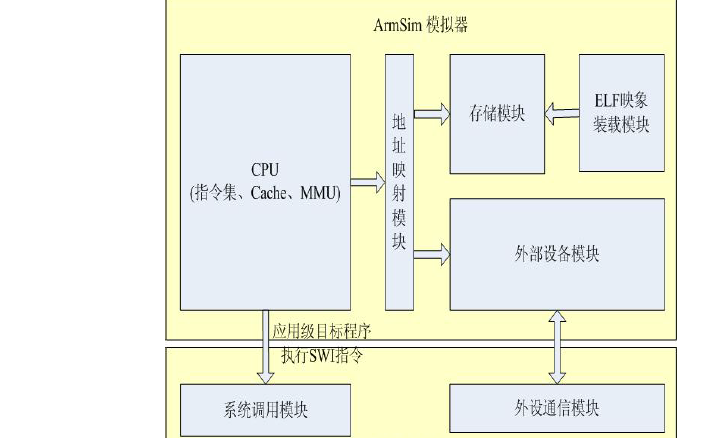

軟硬件協(xié)同驗(yàn)證的概念已經(jīng)提出多年,但是直到這些年隨著SOC技術(shù)的發(fā)展,軟硬件協(xié)同驗(yàn)證技術(shù)才得到更多的關(guān)注和重視,并得到發(fā)展。軟硬件協(xié)同驗(yàn)證是一種在硬件流片封裝之前,驗(yàn)證SOC系統(tǒng)硬件和軟件是否能夠正確工作的技術(shù)。協(xié)同驗(yàn)證又可以叫作虛擬原型技術(shù),因?yàn)橛布糠值?a target="_blank">仿真雖然跟真實(shí)硬件的運(yùn)行基本一樣,但是硬件仿真其實(shí)是通過在工作站上的一個軟件程序的運(yùn)行來實(shí)現(xiàn)的。協(xié)同驗(yàn)證的基本框架如圖1所示。

對比傳統(tǒng)的驗(yàn)證方法,協(xié)同驗(yàn)證技術(shù)使得軟件設(shè)計工程師能夠在設(shè)計早期進(jìn)行調(diào)試,可以較早的進(jìn)行軟硬件的整合,縮短上市時問(time-to-market)。另一方面,通過軟硬件協(xié)同驗(yàn)證,可以為硬件設(shè)計工程師提供了一整套非常接近于現(xiàn)實(shí)的激勵集,有利用于提高驗(yàn)證的質(zhì)量。

協(xié)同驗(yàn)證系統(tǒng)由一個硬件執(zhí)行環(huán)境和一個軟件執(zhí)行環(huán)境組成,通過事件和命令,使用一些機(jī)制,在這兩個環(huán)境間進(jìn)行控制。軟件的執(zhí)行環(huán)境用于產(chǎn)生總線周期的序列,協(xié)同驗(yàn)證工具將總線周期轉(zhuǎn)換成許多信號事件或者命令集,并驅(qū)動這些信號事件命令進(jìn)入硬件執(zhí)行環(huán)境,然后對總線周期響應(yīng)進(jìn)行硬件環(huán)境取樣,這一響應(yīng)又被傳送回軟件環(huán)境。同時,保持硬件及軟件環(huán)境問的同步以便硬件或軟件環(huán)境都可發(fā)現(xiàn)由于錯失響應(yīng)而導(dǎo)致有誤的情形。

軟硬件協(xié)同驗(yàn)證中,軟硬件部分都是通過建模的方式實(shí)現(xiàn)。其中硬件建模方式有如下幾種:采用FPGA原型或模擬系統(tǒng);采用HDL及邏輯仿真器;采用高級程序語言(如C/C++語言)編寫的行為模型。軟件也可通過幾種方式執(zhí)行:采用ISS(指令集仿真器)在CPU上運(yùn)行;通過編譯,并在運(yùn)行仿真程序的主機(jī)上運(yùn)行。在一般的SOC設(shè)計中,硬件建模一般用硬件描述語言來實(shí)現(xiàn),軟件一般需要編譯成針對SOC硬件嵌入式核的目標(biāo)代碼,因此在本文中,將采用指令級模擬器加邏輯仿真器(ISS with logicsimulator)的方法來構(gòu)建協(xié)同驗(yàn)證環(huán)境。

2 進(jìn)程間通信

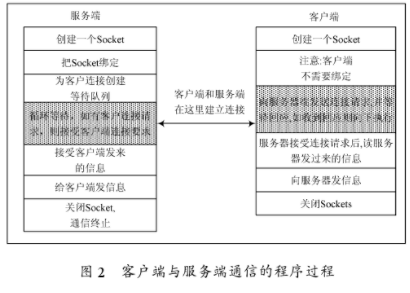

軟硬件仿真器之間的通信是協(xié)同驗(yàn)證中的關(guān)鍵技術(shù)。由于軟件仿真和硬件仿真使用獨(dú)立的兩個進(jìn)程,因此可以使用Unix下的進(jìn)程間通信(Inter Process Communication,IPC)技術(shù)來實(shí)現(xiàn)軟硬件仿真器之間的信息交互。常用的幾種Unix IPC有無名管道,有名管道(FIFO)和Unix套接字(Socket)。無名管道是Unix中最常用的IPC方式,優(yōu)點(diǎn)是非常簡潔,弱點(diǎn)是他只能在相關(guān)的,有共同祖先的進(jìn)程間使用;有名管道(FIFO)和無名管道的區(qū)別在于他是持久穩(wěn)定的,而且可以讓無任何關(guān)聯(lián)的進(jìn)程問交換數(shù)據(jù);套接字是一種抽象數(shù)據(jù)結(jié)構(gòu),用以創(chuàng)建一條在沒有關(guān)聯(lián)的進(jìn)程間發(fā)送、接收消息的通道(連接點(diǎn)),一旦通道建立之后,被連接起來的進(jìn)程就可以通過普通的文件系統(tǒng)存取例程來進(jìn)行通信了。在通信的兩方中,一方稱為客戶程序(client),另一方稱為服務(wù)程序(server)。建立過程如圖2所示。對比上述3種通信方式的特點(diǎn),這里使用UnixSocket來實(shí)現(xiàn)兩個進(jìn)程間的通信。

3 消息傳遞

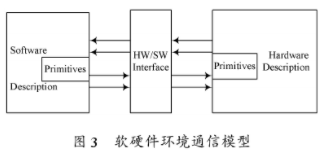

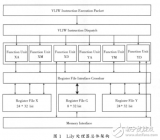

在本環(huán)境中,軟硬件間的通信可以看作是一個消息傳遞的過程,在軟件環(huán)境和硬件環(huán)境中添加數(shù)據(jù)傳輸函數(shù),并通過接口實(shí)現(xiàn)信息交互,如圖3所示。

在兩個進(jìn)程消息傳遞的過程中,消息可以分為3類:同步的數(shù)據(jù)傳輸;異步的數(shù)據(jù)傳輸;無數(shù)據(jù)傳輸?shù)耐叫盘枴M降臄?shù)據(jù)傳輸是指在一種機(jī)制下,保證在發(fā)送端進(jìn)程發(fā)送數(shù)據(jù)時,接收端進(jìn)程處在正確的狀態(tài);如果發(fā)送端進(jìn)程發(fā)起一次數(shù)據(jù)傳輸時,接收端不處在合適的狀態(tài),發(fā)送端則阻塞這次傳輸直到接收端準(zhǔn)備好。異步的數(shù)據(jù)傳輸是指發(fā)送端進(jìn)程在發(fā)送數(shù)據(jù)時,不考慮這次數(shù)據(jù)或者前一次的數(shù)據(jù)是否被接收端接收到,數(shù)據(jù)沒有緩沖,每次新發(fā)送的數(shù)據(jù)都會覆蓋前一次的數(shù)據(jù),因此,在一次傳輸中,數(shù)據(jù)可能被接收多次或者接收不到。通常這種傳輸用來傳遞狀態(tài)信息。無數(shù)據(jù)傳輸?shù)耐叫盘枺脕硗絻蓚€進(jìn)程的狀態(tài),沒有數(shù)據(jù)的交換。一個進(jìn)程可使用同步信號來通知另外一個進(jìn)程開始一次任務(wù)或者等待其完成一次任務(wù)。

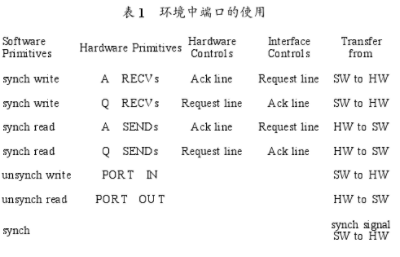

軟件環(huán)境和硬件環(huán)境中數(shù)據(jù)傳輸函數(shù)與接口間的通信方式是不同的。在軟件環(huán)境中,數(shù)據(jù)傳輸函數(shù)只包括簡單的讀寫操作,讀寫操作分為同步和異步兩種模式。在硬件環(huán)境中,需要定義一些端口來控制數(shù)據(jù)傳輸,每一個端口使用不同的協(xié)議。進(jìn)行同步數(shù)據(jù)傳輸時,在硬件環(huán)境中使用握手端口,同時與軟件環(huán)境中的同步讀寫函數(shù)配合。握手端口共有4個,分為兩個SENDs(數(shù)據(jù)從硬件環(huán)境到接口)和兩個RECVs(數(shù)據(jù)從接口到硬件環(huán)境)。每個SENDs,RECVs又根據(jù)硬件環(huán)境是請求方還是應(yīng)答方分為Q_SENDs,Q_RECVs和A_SENDs,A_RECVs。進(jìn)行異步的數(shù)據(jù)傳輸時,在硬件環(huán)境中定義兩個端口PORT_IN和PORT_OUT,與軟件環(huán)境中的異步讀寫函數(shù)配合進(jìn)行傳輸。另外,需要定義一個EVENT端口,發(fā)送無數(shù)據(jù)傳輸?shù)耐叫盘枺脕硗杰浖h(huán)境和硬件環(huán)境的仿真時間。

表1中總結(jié)了在接口中端口的使用。在這個協(xié)同驗(yàn)證環(huán)境中,通過這些端口的使用,設(shè)計者可以忽略底層細(xì)節(jié),有選擇的使用以上端口來實(shí)現(xiàn)軟硬件之間信息交互。

4 協(xié)同驗(yàn)證環(huán)境的實(shí)現(xiàn)

4.1 基本構(gòu)架

整個環(huán)境的基本構(gòu)架如圖4所示,左右兩個框分別表示軟件仿真進(jìn)程和硬件仿真進(jìn)程,他們之間通過UnixSockets交換信息,Verilog PLI是他們交互的接口。下面對環(huán)境的各個部分進(jìn)行介紹。

在軟件環(huán)境中,指令級模擬器(ISS)是一種仿真CPU行為的程序,他在主機(jī)上運(yùn)行,可以仿真軟件程序的可執(zhí)行鏡像。把SOC軟件編譯成針對SOC硬件嵌入式核的目標(biāo)代碼后,即可在指令級模擬器上仿真。C的總線模型(C BFM)用來實(shí)現(xiàn)指令級到周期級的轉(zhuǎn)換,并實(shí)現(xiàn)總線接口功能,與硬件環(huán)境相連接,同時還包含了Unix Sockets的服務(wù)程序。

硬件環(huán)境包含2部分。一部分是Verilog PLI Inter-face。他是軟件和硬件交互的接口,一方面通過UnixSockets的客戶程序與軟件環(huán)境交互信息;一方面通過一些任務(wù)函數(shù),根據(jù)Sockets傳遞過來的信息,向硬件發(fā)出請求或者應(yīng)答信號。另一部分是待驗(yàn)證的硬件模型,用Ver-ilog描述,他的外圍是一段控制程序(verilog controlstub),在仿真的每一個時刻調(diào)用PLI中的函數(shù),通過端口與Verilog PLI Interface交互信息。

4.2 功能實(shí)現(xiàn)

圖5給出了軟硬件環(huán)境通過A_RECV端口實(shí)現(xiàn)通信的例子。

當(dāng)軟件需要向硬件寫入一個數(shù)據(jù)時,首先通過Socket將數(shù)據(jù)發(fā)送給PLI;PLI接收數(shù)據(jù),同時拉高請求線,向硬件發(fā)出請求;硬件模型得到清求后,通過Verilog ControlStub接收數(shù)據(jù),傳遞給內(nèi)部寄存器,并拉高應(yīng)答線,向PLI發(fā)出應(yīng)答。PLI得到應(yīng)答后拉低請求線,同時發(fā)出同步信號給Socket,硬件模型得到拉低的請求后,拉低應(yīng)答線,一次傳輸結(jié)束。當(dāng)軟件需要進(jìn)行下一次寫操作時,首先需要通過Socket讀取同步信號,有同步信號時即可開始下一次操作。其他的端口握手過程與此類似。

4.3 協(xié)同模擬同步

指令集模擬器以指令為單位進(jìn)行模擬,時鐘每次推進(jìn)一個指令周期,指令周期長度則隨指令的不同而不同。硬件模擬器通常采用事件驅(qū)動模擬算法,他以事件為調(diào)度對象,硬件模擬器按照事件發(fā)生的時間進(jìn)度推進(jìn)時鐘,時間單位一般由用戶的設(shè)計指定,例如納秒,微秒等。因此必須采用一定的機(jī)制對二者進(jìn)行同步,并且他們之間能否同步將直接影響到協(xié)同模擬的正確性。指令集模擬器和硬件模擬器之間通常采用Lock-step方式進(jìn)行同步。采用該同步方式必須首先確定同步點(diǎn),保證在兩個同步點(diǎn)之間的時間間隔內(nèi)不發(fā)生軟硬件交互事件。如前文所述,Verilog PLIInterface是軟硬件模擬器之間的信息交換界面,所以同步點(diǎn)會因?yàn)榻换バ畔⒌牟粏柖煌6布M器是以事件發(fā)生的時間順序推進(jìn)時鐘,要保證其時鐘不會越過同步點(diǎn),就必須引入同步信號,即時間為同步點(diǎn)的信號,硬件模擬器完成一個事件后,需要向Verilog PLI Interface發(fā)回一個同步信息,說明硬件模擬器的時鐘己推進(jìn)到同步點(diǎn)。

5 結(jié) 語

設(shè)計驗(yàn)證是SOC設(shè)計的關(guān)鍵技術(shù)之一,貫穿整個SOC技術(shù),隨著SOC技術(shù)的發(fā)展,軟硬件協(xié)同驗(yàn)證技術(shù)得到了更多的關(guān)注和重視。與過去把整個環(huán)境當(dāng)作單一的一個進(jìn)程處理的方法不同,本環(huán)境將軟硬件仿真的過程分離開來,使用Unix Sockets來實(shí)現(xiàn)軟硬件之間的通信,更接近實(shí)際情況。同時,由于兩個仿真過程并行執(zhí)行,仿真速度更快,效率更高。在該環(huán)境中,軟件用編程語言來編寫,硬件用硬件描述語言來建模,符合一般軟硬件工程師的習(xí)慣,較早的進(jìn)行軟硬件的整合。在此環(huán)境中,軟硬件之間通信的吞吐量是影響仿真速度的瓶頸,下一步作者將針對協(xié)同模擬同步及優(yōu)化進(jìn)行研究。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618619 -

仿真器

+關(guān)注

關(guān)注

14文章

1037瀏覽量

85420 -

模擬器

+關(guān)注

關(guān)注

2文章

894瀏覽量

44416

發(fā)布評論請先 登錄

為什么需要仿真器

什么是功率級電機(jī)模擬器

LVGL模擬器該怎樣去搭建呢

ArmSim全系統(tǒng)模擬器的設(shè)計與實(shí)現(xiàn)

ARM指令集仿真器的設(shè)計與實(shí)現(xiàn)

DSP指令集仿真器的設(shè)計與實(shí)現(xiàn)

仿真器和模擬器的不同_仿真器和模擬器的區(qū)別簡單分析

如何使用MATLAB RTW和Vxworks實(shí)現(xiàn)飛行模擬器的實(shí)時仿真

使用ARM處理器設(shè)計實(shí)現(xiàn)全系統(tǒng)模擬器ArmSim的詳細(xì)資料說明

千兆級電路仿真器NanoSpice Giga實(shí)現(xiàn)比FastSPICE仿真器更快速度

PDSDK COM 套件參考手冊(仿真器/模擬器調(diào)試器定制套件)

PDSDK COM 套件參考手冊(仿真器/模擬器調(diào)試器定制套件)

基于指令級模擬器加邏輯仿真器實(shí)現(xiàn)協(xié)同驗(yàn)證環(huán)境的搭建

基于指令級模擬器加邏輯仿真器實(shí)現(xiàn)協(xié)同驗(yàn)證環(huán)境的搭建

評論