模數(shù)轉(zhuǎn)換器(ADC)中的采樣可能會引起混疊和電容反沖問題,為了解決這些問題,設(shè)計人員會在電路中使用濾波器和驅(qū)動放大器,但同時也會給在中等帶寬應(yīng)用領(lǐng)域中實現(xiàn)精確的直流和交流性能帶來挑戰(zhàn),設(shè)計人員可能最終為此犧牲系統(tǒng)目標。

本文將會從采樣技術(shù)的基礎(chǔ)知識說起,重溫模數(shù)轉(zhuǎn)換的基本運作方式,并幫助大家理解現(xiàn)實中會遇到的問題。在接下來的后一篇文章中,我們會進一步介紹如何通過連續(xù)時間Σ-Δ ADC簡化信號鏈,有效地解決采樣中遇到的問題。

采樣基礎(chǔ)

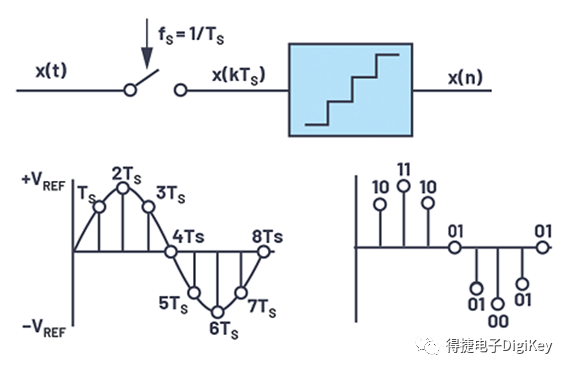

數(shù)據(jù)數(shù)字化涉及采樣和量化這兩個基本過程,如圖1所示。采樣是第一步,其是使用采樣頻率fS將連續(xù)時間變化的模擬信號x(t)轉(zhuǎn)換為離散時間信號x(n)。結(jié)果得出平均間隔的信號為1/ TS(fS = 1/ TS)。

圖1:數(shù)據(jù)采樣 (圖片來源: ADI)

第二步是量化,即將這些離散時間樣本的值估算為一個有限的可能值,并以數(shù)字代碼表示,如圖1所示。量化為一組有限值會導致數(shù)字化錯誤,稱為量化噪聲。

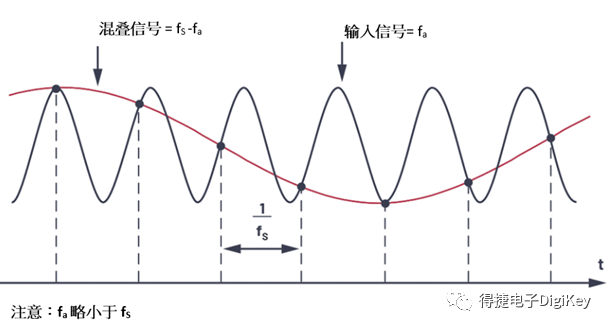

采樣過程也會導致混疊。在混疊中,我們會看到輸入信號折返及其在采樣與保持時鐘頻率周圍出現(xiàn)諧波。奈奎斯特準則要求采樣頻率必須至少是最高信號頻率的兩倍。如果采樣頻率小于最大模擬信號頻率的兩倍,將會發(fā)生稱為混疊的現(xiàn)象。為了理解混疊在時域和頻域中的含義,首先要考慮如圖2所示采樣的單信號正弦波的時域表示形式。

圖2 :混疊的時域表示 (圖片來源: ADI)

在這個示例中,采樣頻率fS較模擬輸入頻率fa 僅略高,但不多于fa 兩倍,因此不符合奈奎斯特準則。值得留意的是,實際樣本的模式會產(chǎn)生較低的頻率(等于fS -fa)的混疊正弦波。這種情況的相應(yīng)頻域表示如圖3所示。

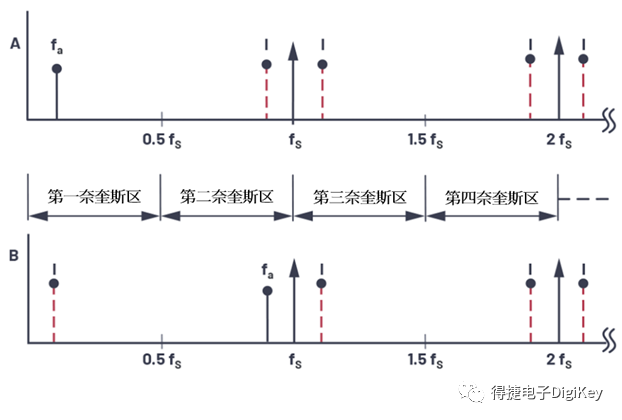

圖3:混疊的頻域表示 (圖片來源: ADI)

奈奎斯特帶寬定義為從直流到fS / 2的頻譜。頻譜被劃分為無數(shù)個奈奎斯特區(qū),每個區(qū)的寬度等于0.5fS。實際上,理想的采樣器由ADC和FFT處理器來代替。FFT處理器僅提供從直流到fS/ 2的輸出;即是出現(xiàn)在第一個奈奎斯特區(qū)域中的信號或混疊。

如果采用理想的脈沖采樣器,在頻率fS下對頻率fa 的單頻正弦波進行采樣,如圖1所示。另外假設(shè)fS 》2fa。采樣器的頻域輸出顯示,每一個fS倍頻附近均會出現(xiàn)原始信號的混疊或鏡像。也就是說,在|± K fS± fa | 的頻率處,K = 1、2、3、4等。

之后,考慮在圖3中第一個奈奎斯特區(qū)域之外的信號情況。信號頻率僅略小于采樣頻率,與圖2時域表示中所示的條件相對應(yīng)。請注意,即使信號在第一個奈奎斯特區(qū)域之外,其鏡像(或混疊)fS – fa 仍在該區(qū)內(nèi)。回到圖3,如果一個不想要的信號出現(xiàn)在fa 的任何鏡像頻率上,它也將會出現(xiàn)在fa上,從而在第一奈奎斯特區(qū)中產(chǎn)生一個雜散頻率成分。

設(shè)計挑戰(zhàn)

對于高性能應(yīng)用,系統(tǒng)設(shè)計人員需要解決由采樣過程引起的量化噪聲、混疊和開關(guān)電容輸入采樣問題。工業(yè)應(yīng)用中常見有兩種類型的精密ADC,分別是逐次逼近寄存器(SAR)和Σ-Δ ADC,它們都是采用基于開關(guān)電容的采樣技術(shù)設(shè)計的。

量化噪聲

在理想的奈奎斯特 ADC中,ADC的LSB大小將決定在進行模數(shù)轉(zhuǎn)換時添加到輸入的量化噪聲。該量化噪聲分布在fS / 2的帶寬范圍內(nèi)。為了解決量化噪聲問題,可以考慮過采樣技術(shù),即以遠高于奈奎斯特頻率的速率對輸入信號進行采樣,以提高信噪比(SNR)和分辨率(ENOB)。在過采樣中,使用采樣頻率為奈奎斯特頻率(2 × fIN )的N倍,因此必須使相同的量化噪聲分布在N倍奈奎斯特頻率范圍內(nèi)。這也放寬了對抗混疊濾波器的要求。過采樣率(OSR)定義為fS/ 2 fIN ,其中fIN 是目標信號帶寬。作為一般準則,對ADC進行四倍的過采樣可以額外提供1位分辨率,或者增加6 dB的動態(tài)范圍。增加過采樣率將導致整體噪聲降低,并增加動態(tài)范圍(DR),過采樣為ΔDR= 10log10 OSR,以dB為單位。

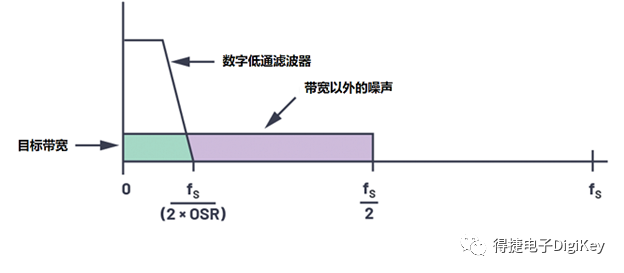

過采樣在本質(zhì)上與集成的數(shù)字濾波器和抽取功能一起使用和實現(xiàn)。Σ-Δ ADC中的基本過采樣調(diào)制器對量化噪聲進行整形,使其大部分出現(xiàn)在目標帶寬之外,從而導致低頻處的整體動態(tài)范圍增大,如圖4所示。然后,數(shù)字低通濾波器(LPF)然后濾除目標帶寬以外的量化噪聲,抽取器將輸出數(shù)據(jù)速率降低,使其回落至奈奎斯特速率。

圖4 :過采樣示例 (圖片來源: ADI)

噪聲整形是另一種減少量化噪聲的技術(shù)。在Σ-Δ ADC中,在環(huán)路濾波器之后的環(huán)路內(nèi)使用低分辨率量化器(一位至五位)。DAC用作反饋,從輸入中減去量化信號。圖5:噪聲整形 (圖片來源: ADI)

積分器持續(xù)將量化誤差加起來,從而將量化噪聲整形至更高頻率,然后可以使用數(shù)字濾波器對其進行濾波。圖6說明了典型Σ-Δ ADC輸出x[n]的功率譜密度(PSD)。噪聲整形斜率取決于環(huán)路濾波器H(z)的階數(shù),每十倍頻程為(20 × n)dB,其中n是環(huán)路濾波器的階數(shù)。通過結(jié)合使用噪聲整形和過采樣,Σ-Δ ADC可實現(xiàn)帶內(nèi)高分辨率。帶內(nèi)帶寬等于fODR / 2(ODR代表輸出數(shù)據(jù)速率)。通過增加環(huán)路濾波器的階數(shù)或增加過采樣率,可以獲得更高的分辨率。

混疊現(xiàn)象

為了在高性能的應(yīng)用中消除混疊,使用更高階的抗混疊濾波器來避免任何數(shù)量的混疊。抗混疊濾波器是一種低通濾波器,其帶寬會限制輸入信號,并確保信號中沒有超出可以折返的目標帶寬的頻率分量。濾波器的性能將取決于帶外信號與fS / 2的接近程度以及所需的衰減量。

對于SAR ADC,輸入信號帶寬和采樣頻率之間的差距并不大,因此我們需要一個更高階濾波器,這會是一個更復(fù)雜、更高功率和更大失真的高階濾波器設(shè)計。例如,如果200 kSPS采樣速度SAR的輸入帶寬為100 kHz,則抗混疊濾波器將需要拒絕大于100 kHz的輸入信號,以確保沒有混疊。這需要使用非常高階的濾波器。

如果選擇400 kSPS的采樣速度來降低濾波器的階數(shù),則需要抑制》 300 kHz的輸入頻率。增加采樣速度將增加功率,如果想實現(xiàn)雙倍速度,需要的功率也將增加一倍。由于采樣頻率遠高于輸入帶寬,因此以功率為代價的進一步過采樣將進一步降低抗混疊濾波器的要求。

在Σ-Δ ADC中,輸入以更高的OSR進行過采樣,由于采樣頻率遠高于輸入帶寬,因而降低了抗混疊濾波器的要求。

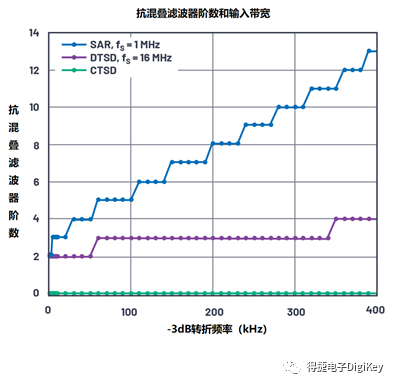

圖9顯示SAR和離散時間Σ-Δ(DTSD)架構(gòu)中抗混疊濾波器復(fù)雜度的程度。如果我們采用100 kHz的 -3dB輸入帶寬在采樣頻率fS下實現(xiàn)102 dB衰減,則DTSD ADC將需要使用二階抗混疊濾波器,而采用SAR ADC在fS下獲得相同的衰減,則需要使用五階濾波器。對于連續(xù)時間Σ-Δ(CTSD)ADC,衰減是固有的,因此我們不需要使用任何抗混疊濾波器。

圖9 :各種架構(gòu)的抗混疊濾波器要求 (圖片來源: ADI)

這些濾波器對系統(tǒng)設(shè)計人員來說可能是一道難題,它們必須優(yōu)化這些濾波器的設(shè)計,以便在目標頻帶內(nèi)提供衰減,并盡可能提供更高的抑制性能。它們還會給系統(tǒng)增加許多其他誤差,例如失調(diào)、增益、相位誤差和噪聲,從而降低其性能。同樣,高性能ADC本質(zhì)是差分的,因此我們需要兩倍數(shù)量的無源組件。為了在多通道應(yīng)用中獲得更好的相位匹配,信號鏈中的所有組件都必須匹配良好,即需要使用公差更嚴格的組件。

ADC選料上的考慮

工程師要選擇一款合適的模數(shù)轉(zhuǎn)換器(ADC),要了解轉(zhuǎn)換器的關(guān)鍵參數(shù)項。如上文所述,它們包括「位數(shù)」、「采樣率」或「輸入數(shù)」的要求,轉(zhuǎn)換「架構(gòu)」的選擇(SAR、三角積分…),甚至于「輸入類型」的選項(單端、差分… )等,以及參數(shù)項互相的影響或補充。如工程師手上能擁有一個能夠概括大部份主要參數(shù)項的篩選列表,在篩選中還能清楚表達各選項在市場上的普遍程度,且能夠靈活地加減篩選項,這一定會提升選料效率。

本文小結(jié)

本文中,我們首先重溫了模數(shù)轉(zhuǎn)換器的基礎(chǔ)運作原理。接下來介紹了如何通過Σ-Δ ADC來簡化信號鏈,有效地解決采樣問題。這種方法,消除了對抗混疊濾波器和緩沖器的需求,并解決了信號鏈偏移誤差和與其他組件相關(guān)的漂移問題。這些設(shè)計的好處包括:可縮小解決方案的尺寸,簡化設(shè)計,并改善系統(tǒng)的相位匹配和整總體延遲。此外, Digi-Key官網(wǎng)中的「數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器(ADC)」產(chǎn)品的參數(shù)篩選列表清晰易用,可以方便工程師快速完成ADC的選料。

責任編輯:haq

-

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174547 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8970瀏覽量

150883 -

adc

+關(guān)注

關(guān)注

99文章

6649瀏覽量

548371

原文標題:全程干貨!ADC采樣中的信號鏈設(shè)計挑戰(zhàn)

文章出處:【微信號:得捷電子DigiKey,微信公眾號:得捷電子DigiKey】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

ADC采樣率與信號頻率:關(guān)鍵概念與設(shè)計要點

ADC技術(shù)在信號處理中的應(yīng)用

ADC108S102采樣時,輸入信號有毛刺怎么解決?

高速ADC設(shè)計中采樣時鐘影響的考量

adc最新技術(shù)趨勢與發(fā)展

如何優(yōu)化adc的采樣率

位深和采樣率在數(shù)采系統(tǒng)中的作用詳解

采樣頻率和信號頻率之間的關(guān)系

ADC采樣保持電路的工作原理和技術(shù)指標

基于TI射頻直接采樣ADC(ADC32RF80)的RX鏈路設(shè)計

ADC中采樣技術(shù)的信號鏈設(shè)計挑戰(zhàn)

ADC中采樣技術(shù)的信號鏈設(shè)計挑戰(zhàn)

評論