全加器英語名稱為full-adder,是用門電路實(shí)現(xiàn)兩個(gè)二進(jìn)制數(shù)相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進(jìn)位,并輸出本位加法進(jìn)位,多個(gè)一位全加器進(jìn)行級(jí)聯(lián)可以得到多位。

全加器是形成三位算術(shù)和的組合電路,它由三個(gè)輸入和兩個(gè)輸出組成。

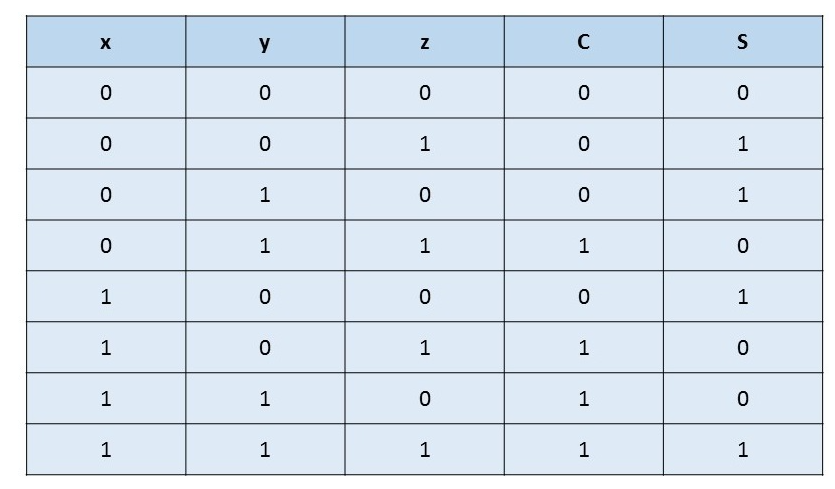

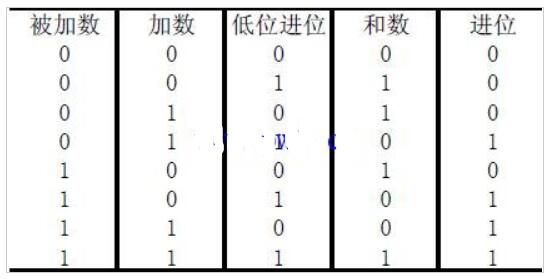

真值表

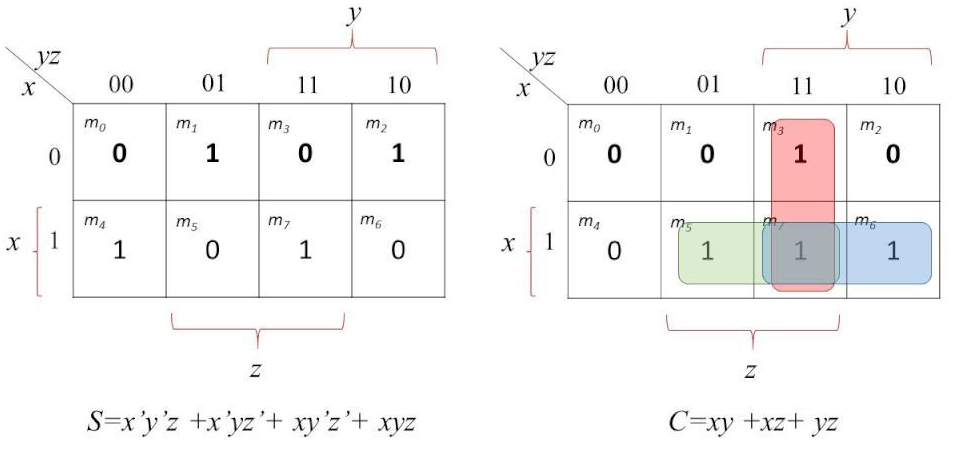

a.) 基于真值表,S 和 C 的卡諾圖如下:

S 和 C 的 K 映射

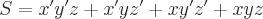

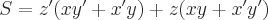

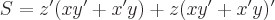

b.) S 輸出可以減少為:

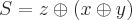

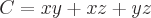

進(jìn)位輸出 C 為:

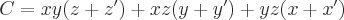

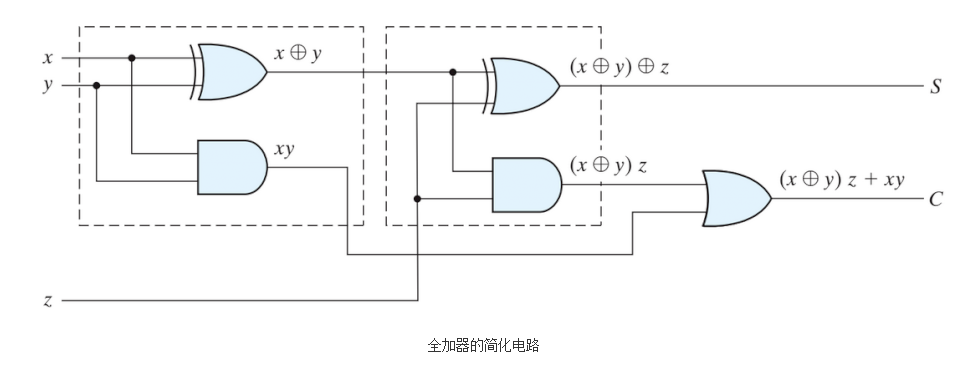

全加器的簡(jiǎn)化電路

邏輯電路變成了兩個(gè)級(jí)聯(lián)的半加器和一個(gè)或門。

文章來源:eeweb avon ampo

編輯:ymf

-

全加器

+關(guān)注

關(guān)注

10文章

62瀏覽量

28815 -

二進(jìn)制數(shù)

+關(guān)注

關(guān)注

0文章

12瀏覽量

7853 -

組合電路

+關(guān)注

關(guān)注

0文章

11瀏覽量

6776

發(fā)布評(píng)論請(qǐng)先 登錄

怎么利用QuartuesII查元件真值表

怎么利用QuartusII查元件真值表

求常用單片機(jī)的功能表、引腳圖、真值表

關(guān)于多位輸入真值表的問題

輸入真值表相同 輸出結(jié)果不同 74HC138

LUT真值表在實(shí)施期間發(fā)生了變化

真值表,真值表是什么意思

與門真值表和與非門真值表的區(qū)別

全加器真值表解釋

看看全減器電路與Verilog

全加器的真值表

全加器的真值表

評(píng)論