電子發(fā)燒友網(wǎng)站提供《在Spartan 6 FPGA上從頭開(kāi)始實(shí)現(xiàn)全加器.zip》資料免費(fèi)下載

2023-06-15 10:13:28 0

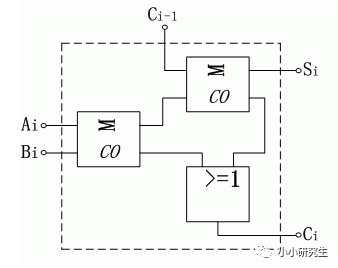

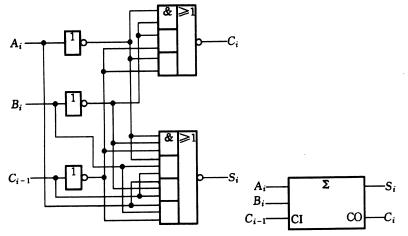

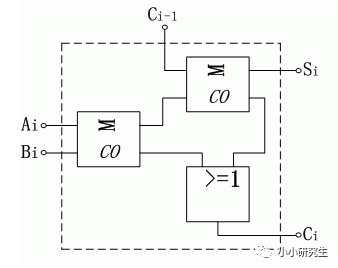

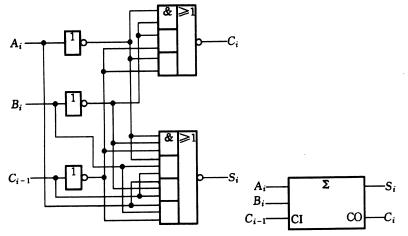

0 首先半加器是A+B構(gòu)成了{(lán)C,S}。由于全加器多了一個(gè)低位的進(jìn)位,就是將{C,S}再加上Ci-1。

2023-05-22 15:26:35 583

583

在上一節(jié)半加器中,介紹了全加器可看作兩個(gè)半加器和一個(gè)或門組成。

2023-05-14 15:07:47 837

837

注冊(cè)表解鎖方法1 編輯一個(gè)注冊(cè)表解鎖項(xiàng),加進(jìn)注冊(cè)表。 方法:新建記事本,輸入"REGEDIT4 [HKEY_CURRENT_USER

2008-06-03 17:49:32

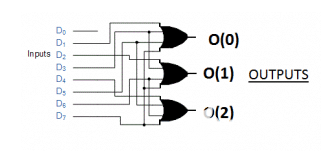

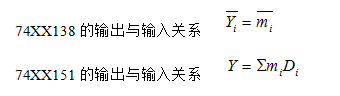

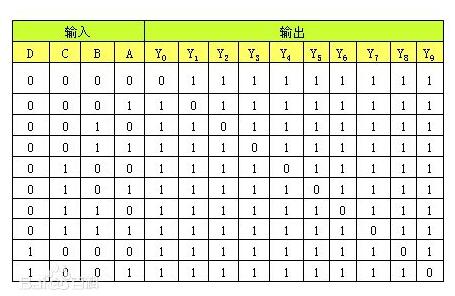

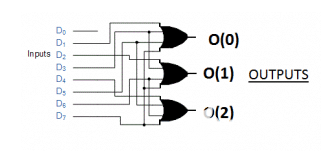

編碼器和解碼器是組合邏輯電路,在其中,主要借助布爾代數(shù)實(shí)現(xiàn)組合邏輯。今天就大家了解一下編碼器和解碼器電路,分別從定義,工作原理,應(yīng)用,真值表幾個(gè)方面講述一下。

2022-11-03 09:22:57 3470

3470

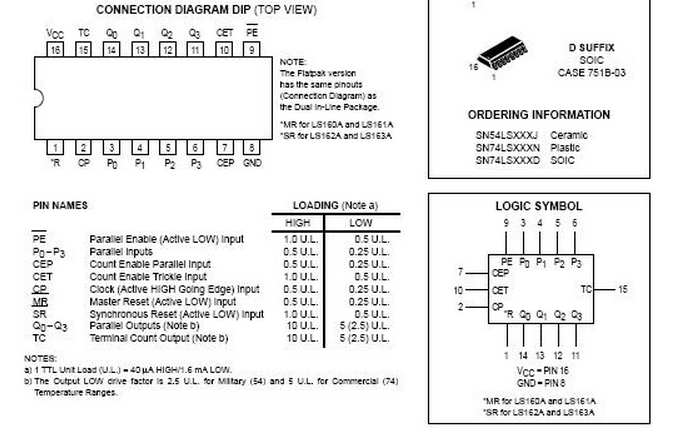

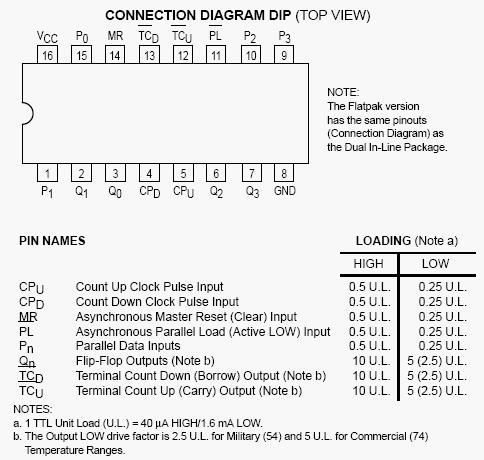

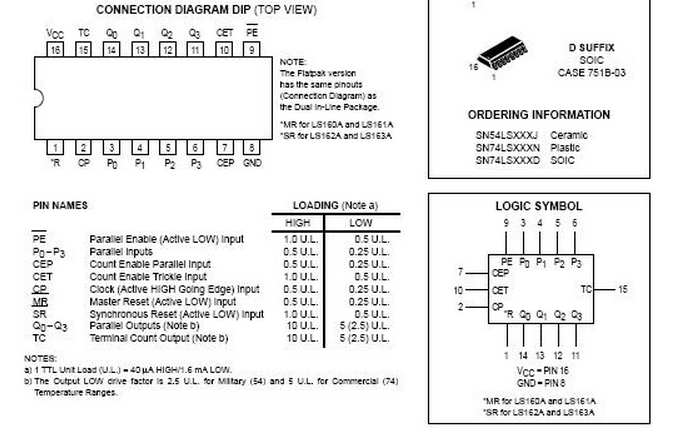

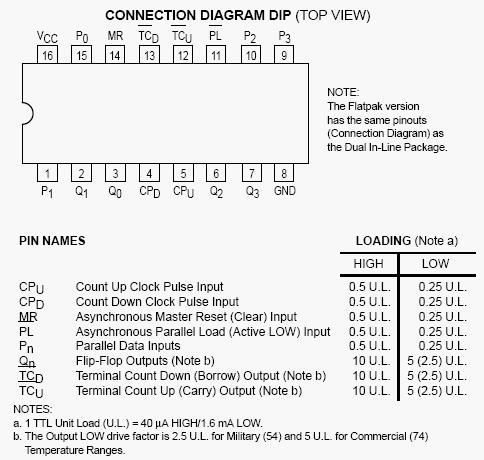

74ls160引腳圖管腳圖及功能真值表,74ls160引腳圖管腳圖74LS160的功能真值表-綜合電路圖 74ls160引腳圖管腳圖 ? 74LS160的功能真值表 ?

2022-05-25 16:39:14 102427

102427

Verilog數(shù)字系統(tǒng)設(shè)計(jì)四復(fù)雜組合邏輯實(shí)驗(yàn)2文章目錄Verilog數(shù)字系統(tǒng)設(shè)計(jì)四前言一、什么是8位全加器和8為帶超前進(jìn)位的全加器?二、編程1.要求:2.門級(jí)原語(yǔ)實(shí)現(xiàn)8位全加器:3.門級(jí)原語(yǔ)實(shí)現(xiàn)帶

2021-12-05 19:06:10 4

4 多思計(jì)算機(jī)組成原理網(wǎng)絡(luò)虛擬實(shí)驗(yàn)系統(tǒng)計(jì)算機(jī)組成原理實(shí)驗(yàn)一全加器實(shí)驗(yàn)

2021-10-22 10:36:12 11

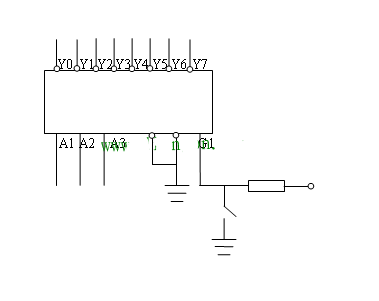

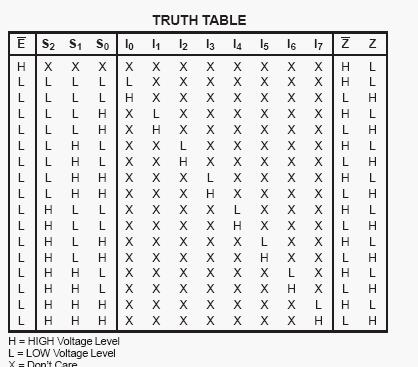

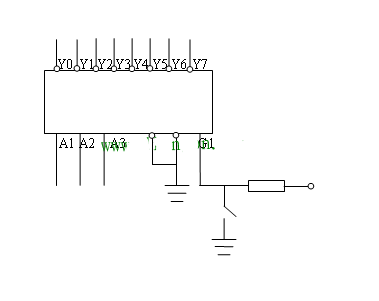

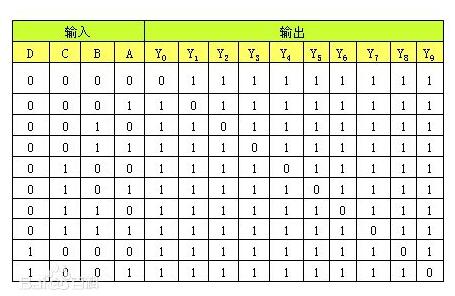

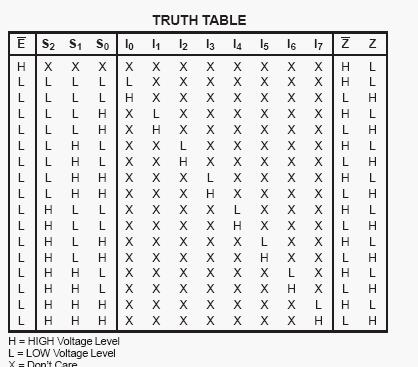

11 38譯碼器也就是三線八線譯碼器,那么38譯碼器真值表以及功能與原理是什么呢,下面小編就為大家來(lái)帶38譯碼器真值表以及功能與原理。 三線八線譯碼器的三線是指三位二進(jìn)制數(shù)字,其會(huì)組成000到111共八個(gè)

2021-07-08 15:55:54 97073

97073

全加器英語(yǔ)名稱為full-adder,是用門電路實(shí)現(xiàn)兩個(gè)二進(jìn)制數(shù)相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進(jìn)位,并輸出本位加法進(jìn)位,多個(gè)一位全加器進(jìn)行級(jí)聯(lián)可以得到多位。全加器是形成三位算術(shù)和的組合電路,它由三個(gè)輸入和兩個(gè)輸出組成。

2021-06-29 09:14:46 53586

53586

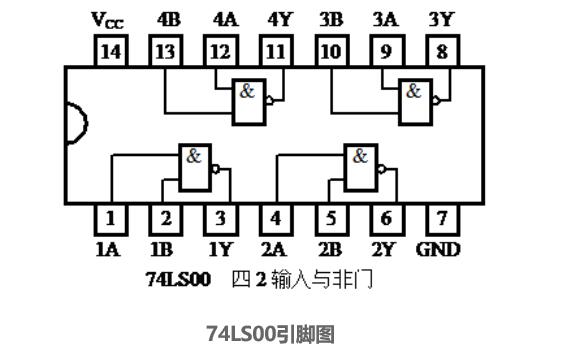

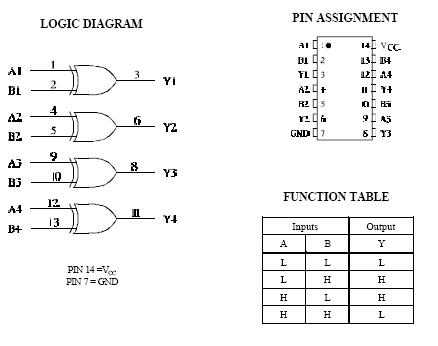

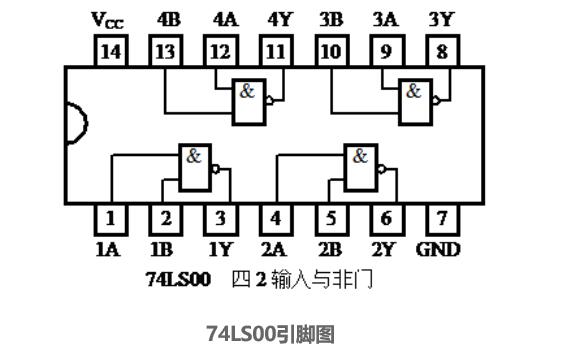

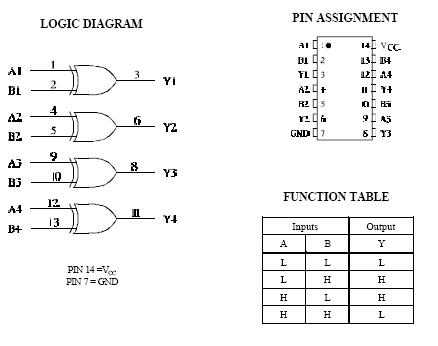

本文主要介紹74ls00引腳圖及功能、真值表和特性參數(shù)。

2021-06-16 16:02:03 150922

150922

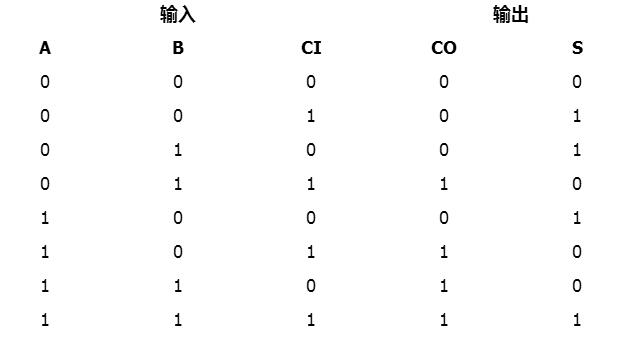

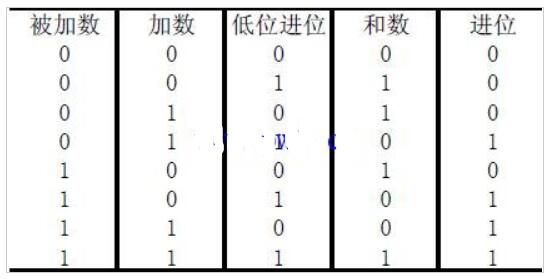

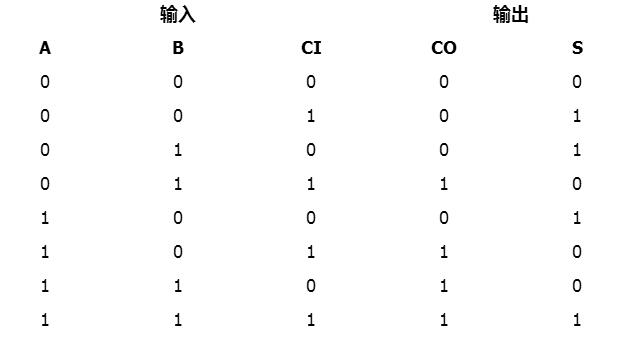

全加器的輸入端有三個(gè),分別為A、B、C(低位的進(jìn)位);兩個(gè)輸出S(和);C(運(yùn)算產(chǎn)生的進(jìn)位)。

2020-04-23 09:59:42 96058

96058

本文主要介紹了全加器邏輯表達(dá)式及全加器的邏輯功能。

2020-04-23 09:51:14 105979

105979

全加器是數(shù)字信號(hào)處理器微處理器中的重要單元,它不僅能完成加法,還能參與減法、乘法、除法等運(yùn)算,所以,。提高全加器性能具有重要意義。本文分析了兩種普通全加器,運(yùn)用布爾代數(shù)對(duì)全加器和的數(shù)、進(jìn)位函數(shù)進(jìn)行

2019-07-03 17:11:16 38

38 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL語(yǔ)言設(shè)計(jì)的全加器源代碼和工程文件免費(fèi)下載。

2019-06-03 08:00:00 4

4 全加器英語(yǔ)名稱為full-adder,是用門電路實(shí)現(xiàn)兩個(gè)二進(jìn)制數(shù)相加并求出和的組合線路,稱為一位全加器。

2018-07-25 16:03:28 73111

73111 半加器、全加器是組合電路中的基本元器件,也是CPU中處理加法運(yùn)算的核心,理解、掌握并熟練應(yīng)用是硬件課程的最基本要求。

2018-07-25 14:39:45 130197

130197

加器是能夠計(jì)算低位進(jìn)位的二進(jìn)制加法電路。與半加器相比,全加器不只考慮本位計(jì)算結(jié)果是否有進(jìn)位,也考慮上一位對(duì)本位的進(jìn)位,可以把多個(gè)一位全加器級(jí)聯(lián)后做成多位全加器。

2018-07-25 11:15:53 65775

65775

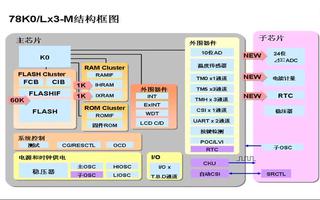

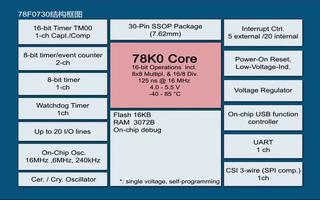

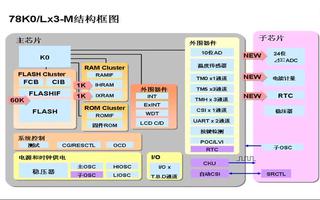

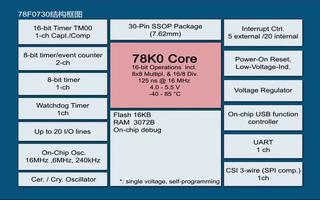

國(guó)網(wǎng)電能表解決方案

2018-07-23 00:34:00 4323

4323

插座表解決方案

2018-07-23 00:13:00 2610

2610

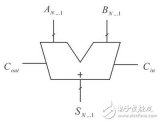

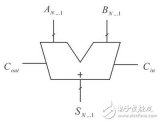

N位全加器將{AN,……,A1}、{BN,……,B1}和進(jìn)位輸入Cin作為輸入,計(jì)算得到和{SN,……,S1}以及最高位的進(jìn)位輸出Cout(見(jiàn)圖1)。每一位得到的和與進(jìn)位輸出都直接受其上一位的影響,其進(jìn)位輸出也會(huì)影響下一位。最終,整個(gè)全加器的和與輸出都受進(jìn)位輸入Cin的影響。

2018-06-08 10:24:00 3995

3995

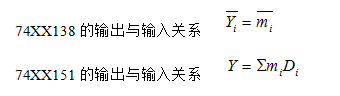

本文主要介紹了用74ls151實(shí)現(xiàn)全加器設(shè)計(jì)電路。根據(jù)全加器的定義可知:輸入為:A,B,Ci其中A,B為被加數(shù)和加數(shù),Ci為低位進(jìn)位數(shù)。輸出為:S,Co,其中S為本位和數(shù),Co為高位進(jìn)位數(shù)。其邏輯關(guān)系為:S=A⊕B⊕Ci;Co=AB+(A⊕B)Ci。

2018-05-07 09:52:22 106645

106645

本文主要介紹了邏輯真值表怎么列出的_真值表是怎么畫出來(lái)的。一個(gè)邏輯函數(shù)的卡諾圖就是將此函數(shù)的最小項(xiàng)表達(dá)式中的各最小項(xiàng)相應(yīng)地填入一個(gè)特定的方格圖內(nèi),此方格圖稱為卡諾圖。由A、B、C三個(gè)邏輯變量構(gòu)成

2018-04-09 11:45:02 218331

218331

與門真值表和與非門真值表的區(qū)別,與門真值表:有0出0,全1出1。與非門真值表:有0出1,全1出0。

2018-01-30 15:37:07 113692

113692

表征邏輯事件輸入和輸出之間全部可能狀態(tài)的表格。列出命題公式真假值的表。通常以1表示真,0 表示假。命題公式的取值由組成命題公式的命題變?cè)娜≈岛兔}聯(lián)結(jié)詞決定,命題聯(lián)結(jié)詞的真值表給出了真假值的算法。

2018-01-30 15:16:13 62364

62364

Avago Technologies智能儀表解決方案

2016-06-02 15:59:14 5

5 智能儀表解決方案 ,電力工業(yè)上要用到的PDF

2016-01-06 15:38:45 1

1 實(shí)驗(yàn)五 全加器、譯碼器及數(shù)碼顯示電路 一、實(shí)驗(yàn)?zāi)康?1、掌握全加器邏輯功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段譯碼器和七段數(shù)碼管顯示十進(jìn)制數(shù)的方法。 3、掌握

2012-07-16 23:01:22 37

37 本文旨在通過(guò)對(duì)恩智浦半導(dǎo)體智能電表解決方案的介紹,使大家對(duì)非接觸式預(yù)付費(fèi)智能表系統(tǒng)有一個(gè)整體的認(rèn)識(shí)。本文還對(duì)一些常見(jiàn)問(wèn)題做出了回答

2011-05-26 10:16:23 11015

11015

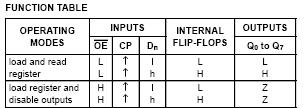

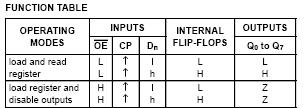

本文是74ls175的真值表及74ls175功能描述

2011-03-20 17:00:52 24846

24846

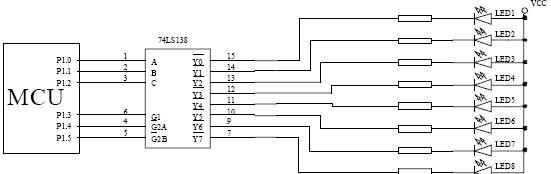

本資料有74ls138真值表_74ls138功能表。

2011-03-20 14:25:55 69

69 基于單電子晶體管的I-V特性和傳輸晶體管的設(shè)計(jì)思想,用多柵單電子晶體管作為傳輸晶體管,設(shè)計(jì)了一個(gè)由5個(gè)SET構(gòu)成的全加器,相對(duì)于靜態(tài)互補(bǔ)邏輯設(shè)計(jì)的全加器,本文設(shè)計(jì)的全加器在器

2010-07-30 16:54:22 18

18 什么是一位全加器,其原理是什么

加器是能夠計(jì)算低位進(jìn)位的二進(jìn)制加法電路

一位全加器由2個(gè)半加

2010-03-08 17:13:33 72422

72422 全加器,全加器是什么意思

full-adder 用門電路實(shí)現(xiàn)兩個(gè)二進(jìn)數(shù)相加并求出和的組合線路,稱為一個(gè)全加器。

2010-03-08 17:04:58 78218

78218 真值表,真值表是什么意思

把變量的各種可能取值與想對(duì)應(yīng)的函數(shù)值,用表格的形式一一列舉出來(lái),這種表格就叫做真值表。設(shè)一個(gè)變量均有0、1兩

2010-03-08 11:03:15 26920

26920 全加器

全加器能進(jìn)行加數(shù)、被加數(shù)和低位來(lái)的進(jìn)位信號(hào)相加,并根據(jù)求和結(jié)果給出該位的進(jìn)位信號(hào)。 根據(jù)全加器的功能,可列出它的真值表:

2009-04-07 10:34:54 8256

8256

74hc574功能真值表及引腳管腳圖

2009-04-01 15:13:52 19357

19357

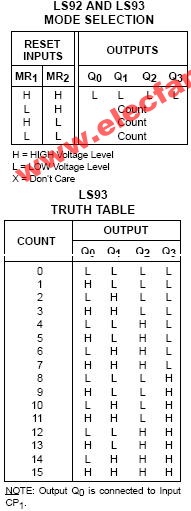

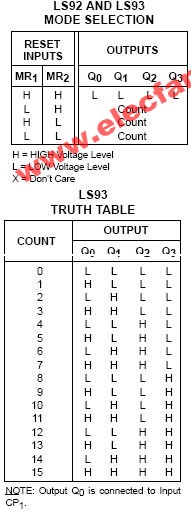

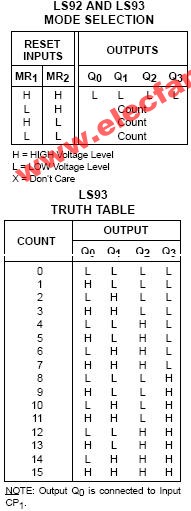

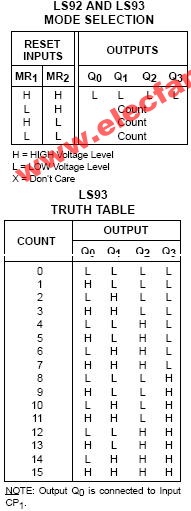

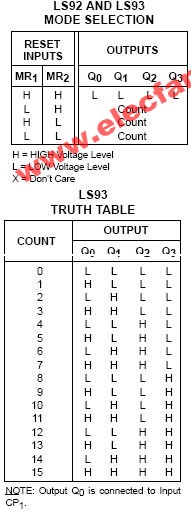

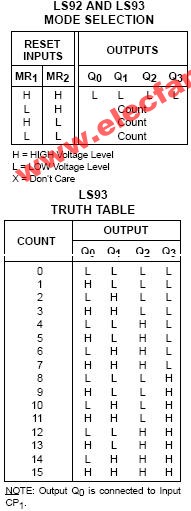

74ls93引腳圖管腳圖及功能真值表

74LS93 TRUTH TABLE

2008-12-01 15:42:17 1951

1951

74ls93引腳圖管腳圖及功能真值表

74LS93 TRUTH TABLE

2008-12-01 15:41:17 1924

1924

74ls93引腳圖管腳圖及功能真值表

74LS93 TRUTH TABLE

2008-12-01 15:40:48 20695

20695

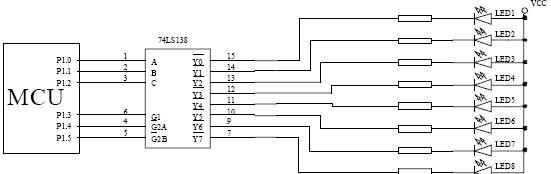

74HC138真值表和管腳圖

五. 實(shí)驗(yàn)步驟1.

2008-09-22 11:15:03 45105

45105

74ls14引腳圖及管腳功能真值表

2008-06-08 08:55:15 35049

35049 74ls11引腳圖

74ls11功能真值表:

2008-06-08 08:48:26 44703

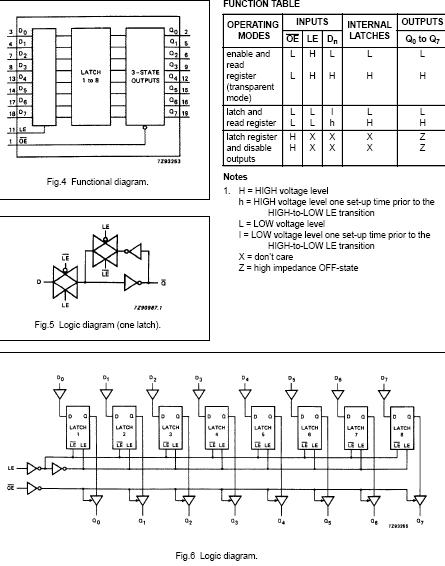

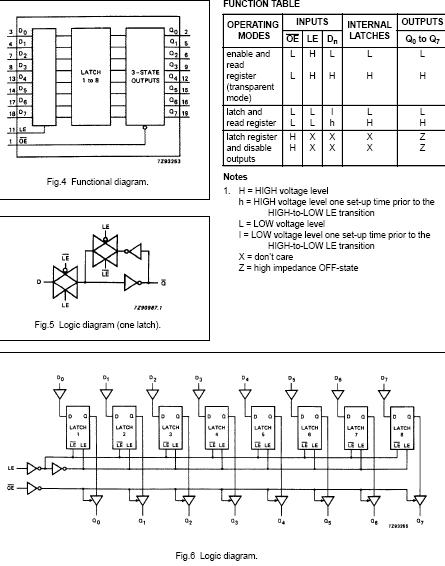

44703 74hc373引腳圖

74hc373真值表和74HC373邏輯功能圖

2008-04-07 23:52:18 23700

23700

CC4008中文資料:型由具有段間快速超前進(jìn)位的4個(gè)全加器段組成。

2008-04-07 22:27:03 32

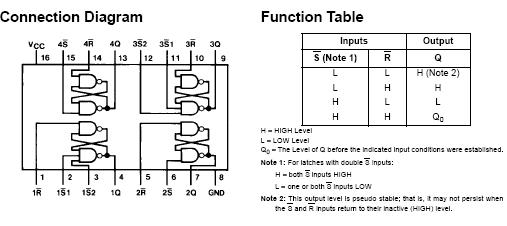

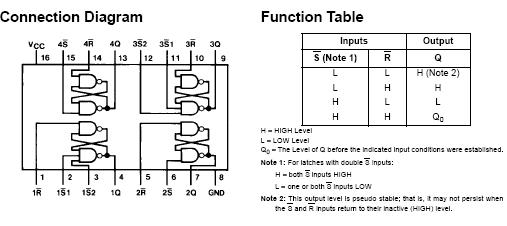

32 74ls279的引腳圖及功能真值表

2008-03-06 14:11:05 90164

90164

7406的引腳功能及真值表

2008-02-28 17:35:37 19431

19431

74ls86管腳圖和引腳圖及真值表如下:

2007-12-17 23:00:21 52324

52324

74ls192真值表

只看真值表也不大方便,下面在提供一下其功能管腳圖

2007-11-29 22:40:16 17788

17788

74ls151管腳圖

真值表:

2007-11-29 22:29:41 87781

87781

D觸發(fā)器真值表分析:

1. D 觸發(fā)器真值表

Dn

2007-09-11 23:15:20 17600

17600

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論