全加器

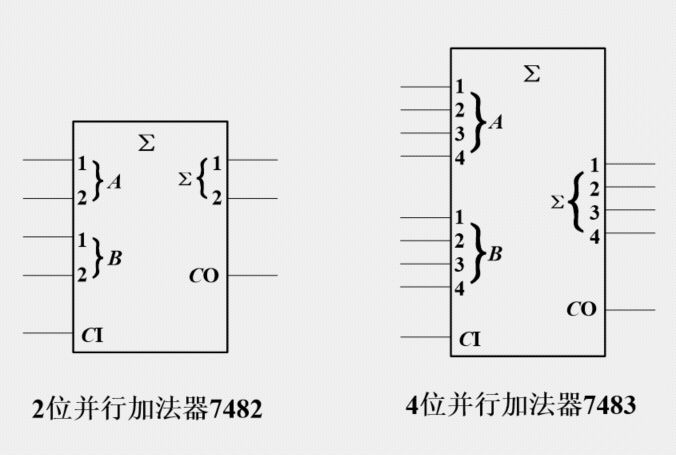

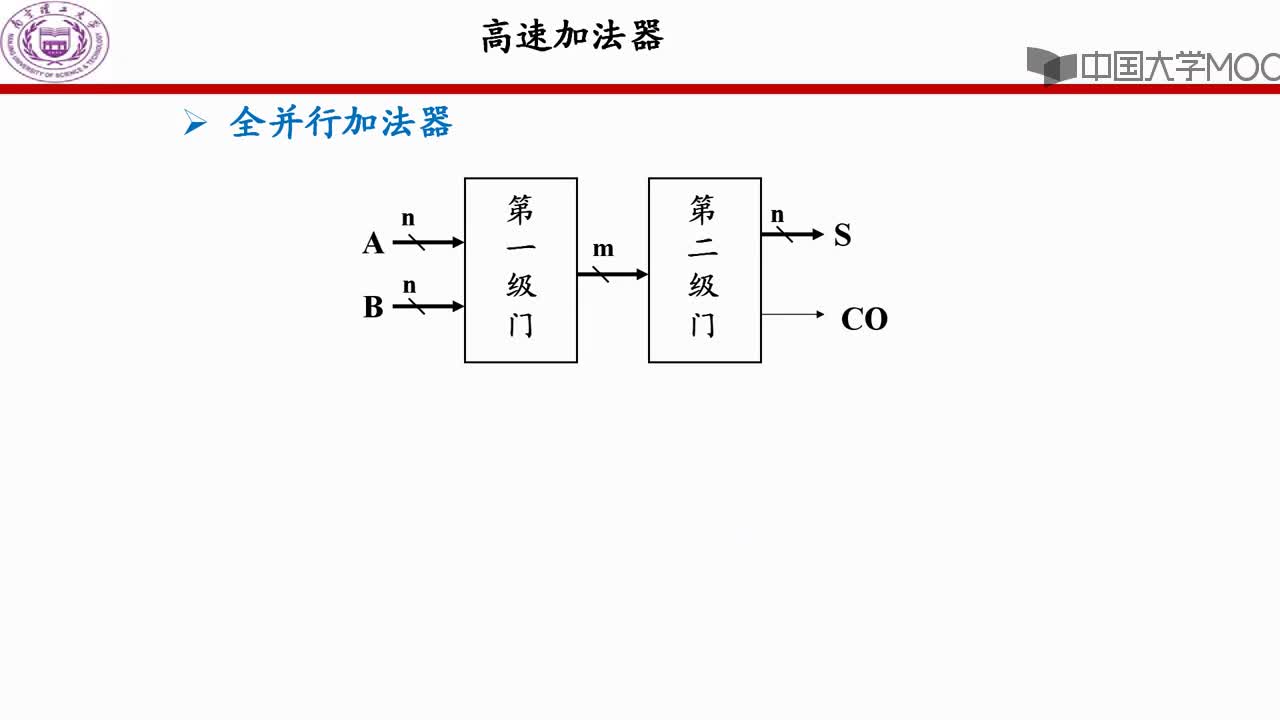

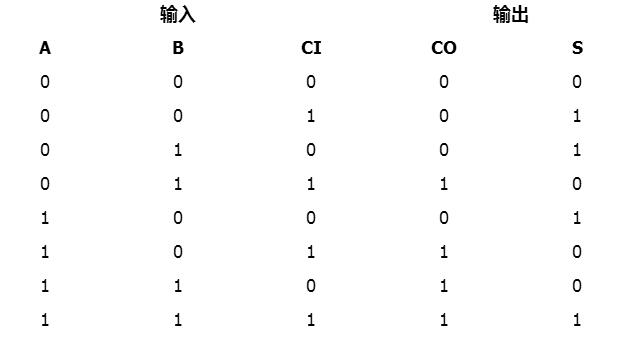

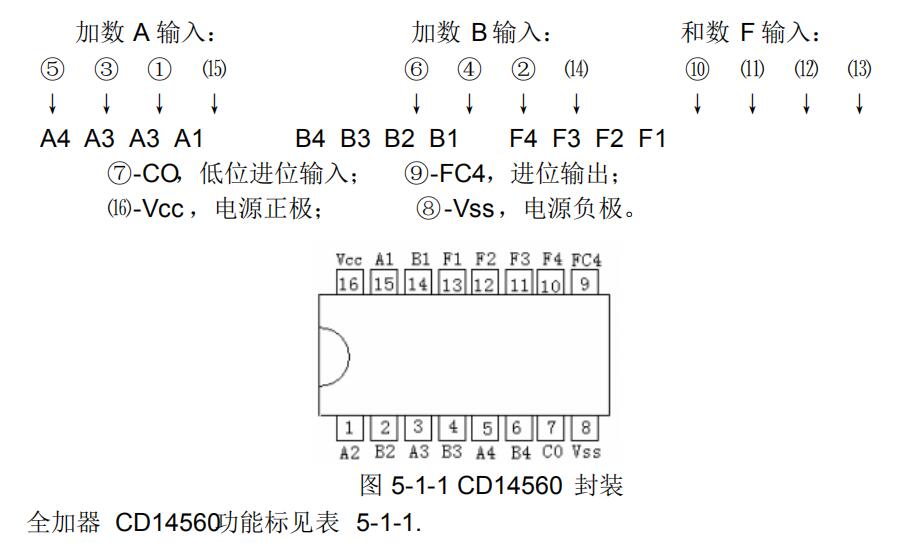

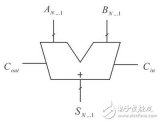

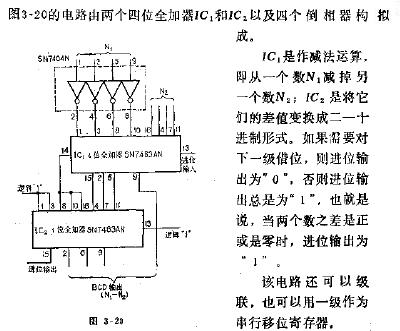

英語名稱為full-adder,是用門電路實(shí)現(xiàn)兩個二進(jìn)制數(shù)相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進(jìn)位,并輸出本位加法進(jìn)位。多個一位全加器進(jìn)行級聯(lián)可以得到多位全加器。常用二進(jìn)制四位全加器74LS283。

全加器是能夠計算低位進(jìn)位的二進(jìn)制加法電路。與半加器相比,全加器不只考慮本位計算結(jié)果是否有進(jìn)位,也考慮上一位對本位的進(jìn)位,可以把多個一位全加器級聯(lián)后做成多位全加器.

全加器和半加器的區(qū)別

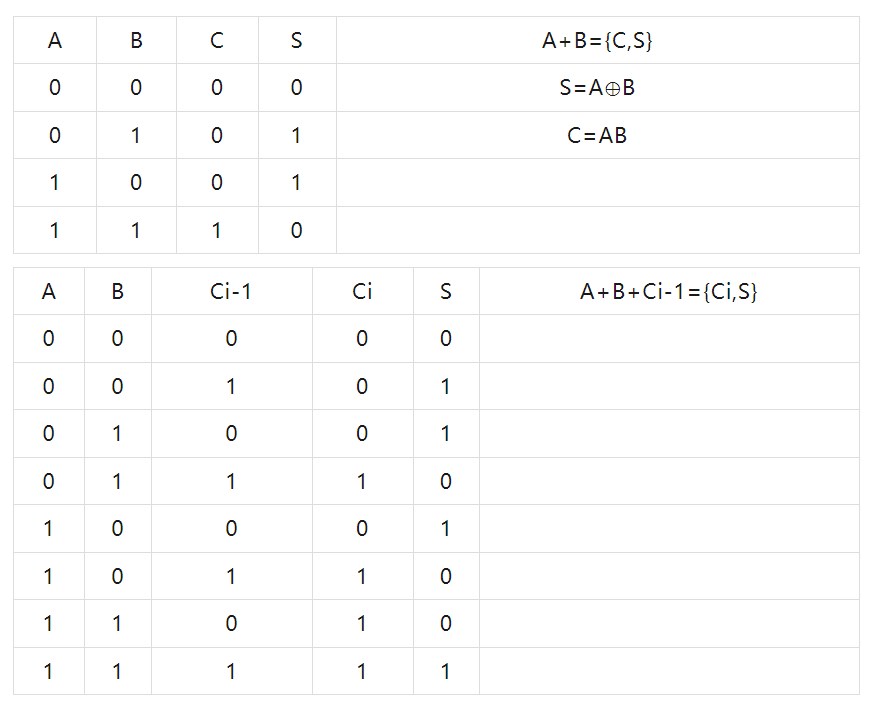

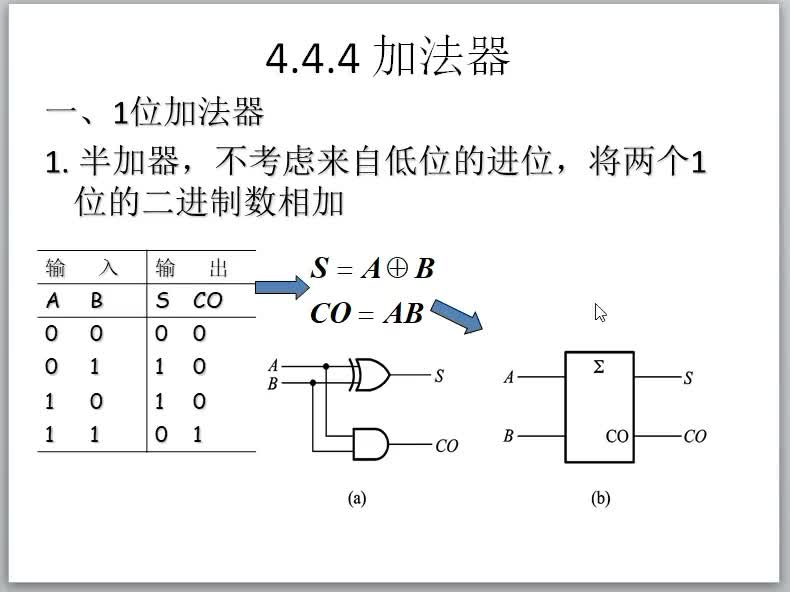

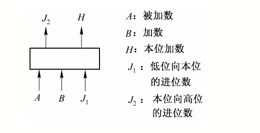

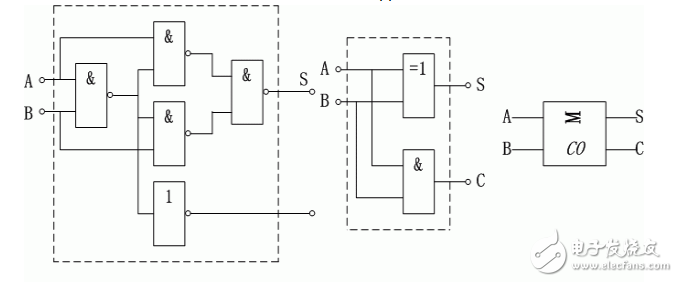

加法器是產(chǎn)生數(shù)的和的裝置.加數(shù)和被加數(shù)為輸入,和數(shù)與進(jìn)位為輸出的裝置為半加器.若加數(shù)、被加數(shù)與低位的進(jìn)位數(shù)為輸入,而和數(shù)與進(jìn)位為輸出則為全加器.

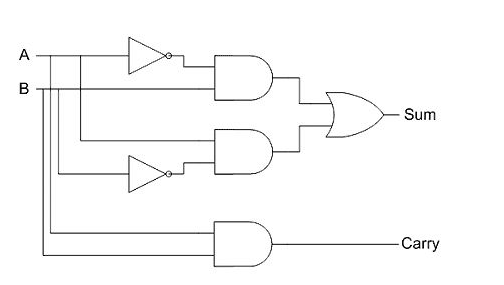

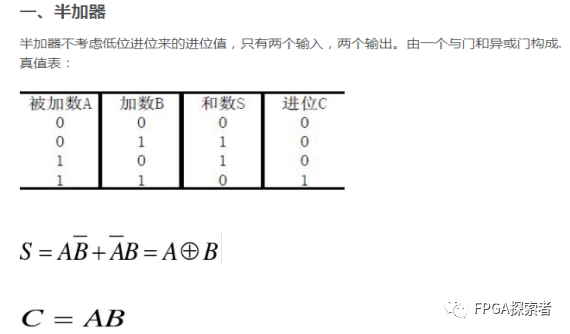

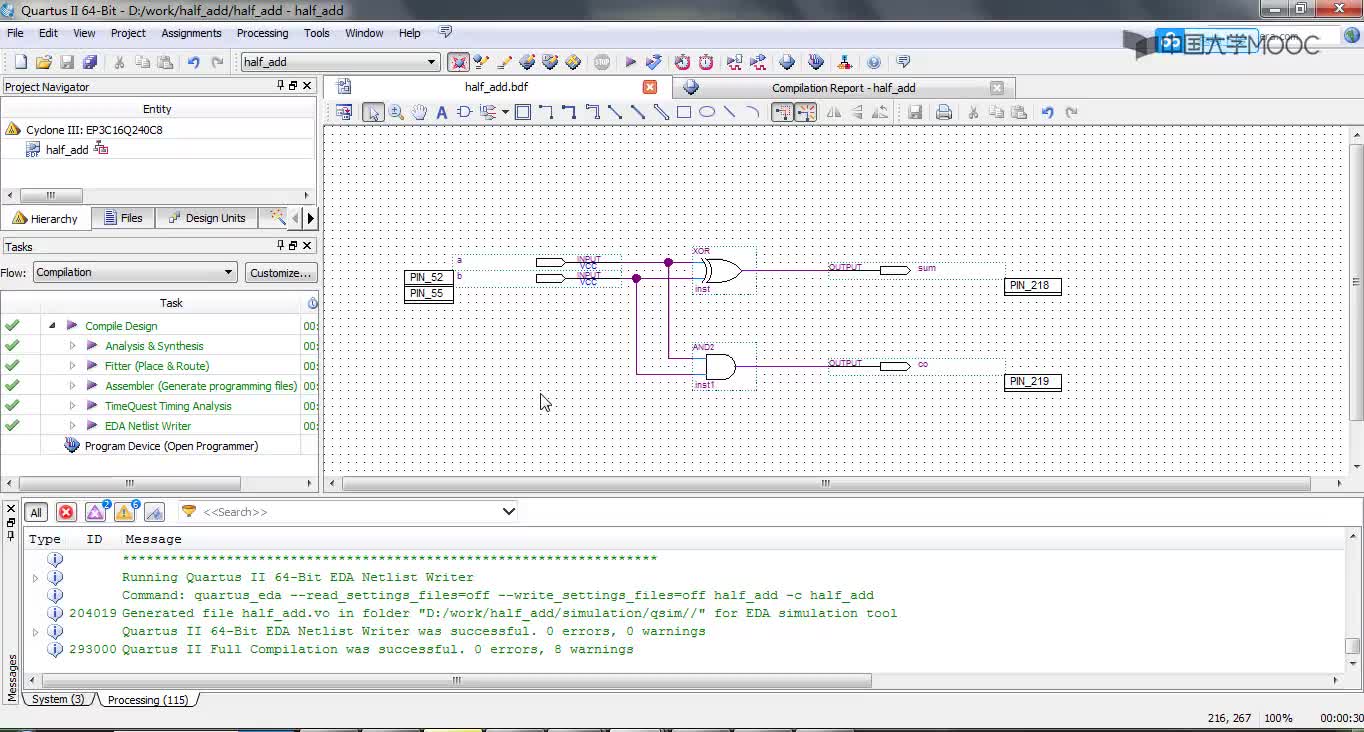

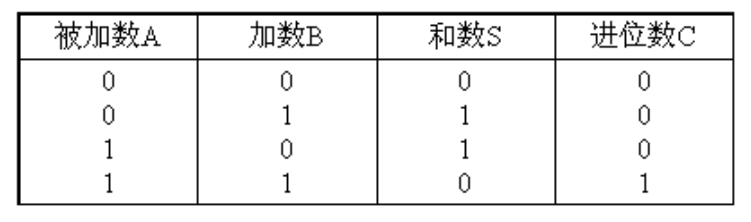

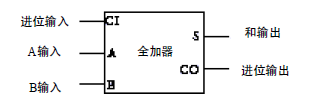

半加器:半加器的電路圖半加器有兩個二進(jìn)制的輸入,其將輸入的值相加,并輸出結(jié)果到和(Sum)和進(jìn)制(Carry).半加器雖能產(chǎn)生進(jìn)制值,但半加器本身并不能處理進(jìn)制值.

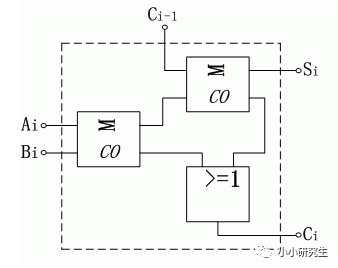

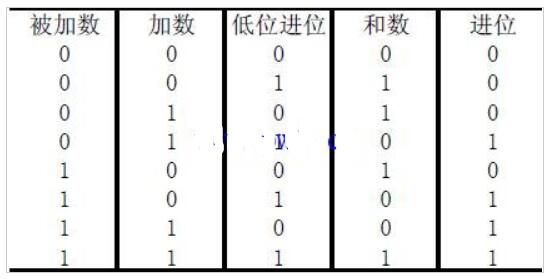

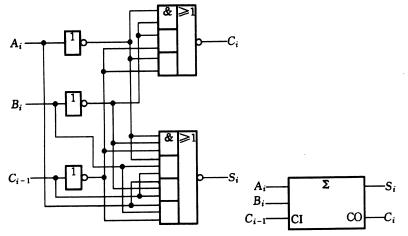

全加器:全加器三個二進(jìn)制的輸入,其中一個是進(jìn)制值的輸入,所以全加器可以處理進(jìn)制值.全加器可以用兩個半加器組合而成.

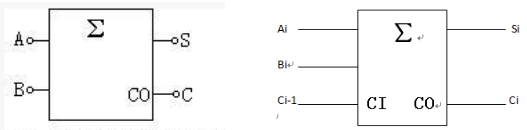

半加器:HA 有兩個代表數(shù)字(A0,B0)有兩個輸出端,用于輸出和S0及進(jìn)位C1(只考慮兩個1位二進(jìn)制數(shù)A和B相加,不考慮低進(jìn)位來的進(jìn)位數(shù)相加稱為半加。)

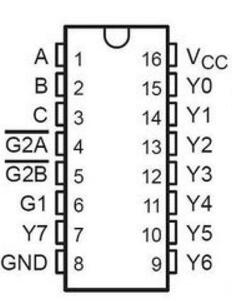

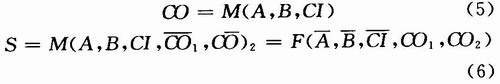

全加器:FA,有三個輸入端,以輸入Ai、Bi、Ci,有兩個輸出端Si,Ci+1(除了兩個1位二進(jìn)制數(shù),還與低位向本位的進(jìn)數(shù)相加稱為全加器。)

半加器能產(chǎn)生進(jìn)位但是不能處理進(jìn)位,而全加器可以。它們本質(zhì)上是一樣的,只是全加器比半加器多一個接收進(jìn)位的輸入端,這樣全加器每一次都要考慮來自低位的進(jìn)位,而半加器不用考慮,直接把兩個二進(jìn)制數(shù)相加就行。

半加器沒有接收進(jìn)位的輸入端,全加器有進(jìn)位輸入端,在將兩個多位二進(jìn)制數(shù)相加時,除了最低位外,每一位都要考慮來自低位的進(jìn)位,半加器則不用考慮,只需要考慮兩個輸入端相加即可。

電子發(fā)燒友App

電子發(fā)燒友App

評論