本篇文章來自賽靈思高級工具產品應用工程師 Hong Han.

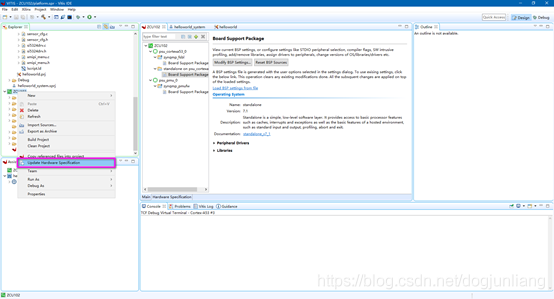

本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado.

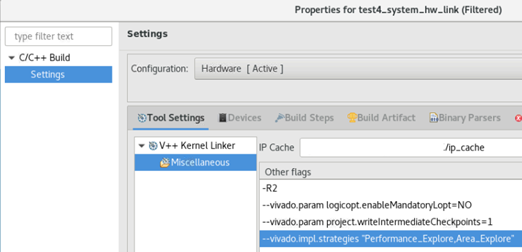

對于Vivado實現階段策略的指定:

--vivado.impl.strategies

舉例設置需要嘗試的實現策略:

--vivado.impl.strategies “Performance_Explore,Area_Explore”

對應configure文件的內容:

#Vivado Implementation Strategies

[vivado]

impl.strategies=Performance_Explore,Area_Explore

在Vivado中可以建立多個基于相同的綜合結果不同策略的impl run來嘗試在單次運行獲取更好的結果,而過去的Vitis一直以來只能支持單一的策略。這里我們可以看到Vitis 2020.2已經可以支持同時在一個run中選擇多個策略進行嘗試, 不同策略用逗號隔開,工具會自動選擇先滿足時序的策略來直接后續的步驟并生成XCLBIN文件。

如需等待所有策略都跑完再挑最好的結果,可以設置 --advanced.compiler 參數

[advanced]

param=compiler.multiStrategiesWaitOnAllRuns=1

在Vivado工程中,可以看到有三個impl runs,一個default策略和另兩個用--vivado.impl.strategies 添加的 Performance_Explore和Area_Explore策略。

對于Vivado仿真階段選項的指定

舉例:意圖在仿真xelab階段覆蓋原有的timeunit, 在Vivado中需要執行以下的命令: (關于仿真選項的具體含義,請參考UG900)

UG900 https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug900-vivado-logic-simulation.pdf

set_property -name {xsim.elaborate.xelab.more_options} -value {-override_timeunit -timescale 1ns/1ps} -objects [get_filesets sim_1]

相應的v++ --link 的選項:

--vivado.prop=fileset.sim_1.xsim.elaborate.xelab.more_options={-override_timeunit -timescale 1ns/1ps}

對于Vivado綜合階段選項的指定

Vitis加速kernel設計實際是一個DFX的設計(關于DFX的內容可以參考UG909),平臺的邏輯屬于靜態邏輯,其布局布線事先就已經完成且鎖定。 包含kernel的邏輯屬于動態部分,需要單獨做out-of-context綜合并連接到平臺的既有網表中做in-context 實現。

UG909:https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/ug909-vivado-partial-reconfiguration.pdf

加入我們期望對于這部分邏輯綜合采用 AreaOptimized_medium Directive,需要執行的Vivado命令如下:

synth_design -top ulp -part xcu200-fsgd2104-2-e -mode out_of_context -directive AreaOptimized_medium

對應的V++ --link選項是:

vivado.prop=run.my_rm_synth_1.STEPS.synth_DESIGN.ARGS.DIRECTIVE=AreaOptimized_medium

注意:在這里synht run的的名字是my_rm_synth_1,可能隨著Vitis版本或者平臺有變化,使用的時候需要注意是否需要做相應的修改。

在底層Vivado工程的synth run的log文件中可以看到綜合的Directive已經成功改為之前設置的值AreaOptimized_medium

其他的Vivado屬性指定:

--export_script/--custom_script: 導出腳本/使用用戶腳本定制編譯和連接的過程

--remote_ip_cache: 指定遠程IP Cache 目錄

--no_ip_cache: 關閉IP Cache

總結:在這里介紹了通過Vitis選項將各類Vivado的設置傳遞到底層Vivado工程的方法并舉例說明, 希望能幫助用戶在Vitis側能很精細地控制Vivado的各類屬性。

編輯:jq

-

編譯

+關注

關注

0文章

676瀏覽量

33816 -

DFx

+關注

關注

0文章

35瀏覽量

10814 -

Vivado

+關注

關注

19文章

832瀏覽量

68355

原文標題:開發者分享 | 如何在Vitis中把設置信息傳遞到底層的Vivado (下)

文章出處:【微信號:TheAlgorithm,微信公眾號:算法與數據結構】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何在Vitis中把設置信息傳遞到底層的Vivado

使用Vitis 在EBAZ4205(ZYNQ)礦機上實現"Hello World!"

如何使用vivado在verilog中傳遞shell命令

Vitis的使用教程

使用Vitis HLS創建屬于自己的IP相關資料分享

【KV260視覺入門套件試用體驗】+02.開發環境安裝Vitis/Vivado(zmj)

Vivado HLS和Vitis HLS 兩者之間有什么區別

Vitis初探—1.將設計從SDSoC/Vivado HLS遷移到Vitis上

在Vitis中把Settings信息傳遞到底層的Vivado

在Vitis中把Settings信息傳遞到底層的Vivado

評論