在本文中,我們將探討差分信號的優勢以及這些優勢如何對您的高速設計產生積極影響。

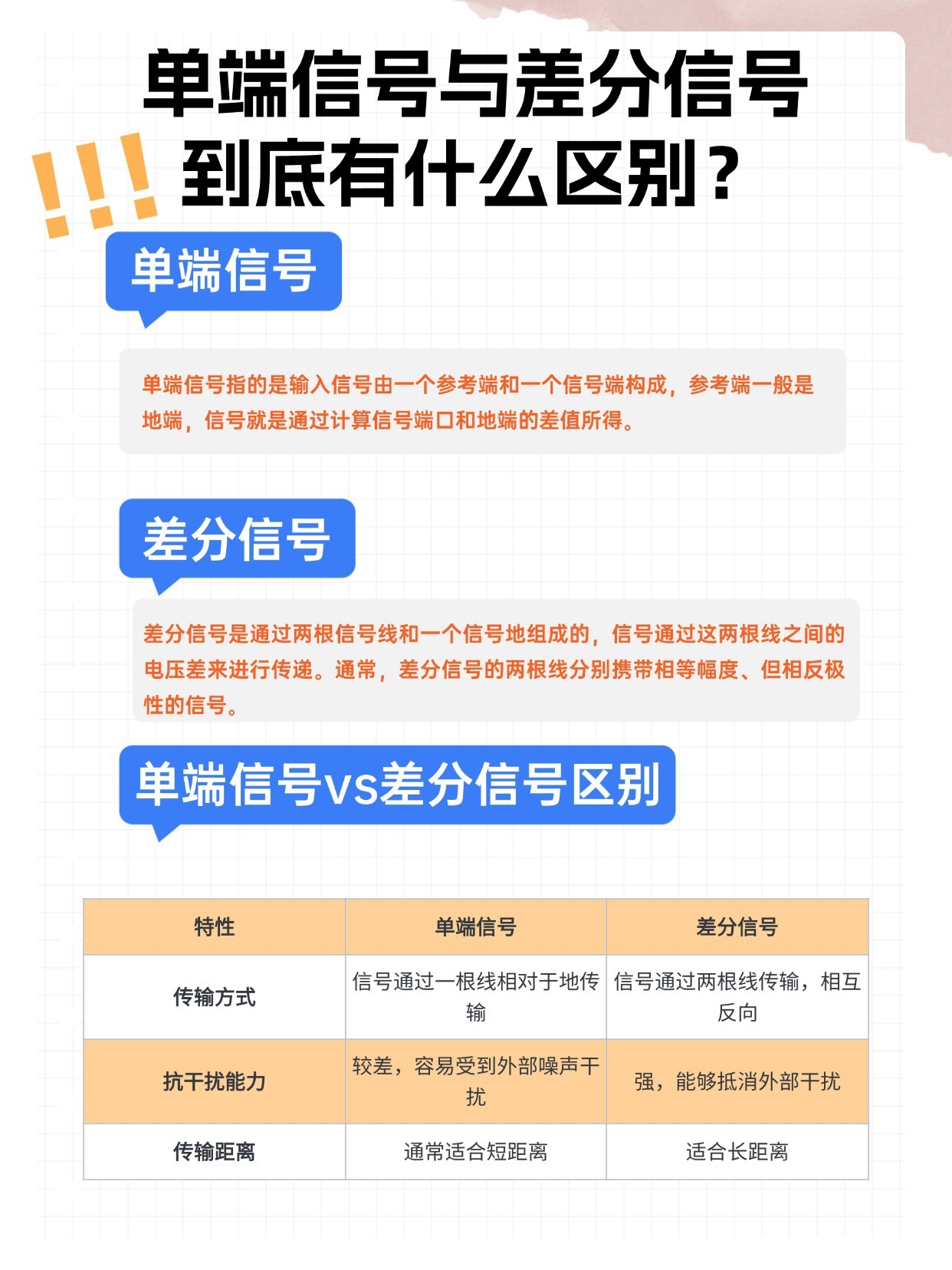

TTL、CMOS 以及其更低電壓的同類 LVTTL 與 LVCMOS 等單端信號都是數字電路設計中的常用技術。然而,使用這些類型的信號發送技術有一些不足,其最終會限制高速設計。由于不同接地電勢和高壓擺率,單端信號在遠距離通信時運行非常吃力。針對每個信號在正負電軌間切換的單端驅動器需要一個高 ΔV/Δt,這就意味著您需要各種負載的電流 (I = CΔV/Δt)。因此,軌至軌信號(大 ΔV)的局限性就顯而易見了:需要更多的電源來實現更短的轉換時間(更小的 Δt)。那么我們應如何圍繞數字設計獲得高速信號,并避免單端信號的損耗呢?實施差分信號!

差分系統一般是三導線系統(也可能更多),包含非反相信號、反相信號以及接地參考。在理想情況的差分系統中,V+ = -V- 和 |I+| = |I-| 可產生平衡的信號。在平衡差分拓撲中,兩根導線緊密耦合在一起,凈接地電流 (IGND-) 等于零。在系統中實施差分信號拓撲有各種優勢,包括更高的信號發送速率、高共模噪聲抗擾度以及更低的功耗等。

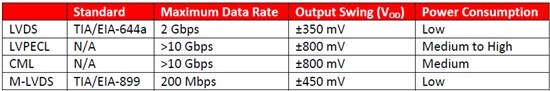

采用差分信號,升降時間大體會比單端信號短,因此在當前通信系統中 10 Gbps 以上數據速率已成為一個可實現的標準。更小的信號擺幅可使系統整體功率預算降低。LVPECL 和 CML 差分信號具有更高的輸出電壓擺幅,因此功耗比 LVDS 及 M-LVDS 信號略高。

差分信號傳輸的第二個優勢在于共模噪聲抗擾度。由于差分信號由幅值相等、極性相反的正負信號組成,因此耦合到傳輸信號上的任何共模噪聲都會被其詢問所抵消。這絕對是巨大的系統優勢,因為很可能會有一些開關穩壓器連接至電源及接地面板,其只是在等待將其能量耦合到您清潔的信號上。這可能開始覺得不算什么,但您很快會發現當嚴格的抖動預算對設計至關重要時,每微微秒都非常關鍵!

下表是最常見差分信號拓撲的摘要,其因功耗、性能及應用領域的不同而不同:

一個優異的差分信號應用實例是將單端 VCO 輸出連接至需要差分 LVDS 時鐘輸入的 FPGA 或串行解串器。為避免因滿足這一需求而破壞原本已非常穩定的系統時鐘架構,您可實施一款器件(如 SN65LVDS1 單路 VDS 發送器等)來執行 VCO 與終端器件之間的單端至差分信號轉換。SN65LVDS1 采用 2.4V 或更高電源電壓運行,理想適用于沒有 3.3V 電軌的低功耗應用。

責任編輯:haq

-

FPGA

+關注

關注

1645文章

22036瀏覽量

618118 -

模擬

+關注

關注

7文章

1438瀏覽量

84513 -

信號

+關注

關注

11文章

2851瀏覽量

78247

發布評論請先 登錄

差分信號的優勢以及對高速設計產生的積極影響

差分信號的優勢以及對高速設計產生的積極影響

評論