前言

為什么每次都將時鐘和復(fù)位單獨(dú)拿出來講?

對于我們使用Xilinx或其他的成熟IP而言,IP相當(dāng)于一個黑匣子,內(nèi)部實(shí)現(xiàn)的邏輯功能我們知道,但是控制不了,只能默認(rèn)OK;一般而言,成熟IP都是經(jīng)過反復(fù)驗(yàn)證和使用,確實(shí)沒有什么問題。所以,IP能不能用,首先要做的就是確保時鐘和復(fù)位。

如果初始化不成功,我們也只能從這兩個方面入手檢查。

一、Aurora核的時鐘

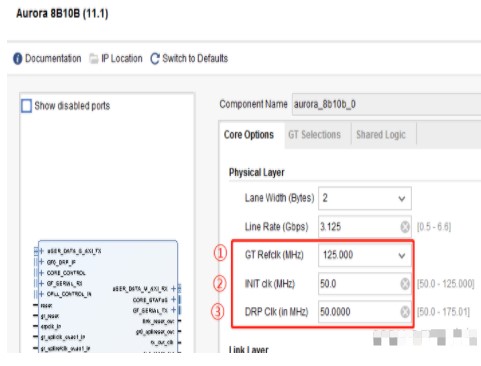

打開Aurora配置界面,我們可以看到有三個時鐘:

參考時鐘、init clock、DRP CLOCK,如下圖所示:

對應(yīng)到代碼:

input INIT_CLK_P;

input INIT_CLK_N;

input DRP_CLK_IN;

input GTXQ0_P;

input GTXQ0_N;

1. GT Refclk : 上一篇我們介紹過,Aurora其實(shí)是基于GT作為物理層實(shí)現(xiàn)的,這個參考時鐘就是GT的參考時鐘,可以翻筆者之前介紹GTX時鐘博文詳細(xì)了解。由外部一對差分輸入時鐘而來,具體根據(jù)硬件而定。默認(rèn)值:125Mhz。

2. INIT CLK :初始化時鐘,之所以要INIT CLK,是因?yàn)樵贕T復(fù)位時,user_clk是停止工作的;Xilinx推薦的配置是INIT CLK時鐘頻率要低于GT參考時鐘。另外,筆者在查看example design的時候,發(fā)現(xiàn)GT復(fù)位是工作在INIT CLK。默認(rèn)值:50Mhz。

3. DRP CLK : DRP時鐘,動態(tài)重配置,感覺沒怎么用到,默認(rèn)值:50Mhz。對于UltraScale器件而言,DRP CLK與INIT CLK相連接。

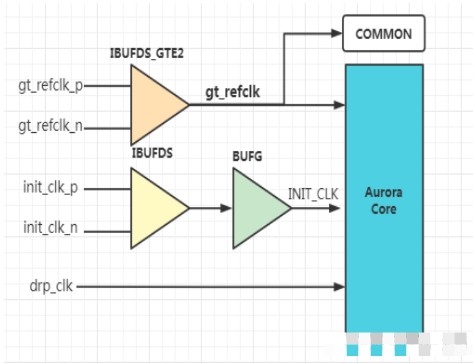

我們再打開example design,看看這幾個時鐘跟Aurora核是怎么連接的:

注意到?jīng)],差分時鐘轉(zhuǎn)為單端時鐘,這里用了兩個原語:IBUFDS_GTE2是GT專用;IBUFDS則是一般情況使用。

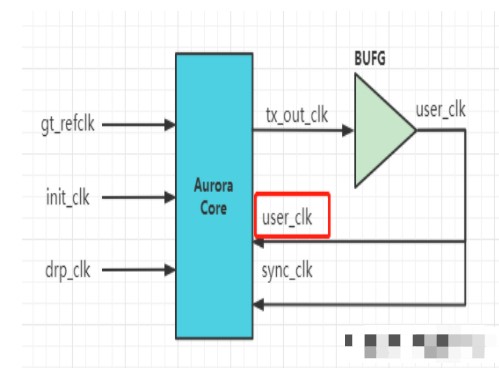

那么,用戶邏輯時鐘又是多少呢?繼續(xù)上圖:

user_clk, 即是用戶邏輯時鐘,我們設(shè)計的用戶接口信號(AXI4-S接口)就是工作在該時鐘域。

而tx_out_clk,其實(shí)就是GTX里所講的gt_txoutclk。

這里一頓分析,只為了我們更好的了解Aurora核。如果只是使用,我們只需要按照IP配置界面選定的時鐘頻率給過去就好。

需要注意的是,參考時鐘必須由專用GT差分輸入時鐘得到,而INIT_CLK和DRP_CLK可以由PLL輸出。

二、復(fù)位設(shè)計

先來看下《PG046》文檔對復(fù)位的描述:

復(fù)位信號是用來將 Aurora 8B/10B core置為一個已知的開始狀態(tài)。在復(fù)位時,核停止當(dāng)前所有操作然后重新初始化一個新的channel。

channel:兩個Aurora所建立的鏈路,可以有多條lane,每條lane對應(yīng)一個高速收發(fā)器GT,統(tǒng)稱為channel。

在全雙工模式下,復(fù)位信號對channel的TX和RX都進(jìn)行復(fù)位。

在單工模式下,tx_system_reset復(fù)位TX鏈路,rx_system_reset復(fù)位RX鏈路。

而gt_reset則是復(fù)位高速收發(fā)器GT,最終也會復(fù)位Aurora核。(這說明GT復(fù)位更加底層,只要GT復(fù)位,就會對核進(jìn)行復(fù)位,后面代碼也會證實(shí)這一點(diǎn))

再來看兩個case:

CASE 1:全雙工配置下的系統(tǒng)復(fù)位

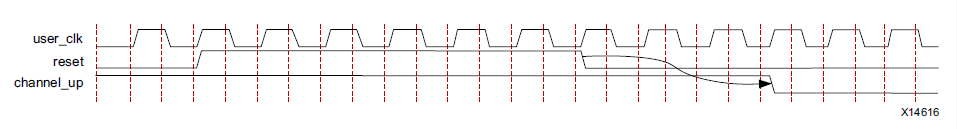

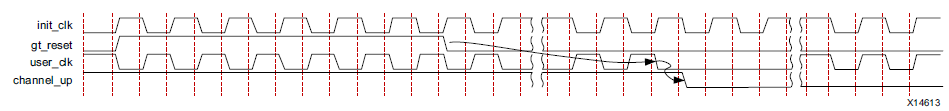

在全雙工配置模式下,復(fù)位信號應(yīng)至少保持6個時鐘周期(user_clk)。channel_up在3個時鐘周期(user_clk)后拉低,如下圖所示:

CASE2:全雙工配置下的GT復(fù)位

在全雙工配置模式下,GT復(fù)位信號應(yīng)至少保持6個時鐘周期(init_clk)。復(fù)位的結(jié)果user_clk會在幾個時鐘周期后停止,因?yàn)闆]有了來自GT的txoutclk。隨后,channel_up也會跟著拉低。跟前文講述一致。如下圖所示:

其他的就不再展開了,感興趣的可以詳細(xì)查閱《PG046》。

我們再從代碼的角度來看看復(fù)位:

Aurora復(fù)位信號有兩個,一個是系統(tǒng)復(fù)位RESET,一個是GT復(fù)位GT_RESET;復(fù)位邏輯就如同前文描述,具體到代碼,感興趣的可以查閱示例工程的reset_logic.v;這里直接給出結(jié)論:

1. GT復(fù)位更加底層,優(yōu)先級要高于系統(tǒng)復(fù)位RESET;也就是說,若GT復(fù)位,那么系統(tǒng)復(fù)位也拉高;《PG046》對復(fù)位的描述也是如此。

2. 當(dāng)GT復(fù)位沒有拉高時,根據(jù)輸入的系統(tǒng)復(fù)位RESET,使用移位寄存器對其打拍,輸出復(fù)位。

3. GT復(fù)位同步于INIT_CLK,所以先將其同步到user_clk時鐘域,再對Aurora進(jìn)行復(fù)位。

最后,Xilinx大佬操作來了!

①channel_up : 只要channel_up信號為高,那么說明核初始化完成,且建立了channel,在channel_up拉高之前,lane_up會拉高。我們邏輯設(shè)計可以直接使用該信號,在初始化完成之后,再進(jìn)行邏輯操作。

②debug流程:具體查看P.105

后記

現(xiàn)在FPGA都集成了高速收發(fā)器硬核,各種協(xié)議的高速接口都是基于GT物理層來實(shí)現(xiàn)的。所以,在學(xué)習(xí)這些高速接口IP之前,最好先熟悉GT。后面就會發(fā)現(xiàn)很多東西都是通的。

審核編輯:湯梓紅

-

Xilinx

+關(guān)注

關(guān)注

73文章

2183瀏覽量

124484 -

時鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132911 -

復(fù)位

+關(guān)注

關(guān)注

0文章

179瀏覽量

24588

發(fā)布評論請先 登錄

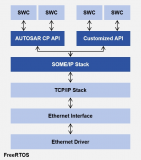

光庭信息SOME/IP平臺融合解決方案介紹

Xilinx Shift RAM IP概述和主要功能

詳解Xilinx的10G PCS PMA IP

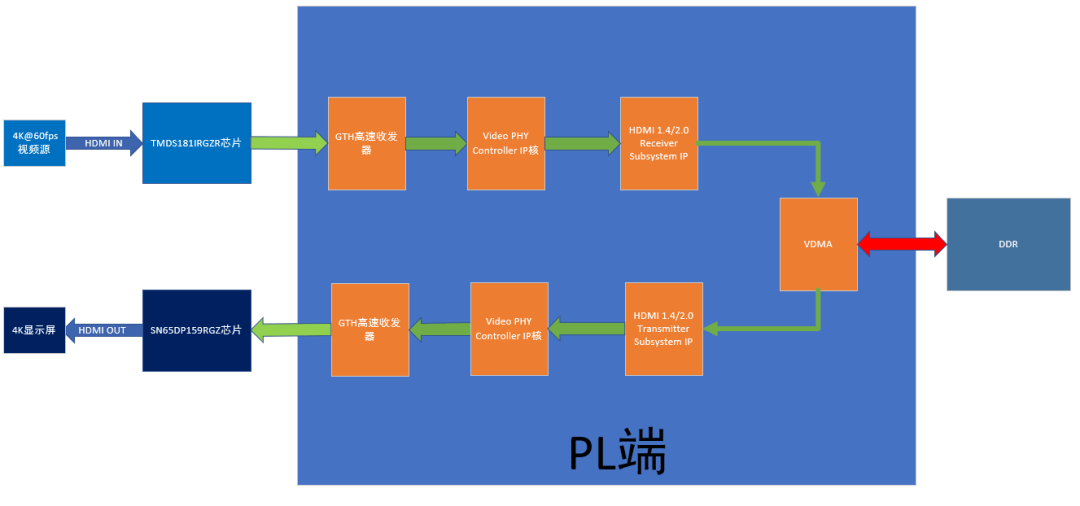

解鎖4K,Xilinx MPSoC ARM + FPGA高清視頻采集與顯示方案!

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】 UART測試

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

復(fù)位電路的設(shè)計問題

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+04.SFP之Aurora測試(zmj)

復(fù)位電路介紹 復(fù)位電路的原理及作用

STM32復(fù)位電路用復(fù)位芯片和阻容復(fù)位電路區(qū)別

復(fù)位電路為什么要加二極管

速度繼電器復(fù)位轉(zhuǎn)速介紹

Xilinx平臺Aurora IP介紹(二)時鐘與復(fù)位

Xilinx平臺Aurora IP介紹(二)時鐘與復(fù)位

評論