1、unified2020.1

linux ubuntu18.04.2

推薦文檔鏈接:

https://xilinx.github.io/Vitis_Libraries/vision/2020.1/overview.html#hls...

https://forums.xilinx.com/t5/High-Level-Synthesis-HLS/Using-Vitis-Vision...

https://github.com/Xilinx/Vitis_Libraries

Vitis Vision庫是OpenCV和Vision功能的加速庫,可在Vitis環境中使用,這些庫的L1目錄是示例設計。為了適應各種用戶環境,從2020.1版本開始,Xilinx不再使用Vivado / Vitis工具提供預安裝的OpenCV版本。盡管Vitis_hls編譯Vision庫不需要OpenCV,但是用戶測試驗證使用時OpenCV。

2、linux下安裝opencv(opencv-3.4.12)

鏈接:https://opencv.org/releases/

sudo apt-get install build-essential

sudo apt-get install cmake git libgtk2.0-dev pkg-config libavcodec-dev libavformat-dev libswscale-dev libjpeg.dev libtiff4.dev

unzip opencv-3.4.12.zip

cd opencv-3.4.12

mkdir build

cd build

cmake -DCMAKE_BUILD_TYPE=Release -DOPENCV_GENERATE_PKGCONFIG=ON -DCMAKE_INSTALL_PREFIX=/usr/local …

make -j8

sudo make install

ldconfig -p |grep opencv

sudo ldconfig -v

qt中測試,報錯 failed to load module “canberra-gtk-module”

sudo apt-get install libcanberra-gtk-module

3、在vitis library中 每個類別提供三種代碼

L1:最低級的代碼,旨在用高級綜合工具綜合后,可以在Vitis(邏輯)中實現這些功能,或將其用作新IP開發的一部分。

L2:中間級可以在Vitis中實現功能(邏輯)。不太懂也不關心!

L3:最高級提供了由多個加速內核創建的應用程序。不太懂也不關心!

4、在linux系統中測試

(1)復制L1/examples中的sobelfilter

(2)將build文件復制到文件夾(xf_config_params.h)這個文件存放的是濾波器的參數

(3)在data中輔助一個128x128的png圖像

(4)配置hls運行前的環境

source /settings64.sh

export OPENCV_INCLUDE=

export OPENCV_LIB=

export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:

(5)在此終端打開vitis_hls

(6)新建hls工程

(7)添加源文件中所需的.cpp 和.h 并且在cflags中添加

-I

-std=c++0x(其他調用的.h文件的路徑,否則將頭文件復制到一個文件夾)

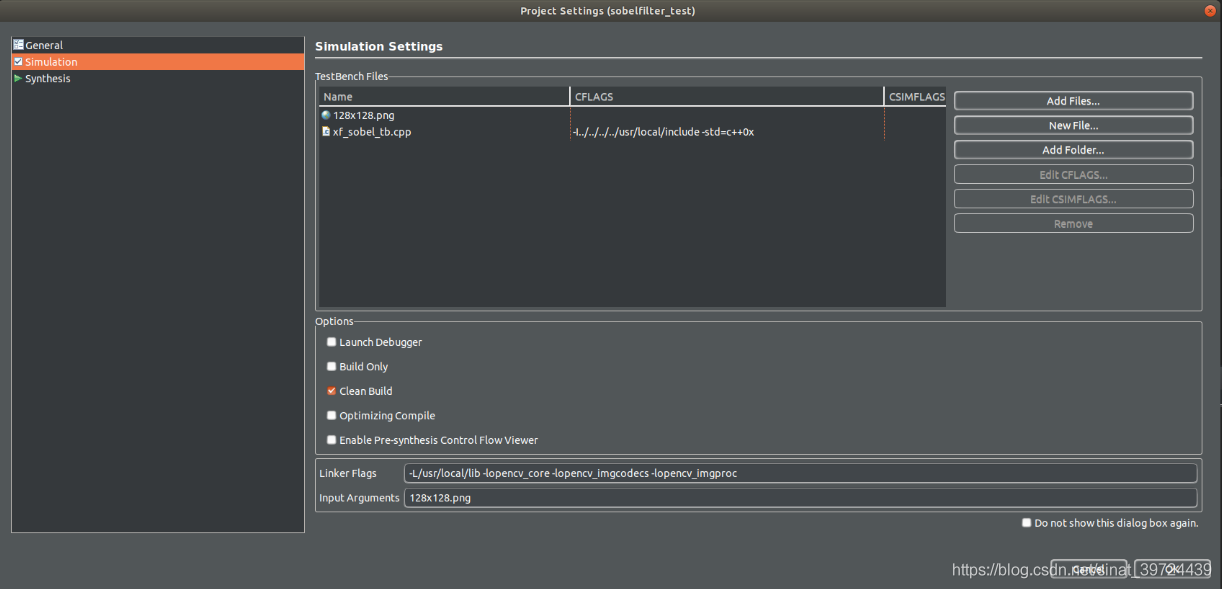

(8)在tb的cflags中添加

-I

-std=c++0x -I

(其他調用的.h文件的路徑,否則將頭文件復制到一個文件夾)

(9)在連接器 (linker flags)中添加

-L

-lopencv_core -lopencv_imgcodecs -lopencv_imgproc

(10)在輸入(input arguments)中輸入圖片名稱

(11)保存

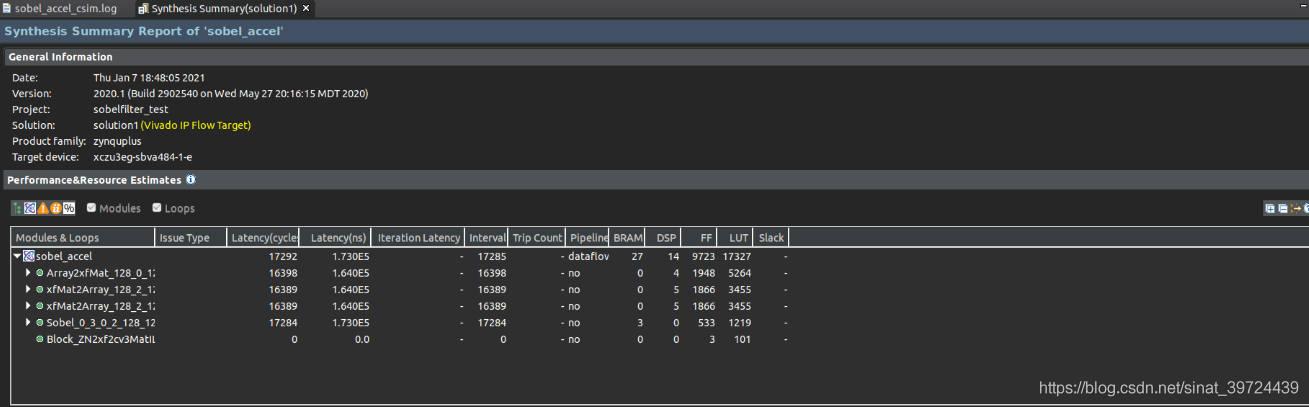

5、點擊綜合

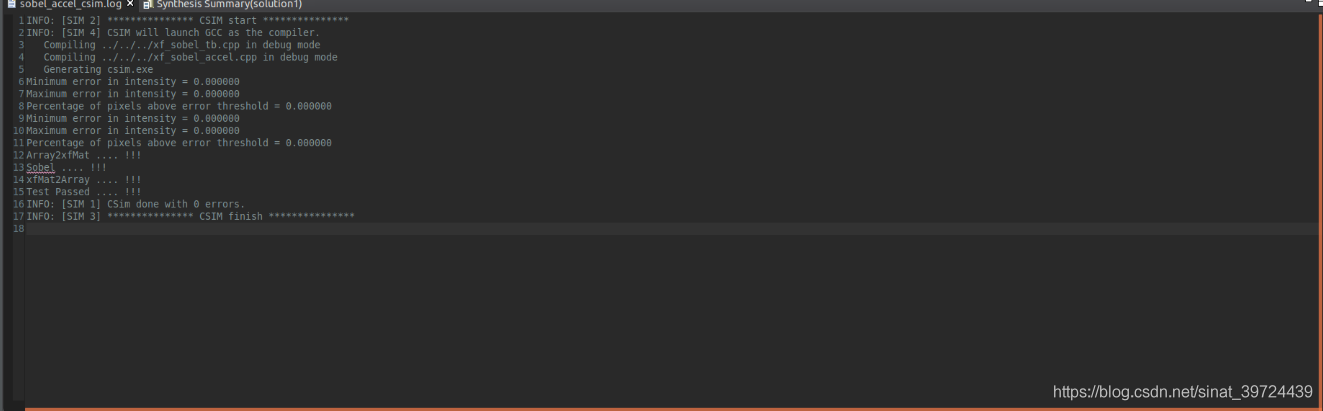

6、點擊仿真

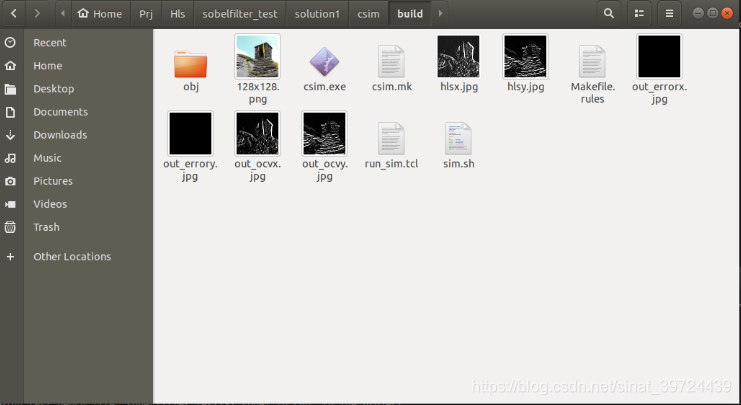

7、實驗現象

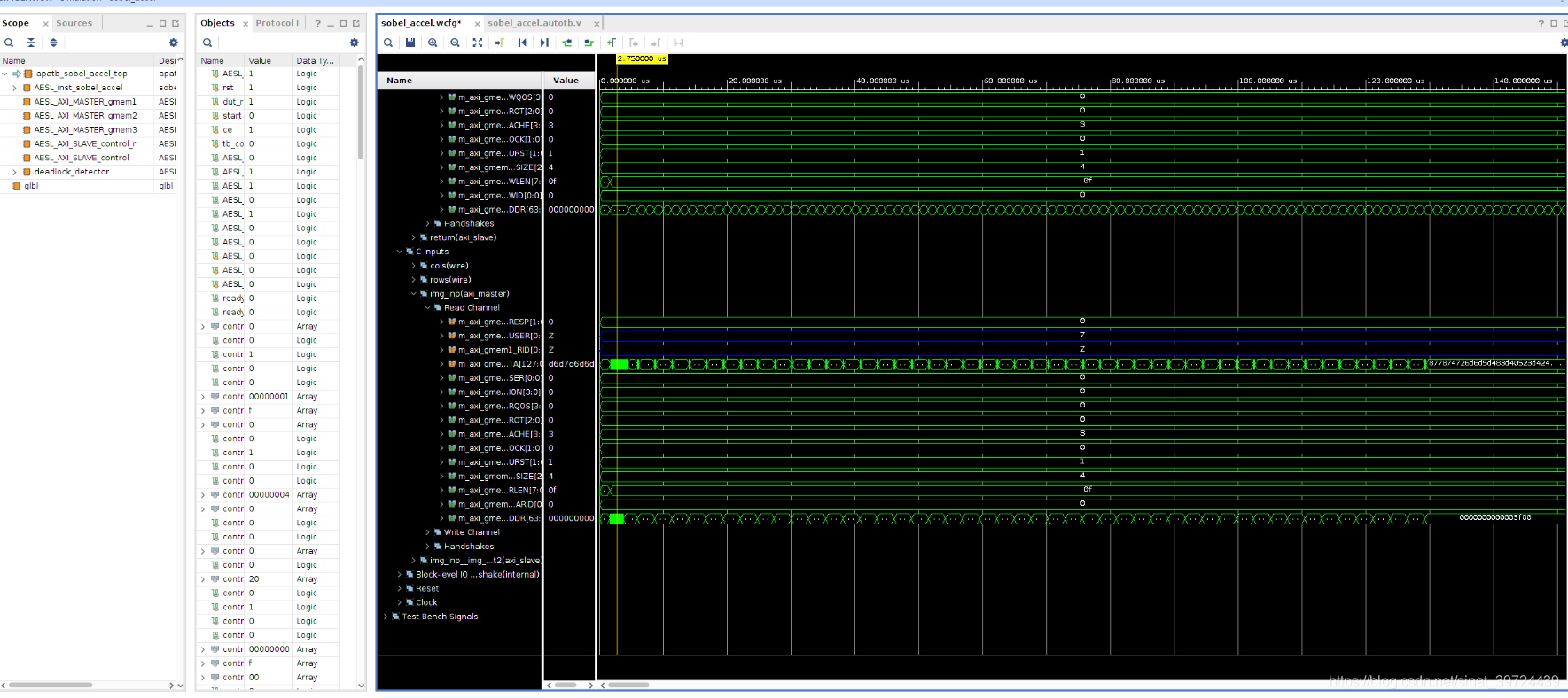

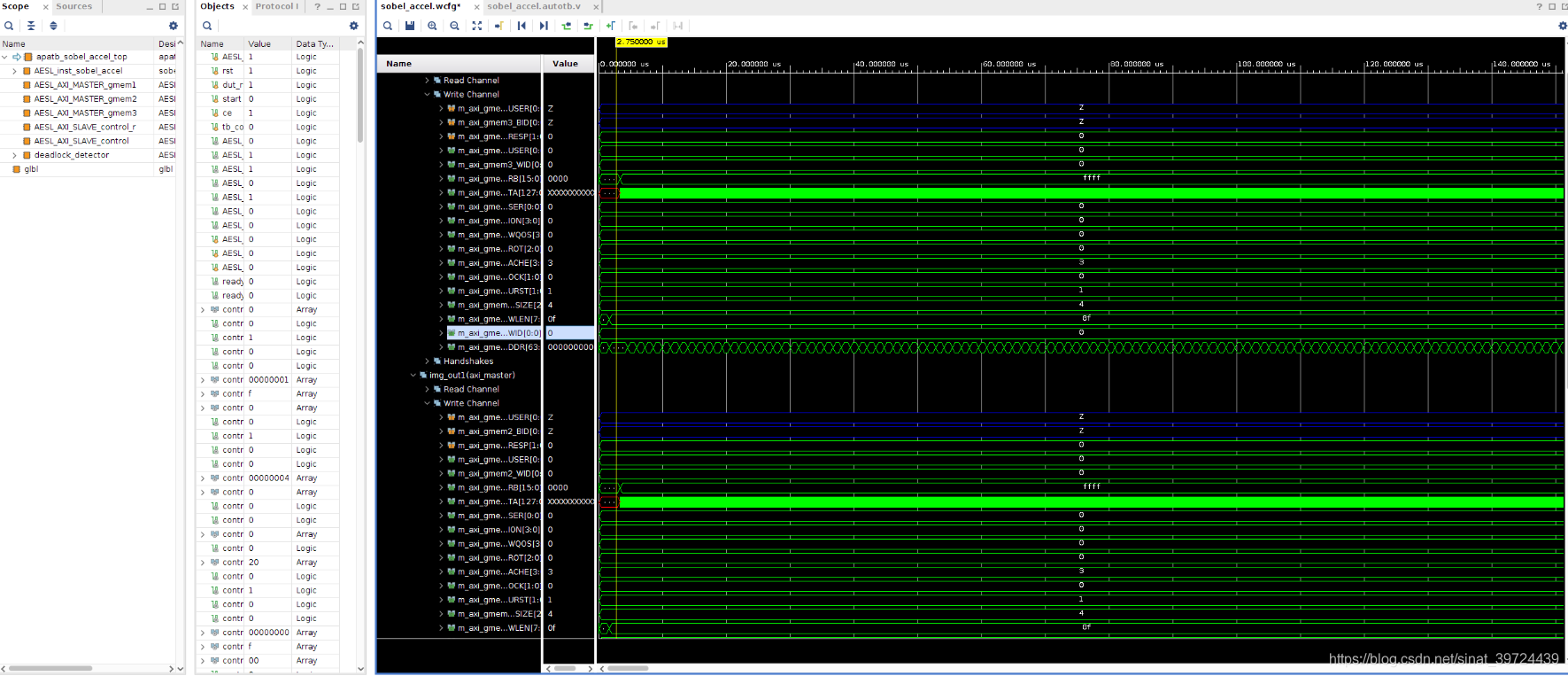

8、協同仿真

9、信號太多,挑模塊的輸入輸出即可,否則除非內存很大,不然會卡死。

輸入數據

輸出數據

審核編輯:符乾江

-

圖像處理

+關注

關注

27文章

1325瀏覽量

57769 -

Vitis

+關注

關注

0文章

148瀏覽量

7853

發布評論請先 登錄

如何使用AMD Vitis HLS創建HLS IP

Vivado HLS設計流程

圖像采集卡:現代圖像處理技術的關鍵組件

FPGA圖像處理基礎----實現緩存卷積窗口

使用HLS流程設計和驗證圖像信號處理設備

使用AMD Vitis進行嵌入式設計開發用戶指南

基于FPGA實現圖像直方圖設計

基于Vitis HLS的加速圖像處理

基于Vitis HLS的加速圖像處理

評論