說起debug(調試),這可能是令所有開發者抓狂且繞不開的永恒話題,相信每個驗證開發者都有很多debug經歷可以吐槽,因為這確實是一個似乎看不到盡頭的艱難挑戰。

調試的過程極為復雜且結果不可預測:首先通過對RTL或者門級模型輸入激勵來驗證模型是否按預期運行。如果未按預期運行,則該事件將被標記為錯誤。如果錯誤發生在驗證平臺,很有可能需要重寫代碼或重新運行,如果錯誤發生在設計中,對于比較淺顯的錯誤還好說,運行幾個仿真周期就可以找到,但若錯誤非常極端且隱蔽,則可能要運行數百萬個仿真周期。由于bug所在位置和涉及的代碼行數的不同,找出bug的時間自然也會大不相同。

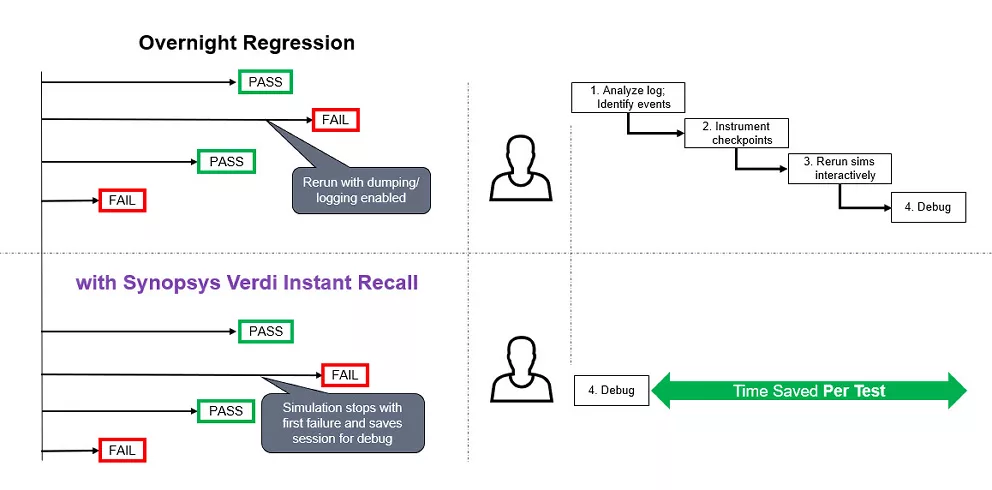

因此,擴大調試的覆蓋范圍、提高調試過程的速度和準確性,是最需要解決的驗證挑戰之一。我們將在下文中分享如何利用調試工具,以及先進的調試技術幫助開發者簡化整個調試過程。

是什么導致了芯片調試的復雜性?

在人工智能(AI)、機器學習(ML)和高性能計算(HPC)等新興應用的推動下,芯片變得越來越大且越來越復雜,調試難度也急劇增加。

目前我們已經實現了:

芯片由數百個IP模塊和子系統組成(包括復雜的協議和內存),部分由內部開發,部分通過現貨購買

各種新的、特定領域的架構

芯片尺寸是影響調試復雜性的因素之一,但對調試過程影響更大的是芯片功能。比如,在小規模設計中可能需要數千個并行發生的不同事件來對特定條件進行仿真,要隔離漏洞就需要檢查這些并行事件以確定問題到底出在哪里。芯片的終端應用也會影響調試過程。例如,用于手機的低功耗芯片的設計與嵌入式處理器的設計就大不相同。對于嵌入式處理器設計,開發者可能會希望借助RTL來調試C語言/匯編代碼,而在低功耗設計中,當設計的一部分電路掉電后,便可插入處理器設計中未使用的隔離單元或其他功耗保持技術。

因此智能的調試工具是必須的,尤其對于汽車等對功能安全合規性要求極高的應用來說,精細的調試更加重要。

AI加速鎖定

讓芯片設計失敗的罪魁禍首

要找到芯片設計中的bug并非易事,原因之一是需要分析和理解的信號太多了。如果沒有好用的功能調試工具就有可能需要進行成千上萬次的仿真和測試來驗證設計,而且每一次測試都會產生大量數據,必須要進一步分析才能從中找出漏洞,這就是為什么說開發者一般會進入一個沒完沒了的調試周期,調試效率比較低。

而事實證明,在效率方面,AI和ML一直具備顯著優勢,它們能夠快速地從大量數據中發現問題核心,AI增強的調試器可以根據它們的特征對錯誤進行分段,并生成一個更易于管理的數字來預估根本原因。

現在,通過使用基于ML的Verdi回歸調試自動化技術,這些暢想將得以實現。

Verdi讓芯片調試更加省時省力

新思科技通過Verdi自動化調試系統(Verdi SoC調試平臺的核心)為所有設計和驗證流程提供全面調試。該系統具有20億門級的設計容量,并定期更新,增加新功能。Verdi自動化調試系統通常可以減少50%以上的調試時間,開發者因此可以將更多精力集中在其他更重要的任務中。此外,Verdi系統的高效率還可以支持開發者跨域、跨抽象級別進行查找及修復bug。

Verdi自動調試系統是新思科技 Verification Continuum的一部分。新思科技Verification Continuum是一系列解決方案的組合,旨在幫助開發者在早期快速發現設計缺陷,更早開始對系統進行驗證。

結 語

開發者通常面臨著復雜調試和上市時間等多重壓力,我們完全可以將勞動密集型任務自動化,通過先進的調試技術——Verdi自動調試系統來實現全面覆蓋高效調試以及簡便應用等調試需求,徹底破解難題,加速芯片上市。

原文標題:快、準、狠,Verdi 自動解決 debug 難題,釋放芯片生產力

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

芯片

+關注

關注

460文章

52520瀏覽量

441155 -

模塊

+關注

關注

7文章

2788瀏覽量

50427 -

調試

+關注

關注

7文章

612瀏覽量

34740

原文標題:快、準、狠,Verdi 自動解決 debug 難題,釋放芯片生產力

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

根據標題利用API實現電商多平臺同步:省時省力生成文章

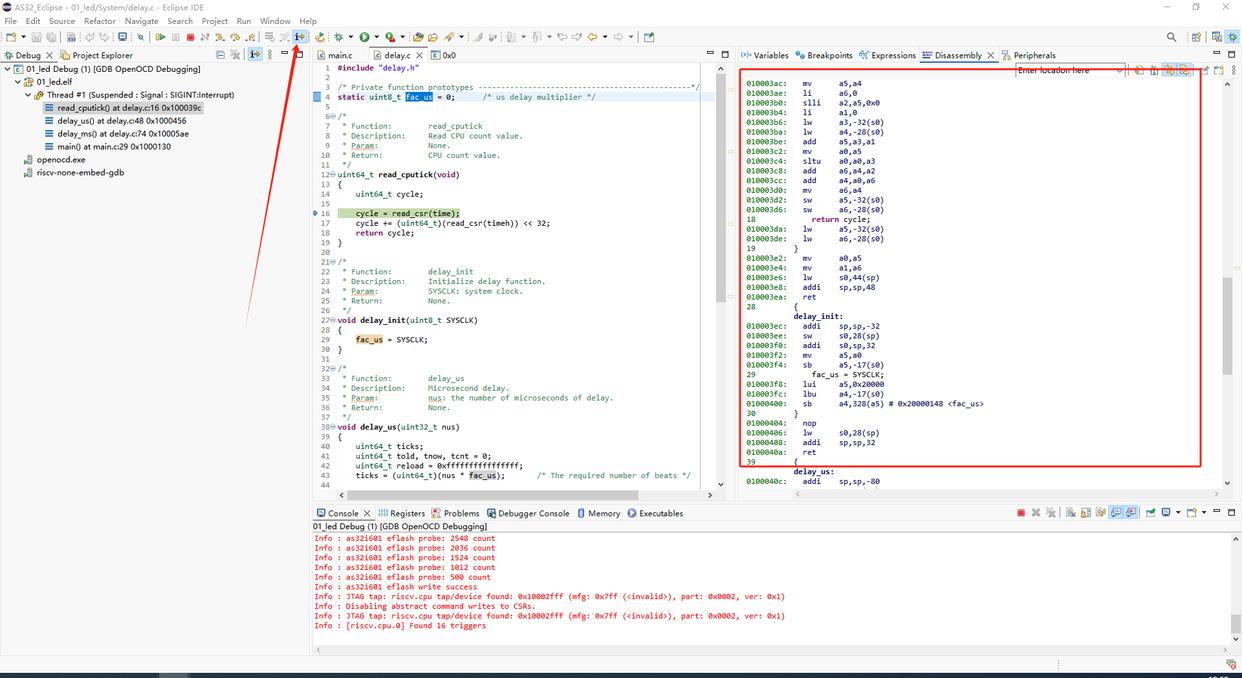

調試工具:Eclipse調試工具欄與窗口的深入分析

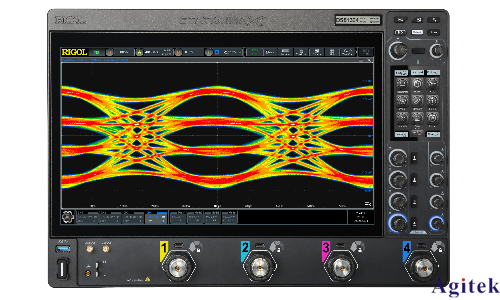

普源MSO8000系列示波器多總線調試的自動化方案

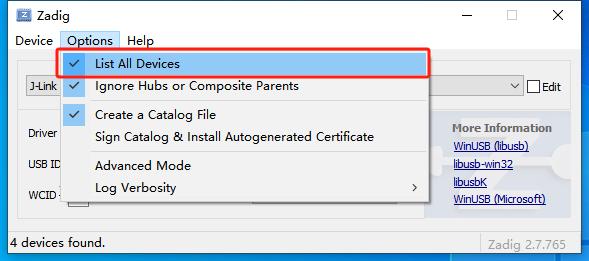

硬件調試:JLink 驅動配置與調試技巧

伺服剛性和慣量比調試

智多晶XSBERT讓高速串行接口調試化繁為簡

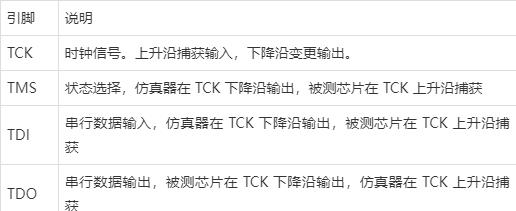

RISC-V JTAG:開啟MCU 芯片調試之旅

恩智浦分享Zephyr調試技巧

Dali通信系統的調試指南

自動控制系統的調試方法 自動控制系統與傳統控制系統的比較

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

數字電源的低壓調試和高壓調試

SpeedDP! 超便利AI自動圖像標注工具 功能豐富、省時省力

新思科技Verdi調試平臺的功能

Verdi自動調試系統讓芯片調試更加省時省力

Verdi自動調試系統讓芯片調試更加省時省力

評論