Step 1

首先,打開最新版本的Vivado(當(dāng)前為2021.2):

1. 新建一個(gè)Vivado工程,將器件直接選定為board – VPK120。

2. 接著新加入一個(gè)以太網(wǎng)IP core,選好自己所需要的IP配置,本文以MRMAC IP為例,并在以太網(wǎng)IP的GT配置那頁,選擇GTM和156.25MHz時(shí)鐘。

3. 然后就可以右鍵點(diǎn)擊IP,選擇Open IP Example Design…

Step 2

例子工程產(chǎn)生完畢之后,在工程的XDC文件里加入GT位置約束和參考時(shí)鐘位置約束,示例如下:

set_property PACKAGE_PIN AF45 [get_ports gt_ref_clk_p]

set_property PACKAGE_PIN BG52 [get_ports {gt_rxp_in[0]}]

1. 這個(gè)參考時(shí)鐘是VPK120板上自帶的,可進(jìn)行配置,產(chǎn)生不同頻率的參考時(shí)鐘。

2. 另外,VPK120板上有2個(gè)QSFP-DD光模塊插槽,此處GT的(管腳)位置約束,正是為了將GT選在其中一個(gè)光模塊插槽上面,方便之后的硬件上面連接使用。

Step 3

等該例子工程跑完綜合,實(shí)現(xiàn),并產(chǎn)生bit文件之后,請將PDI文件加載到你的VPK120里面:

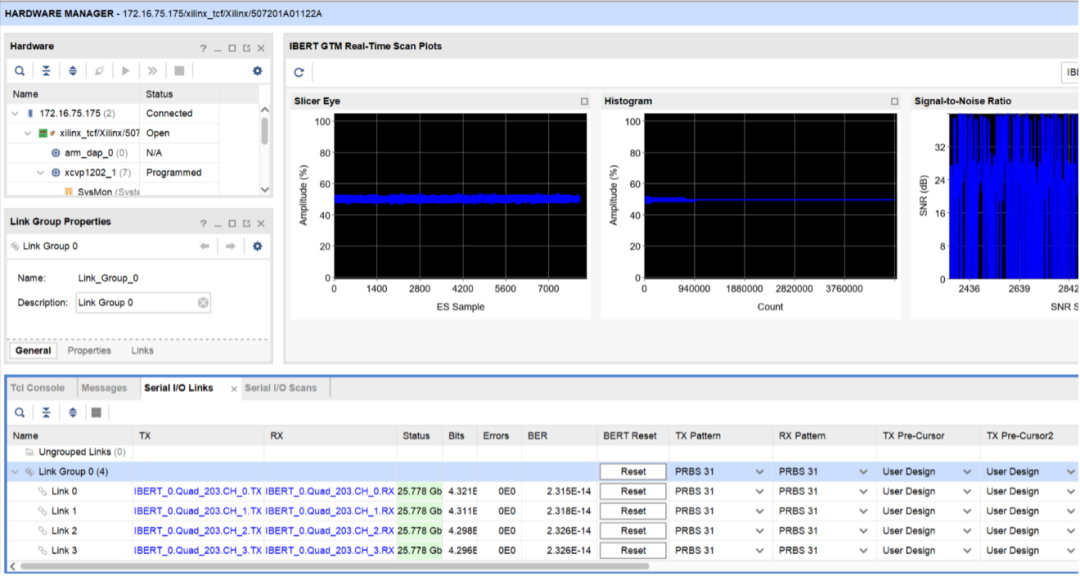

1. 工程上板之后,接下來第一步,我們要利用IP內(nèi)部自帶的in-system IBERT,先確認(rèn)鏈路是否暢通,能正常工作。點(diǎn)擊Serial I/O Link這一頁里面的create links,將Quad_203里的4路GT全部添加為New Links。

a.全部設(shè)為Near-End PCS(如果外部光模塊和光纖已經(jīng)都接上了,此處可選None;建議先做Near-End PCS,再做None)。

b.TX和RX Pattern,全部設(shè)為PRBS31(一般8B10B數(shù)據(jù)應(yīng)用選擇PRBS7,而64B66B數(shù)據(jù)則選PRBS31)。

c.分別做下整個(gè)的TX Reset和RX Reset。

d.檢查PLL鎖定,線速率和TX/RXUSERCLK頻率正確,Bits增加,Errors保持,以及BER不斷減小,即可確認(rèn)鏈路工作正常。

e.如果PLL無法鎖定,請確認(rèn)參考時(shí)鐘頻率是否已經(jīng)設(shè)置正確,以及之前添加的GT和時(shí)鐘位置約束是否已經(jīng)正確起效。

f.如果PLL鎖定,線速率也正確,但是誤碼不斷增加,尤其是在loopback關(guān)閉的模式中,請先按照GT的調(diào)試過程,如調(diào)節(jié)TX預(yù)加重等,調(diào)好板上SI,確保沒有誤碼。

2. 鏈路OK之后,將TX/RX Pattern改回User Design,并依次做一下TX Reset和RX Reset。然后我們就可以通過讀取MRMAC內(nèi)部寄存器,確認(rèn)以太網(wǎng)的link是否已經(jīng)能成功連接,起來工作了。

a.打開xsdb,然后connect。

b.再ta 1,選擇Versal xcvp1202。

c.最后就可以讀取MRMAC寄存器狀態(tài)了,下面給出了一組讀寫寄存器的示例,在做了簡單的復(fù)位后,直接讀了下以太網(wǎng)的RX狀態(tài)。

d.這里提供的是一組讀寫寄存器命令的示例,請按照自己的IP配置,讀寫相應(yīng)的寄存器。寄存器具體定義,可以在mrmac_registers.csv文件里面找到(注意下面地址經(jīng)過十六進(jìn)制和十進(jìn)制的轉(zhuǎn)換)。

mwr -force 2752053252 0x00000FFF

mwr -force 2752053256 0x40000A24

mwr -force 2752053264 0x00000033

mwr -force 2752053260 0x00000C03

mwr -force 2752053456 0x00000000

mwr -force 2752057552 0x00000000

mwr -force 2752061648 0x00000000

mwr -force 2752065744 0x00000000

mwr -force 2752053252 0x00000000

mwr -force 2752053292 0x00000001

mwr -force 2752512000 0x00000F02

mwr -force 2752512000 0x00000002

mrd -force 2752577544

mwr -force 2752055108 0xFFFFFFFF

mwr -force 2752059204 0xFFFFFFFF

mwr -force 2752063300 0xFFFFFFFF

mwr -force 2752067396 0xFFFFFFFF

mrd -force 2752055108

mrd -force 2752059204

mrd -force 2752063300

mrd -force 2752067396

e.最后,可以得到正確結(jié)果如下,說明MRMAC已經(jīng)link up了:

xsdb% mrd -force 2752055108

A4090744: 00010007

原文標(biāo)題:如何在VPK120上實(shí)現(xiàn)MRMAC以太網(wǎng)IP

文章出處:【微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5594瀏覽量

174990 -

光模塊

+關(guān)注

關(guān)注

80文章

1394瀏覽量

60098 -

Vivado

+關(guān)注

關(guān)注

19文章

831瀏覽量

68326

原文標(biāo)題:如何在VPK120上實(shí)現(xiàn)MRMAC以太網(wǎng)IP

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

無法在XDC文件中設(shè)置maxdelay約束

關(guān)于XDC約束文件,你需要知道的幾點(diǎn)

FPGA設(shè)計(jì)約束技巧之XDC約束之I/O篇(下)

如何在工程的XDC文件里加入GT位置約束

如何在工程的XDC文件里加入GT位置約束

評論