XDC 是 Xilinx Design Constraints 的簡寫,但其基礎語法來源于業界統一的約束規范SDC(最早由 Synopsys 公司提出,故名 Synopsys Design Constraints)。XDC 在本質上就是 Tcl 語言,但其僅支持基本的 Tcl 語法如變量、列表和運算符等等,對其它復雜的循環以及文件 I/O 等語法可以通過在 Vivado 中 source 一個 Tcl 文件的方式來補充。觀看視頻,了解和學習有關XDC約束,包括時序,以及物理約束相關知識。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1797瀏覽量

132170 -

語言

+關注

關注

1文章

97瀏覽量

24461 -

時序

+關注

關注

5文章

397瀏覽量

37825

發布評論請先 登錄

相關推薦

熱點推薦

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發商

精彩看點 此次收購將幫助系統級芯片 (SoC) 設計人員通過經市場檢驗的時序約束管理能力來加速設計,并提高功能約束和結構約束的正確性 ? 西門子宣布 收購 Excellicon 公司 ,將該公司用于

PCB Layout 約束管理,助力優化設計

本文重點PCBlayout約束管理在設計中的重要性Layout約束有助避免一些設計問題設計中可以使用的不同約束在PCB設計規則和約束管理方面,許多設計師試圖采用“一刀切”的方法,認為同

PanDao:實際約束條件下成像系統的初始結構的生成

摘要 :初始點的選擇對后續設計過程具有重大影響。除透鏡規格外,其它必要的實際約束條件也可能起到非常關鍵的作用。本研究采用“First Time Right”方法生成受約束的初始系統,并運用

發表于 05-07 08:57

FPGA時序約束之設置時鐘組

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析時鐘組中時鐘的時序路徑,使用set_false_path約束則會雙向忽略時鐘間的時序路徑

xilinx FPGA IOB約束使用以及注意事項

xilinx FPGA IOB約束使用以及注意事項 一、什么是IOB約束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距離IO最近的寄存器,同時位置固定。當你輸入或者輸出

淺談多目標優化約束條件下充電設施有序充電控制策略

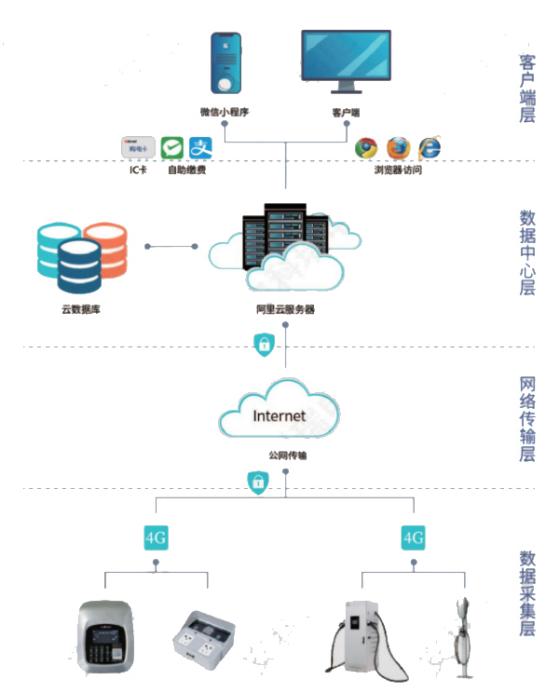

隨著電動汽車的普及,充電設施的需求日益增長,如何在多目標優化約束下實現充電設施的有序充電成為亟待解決的問題。新能源汽車的快速發展為清潔能源和可持續交通帶來了新機遇,但也引出了許多問題。其中,充電設施的有序充電控制策略在多目標優化約束條件下顯得尤為重要。

時序約束一主時鐘與生成時鐘

的輸出,對于Ultrascale和Ultrascale+系列的器件,定時器會自動地接入到GT的輸出。 1.2 約束設置格式 主時鐘約束使用命令create_clock進行創建,進入Timing

常用時序約束使用說明-v1

為了防止約束失敗,我們在Tcl輸入框中驗證,沒有告警或者錯誤說明約束的寫法是正確的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

與非門構成的基本RS觸發器的約束條件是什么

觸發器的約束條件主要涉及輸入信號和輸出信號的狀態。 以下是與非門構成的RS觸發器的一些基本約束條件: 輸入信號的約束 : RS = 0 :當R和S都為0時,觸發器保持當前狀態不變。這是因為兩個與非門的輸入都是0,輸出Q和Q'將保

sr鎖存器約束條件怎樣得出的

,并且能夠在輸入信號發生變化時保持其輸出狀態。SR鎖存器(Set-Reset Latch)是一種基本的鎖存器類型,它由兩個交叉耦合的反相器和一個S(Set)輸入和一個R(Reset)輸入組成。本文將詳細介紹SR鎖存器的約束條件,以及如何根據這些條件進

兩種SR鎖存器的約束條件

基本約束條件: SR鎖存器是一種基本的數字邏輯電路,用于存儲一位二進制信息。它有兩個輸入端:S(Set)和R(Reset),以及兩個輸出端:Q和Q'(Q的反相)。以下是SR鎖存器的基本約束

XDC約束及物理約束的介紹

XDC約束及物理約束的介紹

評論