FPGA設(shè)計流程

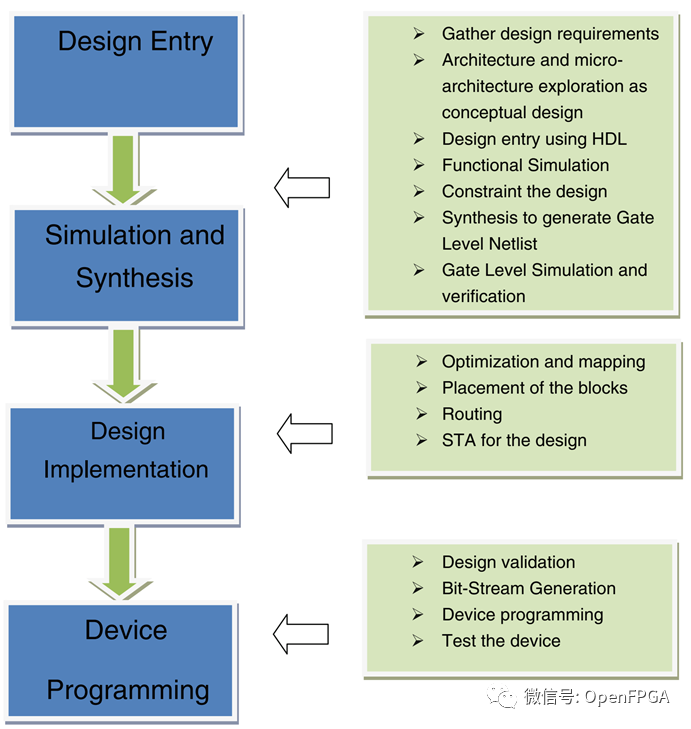

FPGA設(shè)計流程包括以下關(guān)鍵步驟,如圖9.8所示。

1. 設(shè)計輸入

2. 設(shè)計仿真與綜合

3.設(shè)計實現(xiàn)

4.設(shè)備編程。

圖9.8 FPGA設(shè)計流程

設(shè)計輸入

在設(shè)計進入之前,需要根據(jù)設(shè)計規(guī)范進行設(shè)計規(guī)劃。設(shè)計規(guī)范需要轉(zhuǎn)換為體系結(jié)構(gòu)和微體系結(jié)構(gòu)。設(shè)計架構(gòu)和微架構(gòu)包括將總體設(shè)計分解為小模塊,以實現(xiàn)預(yù)期功能。在架構(gòu)設(shè)計階段,需要估計內(nèi)存、速度和功率的需求。根據(jù)需要,需要為實現(xiàn)選擇FPGA設(shè)備。

使用Verilog(.v)或VHDL(.vhd)文件完成設(shè)計輸入。設(shè)計輸入后,需要對設(shè)計進行仿真,以確保設(shè)計的功能正確性。這稱為功能仿真。

設(shè)計仿真與綜合

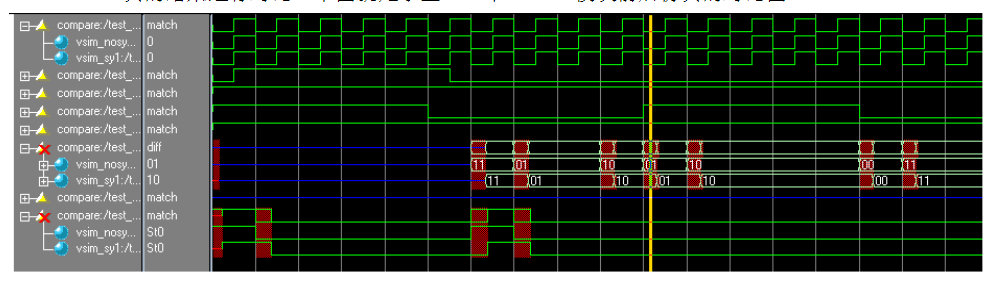

在功能仿真期間,將輸入集應(yīng)用于設(shè)計,以檢查設(shè)計的功能正確性。盡管在后期的設(shè)計周期中可能會出現(xiàn)時間或面積、電源問題,但設(shè)計師至少對設(shè)計的功能有把握。

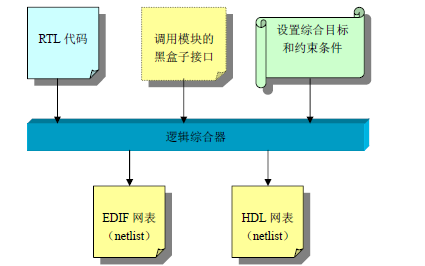

硬件設(shè)計工程師的主要目標(biāo)是生成高效的硬件。綜合是將設(shè)計抽象的一個層次轉(zhuǎn)換為另一個層次的過程。在邏輯綜合中,HDL被轉(zhuǎn)換成網(wǎng)絡(luò)表。網(wǎng)絡(luò)列表獨立于設(shè)備,可以采用標(biāo)準(zhǔn)格式,如電子設(shè)計互換格式(EDIF)。

設(shè)計實施

該設(shè)計經(jīng)歷了translate, map and place and route等步驟。在設(shè)計實現(xiàn)過程中,EDA工具將設(shè)計轉(zhuǎn)換為所需格式,并根據(jù)所需區(qū)域?qū)⑵溆成涞紽PGA。EDA工具通過使用實際邏輯單元或宏單元來執(zhí)行映射。在映射過程中,EDA工具使用宏單元、可編程互連和IO塊。專用模塊,如乘法器、DSP和BRAM,也使用供應(yīng)商工具進行映射。這些塊被放置在FPGA內(nèi)部的預(yù)定義幾何體上,并通過使用可編程互連來實現(xiàn)預(yù)期功能。這一步稱為布局和布線。

為了檢查設(shè)計計時性能以及是否滿足約束,將執(zhí)行時序分析,該分析稱為布局后STA。在STA期間,使用與可編程互連相關(guān)聯(lián)的延遲來檢查時序路徑。提取RC延遲并將其用于時序分析也稱為反向注釋。

設(shè)備編程

FPGA通過使用特定于供應(yīng)商或?qū)S械奈涣魑募M行編程。位流是需要加載到FPGA中以執(zhí)行特定硬件設(shè)計的二進制數(shù)據(jù)文件。

如果設(shè)計針對特定的FPGA,則EDA工具將生成設(shè)備利用率摘要。

用FPGA實現(xiàn)邏輯

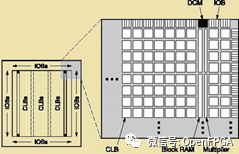

現(xiàn)代FPGA的體系結(jié)構(gòu)包括CLB陣列、塊RAM、乘法器、DSP、IOB和數(shù)字時鐘管理器(DCM)。延遲鎖定環(huán)(DLL)用于賦值具有均勻時鐘偏移的時鐘。XILINX SPARTAN系列FPGA的平面圖如下圖所示。

可配置邏輯塊

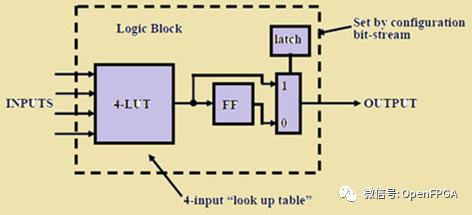

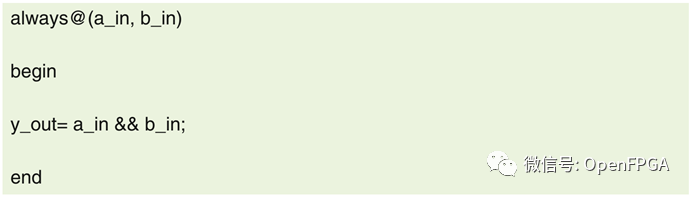

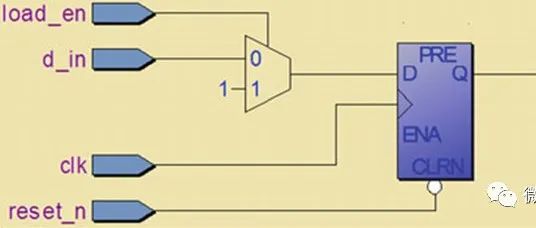

如下圖所示,基本CLB由LUT、觸發(fā)器和多路復(fù)用器邏輯組成。配置數(shù)據(jù)保存在鎖存器中。CLB體系結(jié)構(gòu)取決于供應(yīng)商,由多個LUT、觸發(fā)器、多路復(fù)用器和鎖存器組成。下面的Verilog代碼是使用單個四輸入LUT實現(xiàn)的,稱為組合邏輯。

圖9.9 Xilinx基本CLB結(jié)構(gòu)

下面的Verilog功能塊在實現(xiàn)過程中使用單LUT和單寄存器,因此該邏輯稱為時序邏輯。

圖9.9所示的CLB也用于實現(xiàn)16位移位寄存器。LUT可以級聯(lián)以設(shè)計較長尺寸的移位寄存器,也可以用于設(shè)計的流水線。

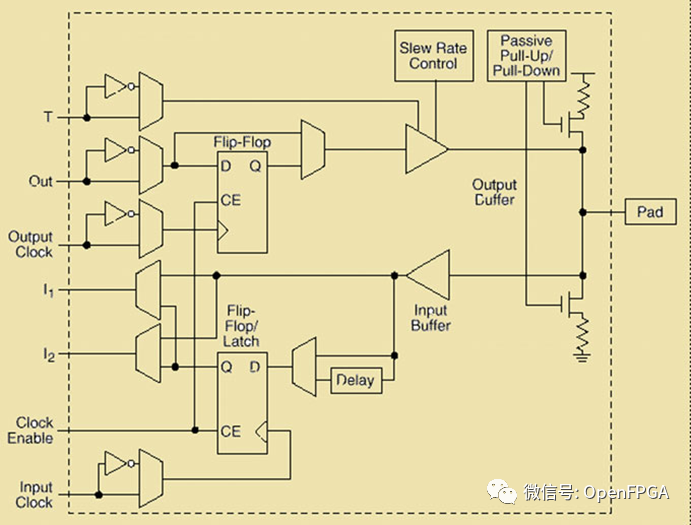

輸入-輸出塊(IOB)

輸入-輸出塊用于建立邏輯與外部世界的接口,由具有三態(tài)控制機制的寄存器和緩沖器的數(shù)量組成。該塊可用于寄存器輸入和寄存器輸出。

圖9.10 Xilinx基本IO塊

現(xiàn)代FPGA的IOB結(jié)構(gòu)非常復(fù)雜,可以包含許多IO控制支持,其中可能包括DDR、專用高速接口。基本IO塊結(jié)構(gòu)如圖9.10所示。

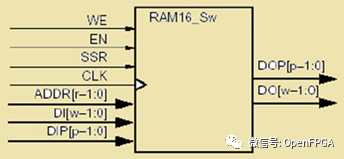

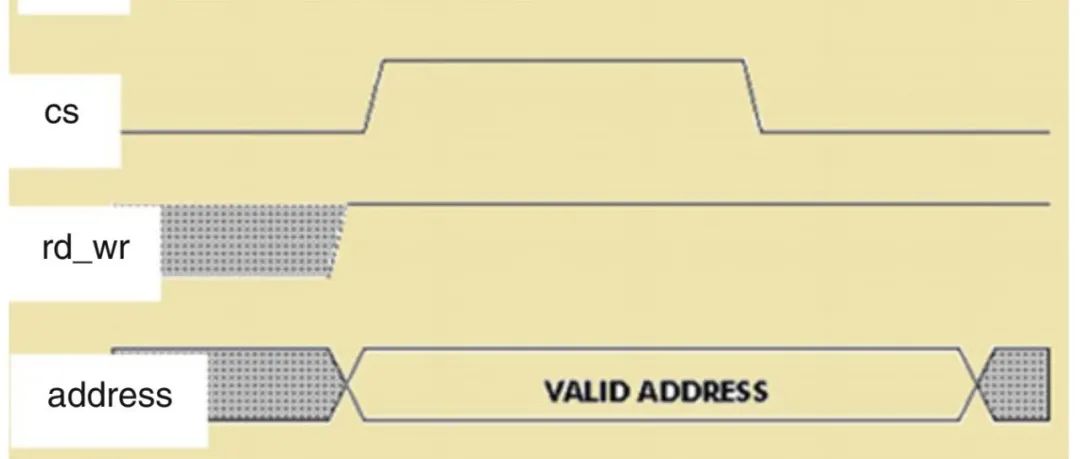

Block RAM

XILINX Spartan-7系列支持可配置18 kbit塊的形式組織的200 MHz塊RAM。每個塊RAM包含18432位,其中16kbit賦值用于數(shù)據(jù)存儲,其余2kbit賦值用于奇偶校驗。塊RAM可用作單端口存儲器或雙端口存儲器,并具有獨立的端口訪問。每個端口與獨立時鐘、時鐘啟用和寫啟用同步。讀取操作本質(zhì)上也是同步的,需要啟用時鐘。塊RAM的應(yīng)用是存儲數(shù)據(jù)、FIFO設(shè)計、緩沖區(qū)和堆棧,甚至是在設(shè)計復(fù)雜的狀態(tài)機時。單端口RAM如圖9.11所示。

圖9.11 Xilinx單端口Block RAM

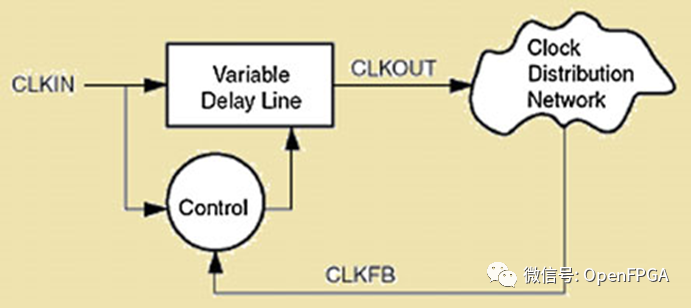

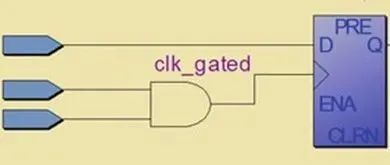

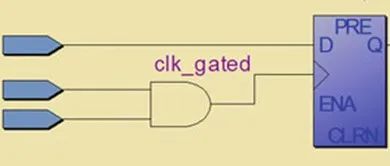

數(shù)字時鐘管理器(DCM)

Xilinx設(shè)備系列使用延遲鎖定環(huán)(DLL),Altera使用鎖相環(huán)(PLL)作為時鐘管理器。DCM、DLL的作用是提供對相移、時鐘偏移和時鐘頻率的完全控制。DCM、DLL支持以下功能。

相移?時鐘偏移消除

頻率綜合。

DCM由可變延遲線和時鐘賦值網(wǎng)絡(luò)組成,基本框圖如圖9.12所示。

圖9.12 Xilinx基本DLL塊

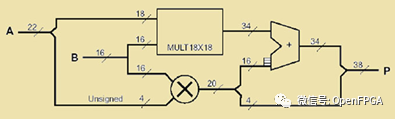

乘法器

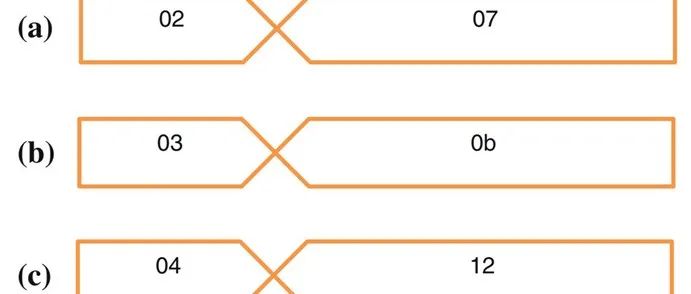

所有Spartan7 FPGA都有兩個18位輸入,并生成36位輸出。乘法器為嵌入式塊,每個設(shè)備有4~104個嵌入式乘法器塊。嵌入式乘法器的主要優(yōu)點是,與基于CLB的乘法器相比,它需要更少的功耗。它們用于以最小的通用資源實現(xiàn)快速算術(shù)函數(shù)。可以使用路由資源級聯(lián)乘法器,下圖顯示了配置為22位乘以16位的乘法器,以生成38位輸出的乘法器可用于有符號或無符號數(shù)字乘法。乘法器廣泛應(yīng)用于DSP應(yīng)用中。基本塊如圖9.13所示。

圖9.13 Xilinx基本乘法器塊

FPGA中仿真概念

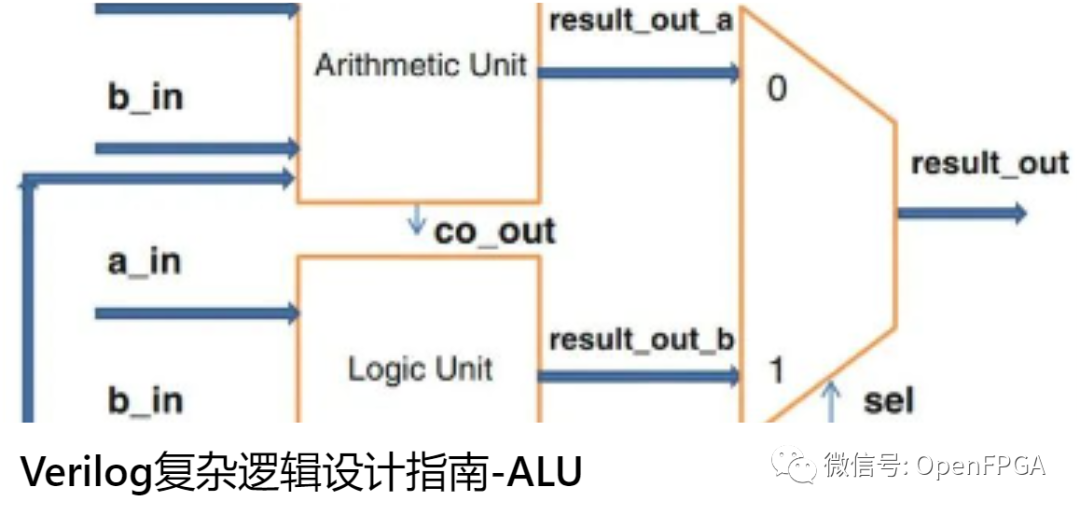

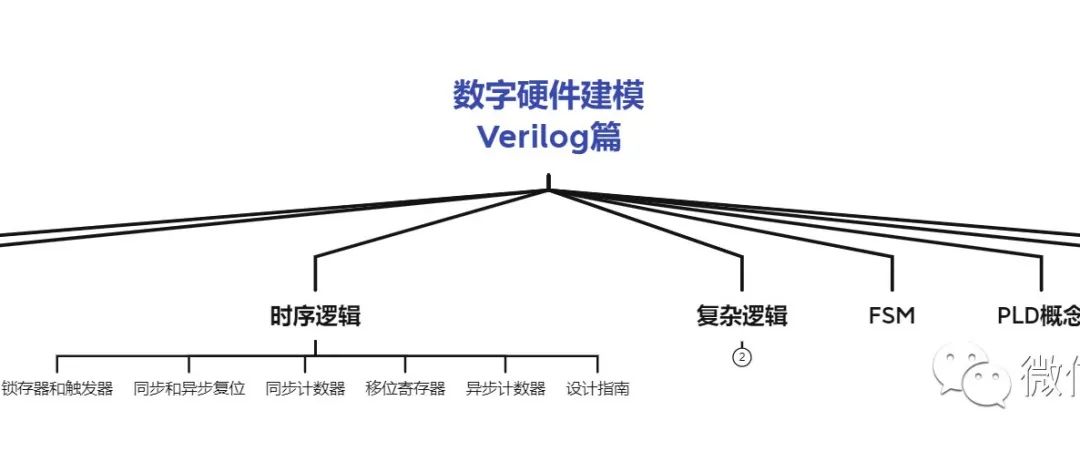

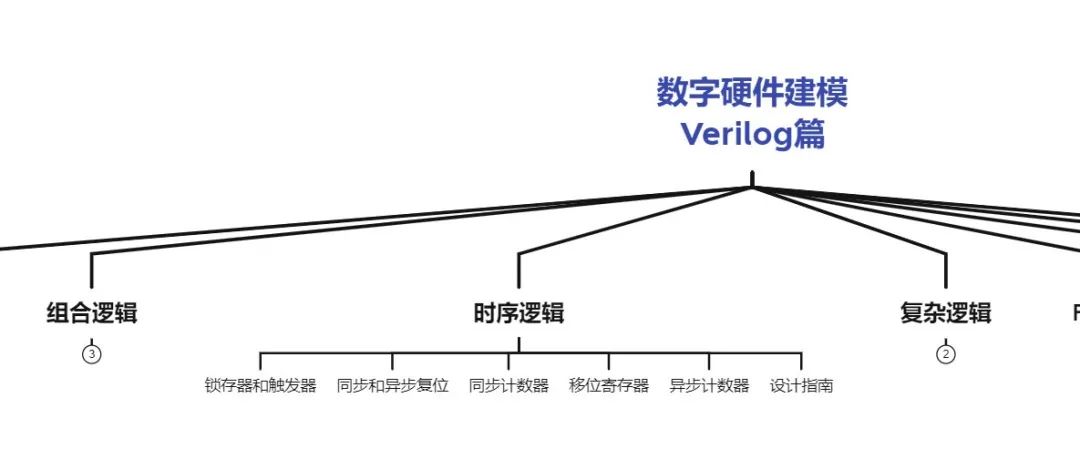

Verilog復(fù)雜邏輯設(shè)計指南-奇偶校驗生成器和校驗器及筒式移位器

Verilog時序電路設(shè)計指南

Verilog時序邏輯硬件建模設(shè)計(五)異步計數(shù)器&總結(jié)

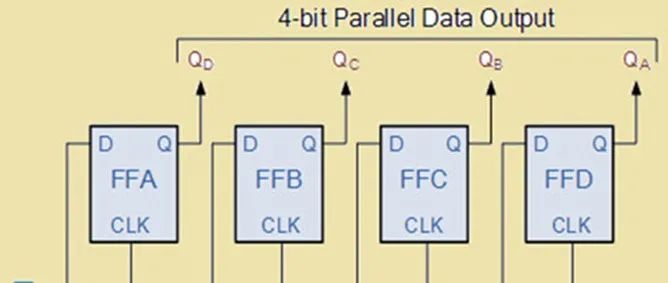

Verilog時序邏輯硬件建模設(shè)計(四)移位寄存器

Verilog時序邏輯硬件建模設(shè)計(三)同步計數(shù)器

Verilog時序邏輯硬件建模設(shè)計(二)同步和異步復(fù)位

Verilog時序邏輯硬件建模設(shè)計(一)鎖存器D-latch和觸發(fā)器Flip-Flop

Verilog組合邏輯設(shè)計指南

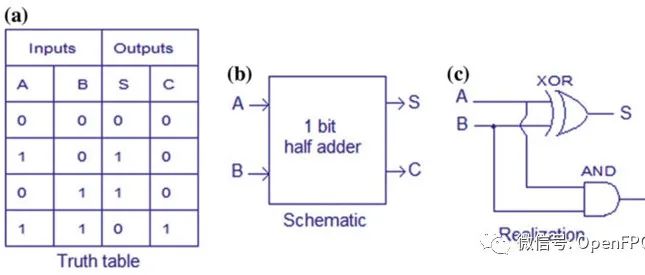

組合邏輯硬件建模設(shè)計(二)算術(shù)電路

Verilog 里面,always,assign和always@(*)區(qū)別

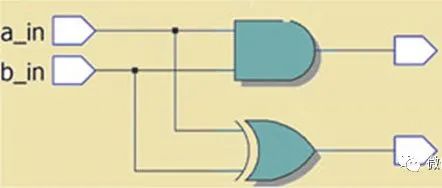

組合邏輯硬件建模設(shè)計(一)邏輯門

數(shù)字硬件建模-重新從另一方面理解Verilog(二)

數(shù)字硬件建模-從另一方面理解Verilog(一)

數(shù)字硬件建模綜述

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614268 -

仿真

+關(guān)注

關(guān)注

51文章

4241瀏覽量

135328

原文標(biāo)題:FPGA設(shè)計流程

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

華為FPGA設(shè)計流程指南

華為FPGA設(shè)計流程指南

FPGA的設(shè)計流程是怎樣的

從賽靈思FPGA設(shè)計流程看懂FPGA設(shè)計

FPGA設(shè)計流程“又臭又長”?從eda工具理解超級簡單!

FPGA的設(shè)計流程是怎么樣的?FPGA設(shè)計流程指南詳細資料免費下載

FPGA設(shè)計流程及原理

FPGA設(shè)計流程

FPGA設(shè)計流程

FPGA設(shè)計流程

評論