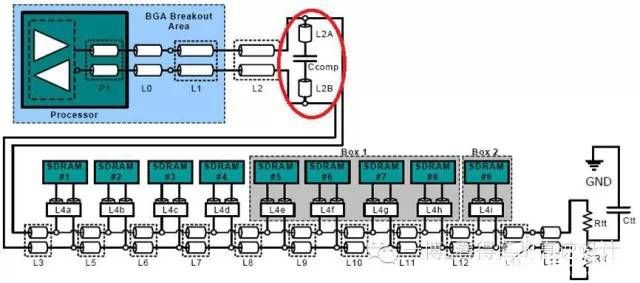

差分電容?沒看錯吧,有這種電容嗎?當然是沒有的,只是這個電容并聯在差分信號P/N中間,所以我們習慣性的叫它差分電容罷了。如下圖一中紅色框中所示即我們今天的主角,下面容我慢慢給大家介紹。

圖一

大家看到它是否有種似曾相識又不曾見過的感覺?確實,它只不過是一個普普通通的不起眼的電容罷了!但是,如果它真的只是一個普通的電容,高速先生也不屑拿出來和大家講了,其實它普通的表面隱藏著很深的道道。到底有什么呢?噓!一般人我不告訴他!

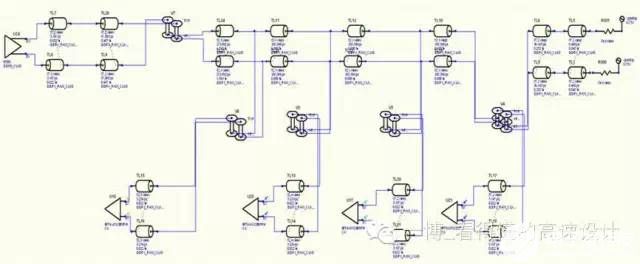

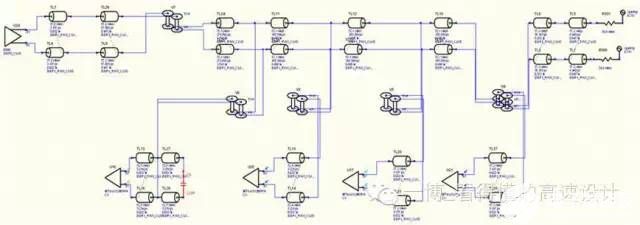

圖一是Intel平臺設計指導上經常可以看到的DDR3時鐘拓撲結構,我們也經常會在仿真實踐中去人為的添加這個差分電容,如下圖二時鐘信號一拖四所示為我們在設計中看到的一個真實案例。

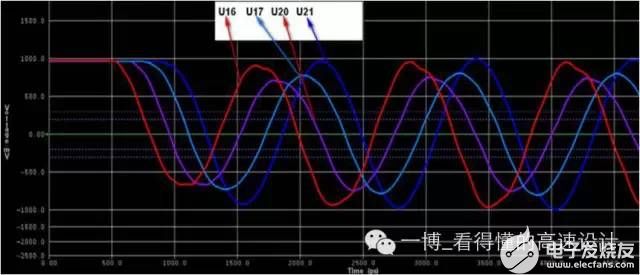

圖二 無差分電容的時鐘信號拓撲及波形

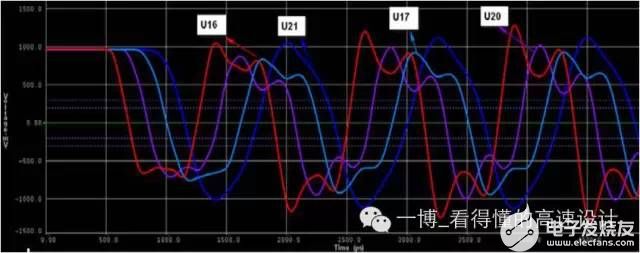

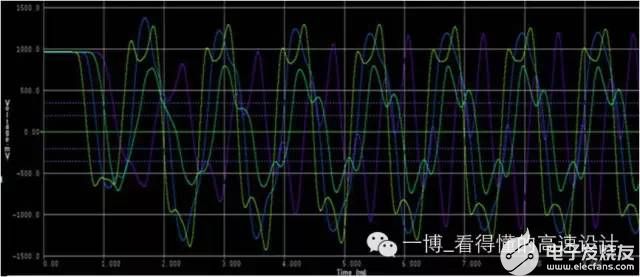

雖然看起來這個波形還湊合,沒有太大的問題,但還是有優化的余地(工程師的強迫癥又來了,真是傷不起啊!),可以通過在前端并聯一個電容來優化,如下圖三所示為并聯了2.2pF差分電容后的拓撲結構和仿真波形。

圖三 有差分電容的拓撲結構和波形

在前端加了差分電容后,雖然上升沿有微小的變緩,但波形真的是呈現了一個完美的正弦波曲線,振蕩消除了,實在是苦逼的工程師們居家(埋頭實驗室)旅行(客戶現場出差)、殺人滅口(消除反射等)之必備良方。此優化設計也已經投入使用,在加了這個電容后系統能穩定運行在800MHz的頻率,如果沒有焊接這個電容,系統只能穩定運行在667MHz,運行到800MHz時系統時有錯誤發生。

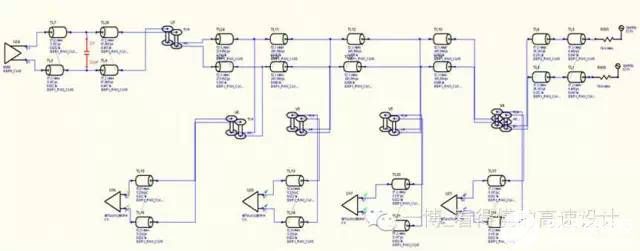

看到這里,一些腦洞大開的工程師可能會問,這個電容的位置有什么講究嗎?我可不可以把這個電容放在最后面那個顆粒?高速先生就喜歡有人提這種高質量的問題。下面還是看看仿真結果吧。

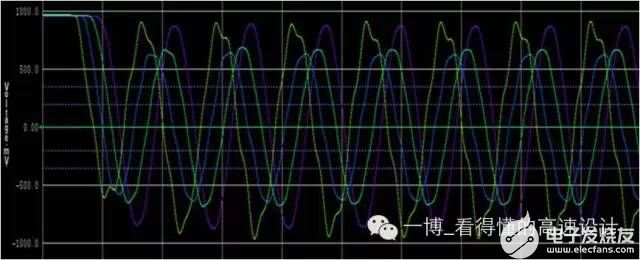

首先看看將電容放在第一個顆粒處的仿真結果,如下圖四所示。

圖四、電容在第一個顆粒處的拓撲和波形

可以看出此時波形已經沒有放在前端(靠近發送芯片端)時的完美了,甚至出現了振蕩的小苗頭。接著把電容放在最后一片顆粒處,仿真結果如下圖五所示。

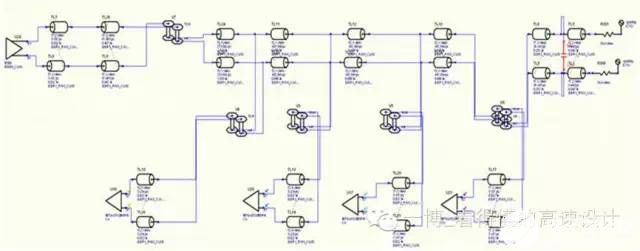

圖五 電容在最后處的拓撲和波形

此時波形振蕩甚至比沒有電容的效果還明顯,仿真結果表明此電容還是不要放在末端為好,最好的位置還是靠近發送端吧。

-

DDR3

+關注

關注

2文章

284瀏覽量

43128 -

差分電容

+關注

關注

0文章

6瀏覽量

8907 -

時鐘信號

+關注

關注

4文章

468瀏覽量

29213

發布評論請先 登錄

【RK3568+PG2L50H開發板實驗例程】FPGA部分 | DDR3 讀寫實驗例程

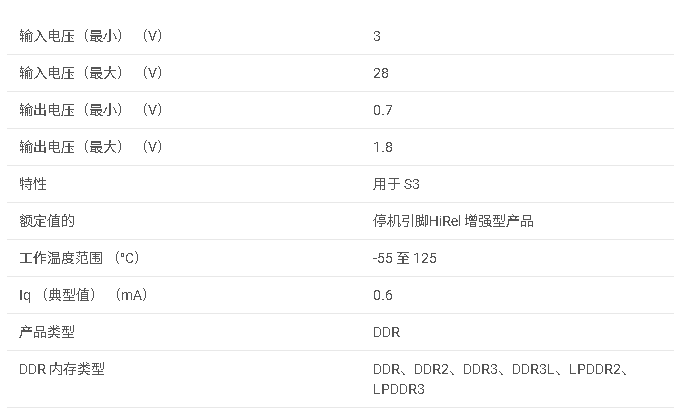

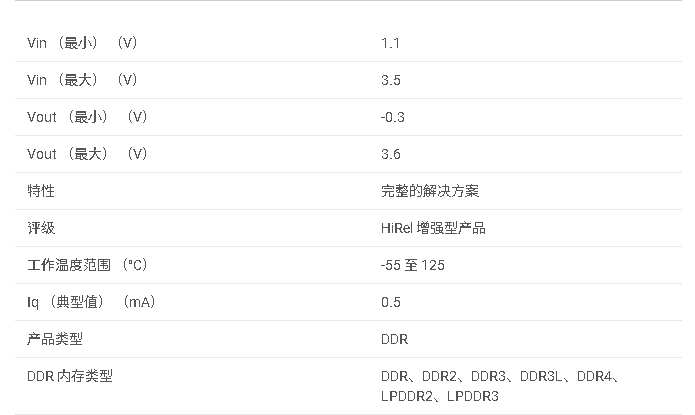

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據手冊

TPS51216-EP 增強型產品 完整的 DDR2、DDR3 和 DDR3L 內存電源解決方案 同步降壓控制器數據手冊

TPS51200-EP 灌電流/拉電流 DDR 終端穩壓器數據手冊

DDR3 SDRAM配置教程

DDR3系列之時鐘信號的差分電容

DDR3系列之時鐘信號的差分電容

評論