在FPGA的HR BANK上供電3.3V,先就其差分端口而言,LVDS電平以及LVDS25電平能否約束到這個BANK上呢?

解決這個問題前,先了解下

1、什么是HR Bank以及HP bank:

Xilinx的7系列FPGA有兩種IO Bank:HP(High Performace)和HR(High Range)。HP(high-performance)I/O banks的設計目的是為了獲取更高的Memory及chip-to-chip間的傳輸速率;而HR(high-range)I/O banks的設計目的是為了更寬的I/O電平標準。兩種BANK的IO口電壓不同,其中HR I/O Banks的VCCO電壓最大為3.3V,HP I/O banks的VCCO電壓最大為1.8V。特別是初次使用7系列時,在硬件設計中特別要注意它們I/O口的最大工作電壓,一不注意就會把電壓搞錯,導致FPGA不能正常工作。

2、HR和HP banks的LVDS電平

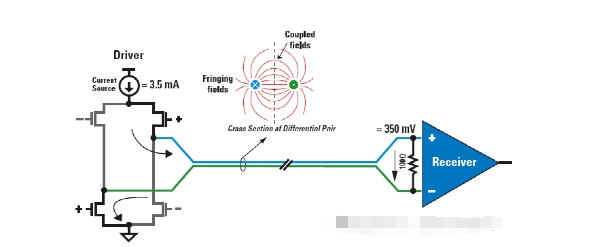

當兩個banks的I/O口作為LVDS電平時,HR banks的I/O電壓VCCO只能為2.5V,HP banks的I/O口電壓為1.8V。兩個banks支持LVDS的標準不同,HR I/O banks的I/O只能分配LVDS_25標準,HP分配為LVDS標準。

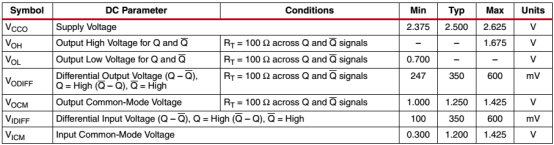

LVDS_25的直流特性如下表所示。

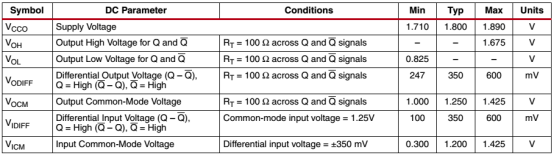

LVDS的直流特性如下表所示。

xilinx 7系列芯片不再支持LVDS33電平,在VCCO電壓為3.3V的情況下無法使用LVDS25接口。

有些設計者想通過在軟件中配置為LVDS25,實際供電3.3V來實現LVDS33也是無效的,原因是xilinx 7系列芯片在IO配置方面增加了過壓保護,因而無法通過欺騙綜合軟件的方式強行配置IO,具體參見

7-Series SelectIO Resources Guide, page 100, Note 2 states:

"if the voltage exceeds 2.85V, the outputs will be in a high-Z state. The device should always be operated within the recommended operating range as specified in the 7 series FPGA data sheets."

雖然在VCCO為3.3V情況下無法輸出LVDS25,但可以作為輸入進行使用,具體參見AR#43989 https://www.xilinx.com/support/answers/43989.html

即使VCCO電平不是1.8V,在HP I / O bank中也可以使用LVDS輸入。LVDS輸出(因此雙向LVDS)只能用于1.8V供電的組。

同樣,即使VCCO電平不是2.5V,也可以在HR I / O bank中使用LVDS_25輸入。LVDS_25輸出(因此雙向LVDS_25)只能用于2.5V供電的bank。

查了上述說法之后,我們自己試驗下:

實驗驗證:

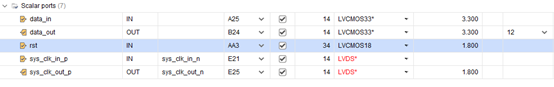

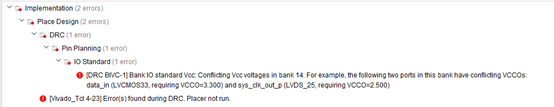

Bank14為HR Bank,差分輸入以及差分輸出使用LVDS電平:

提示說明,LVDS電平不支持HRbank。

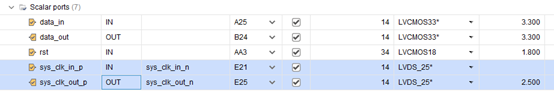

差分輸入以及差分輸出使用LVDS25電平:

提示VCCOs矛盾,輸出差分時鐘sys_clk_out_p,要求VCCO=2.5V,但對輸入并沒有這種要求。

驗證了:

即使VCCO電平不是1.8V,在HP I / O bank中也可以使用LVDS輸入。LVDS輸出(因此雙向LVDS)只能用于1.8V供電的組。

同樣,即使VCCO電平不是2.5V,也可以在HR I / O bank中使用LVDS_25輸入。LVDS_25輸出(因此雙向LVDS_25)只能用于2.5V供電的bank。

審核編輯 :李倩

-

FPGA

+關注

關注

1645文章

22034瀏覽量

617920 -

Xilinx

+關注

關注

73文章

2184瀏覽量

125215 -

電平

+關注

關注

5文章

367瀏覽量

40562

原文標題:FPGA學習-FPGA的LVDS電平以及LVDS25電平能在HR Bank上使用嗎?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

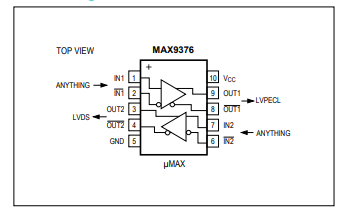

MAX9374/MAX9374A差分LVPECL至LVDS變換器技術手冊

MAX9376 LVDS/任意邏輯至LVPECL/LVDS、雙路電平轉換器技術手冊

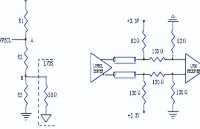

差分晶振-LVPECL到LVDS的連接

LVDS電平以及LVDS25電平能否約束到這個BANK上呢?

LVDS電平以及LVDS25電平能否約束到這個BANK上呢?

評論