概述

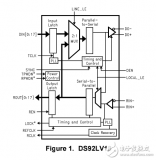

MAX9376是全差分、高速、LVDS/任何輸入至LVPECL/LVDS雙通道轉換器,適用于高達2GHz的信號速率。一個通道是LVDS/任何輸入至LVPECL轉換器,另一個通道是LVDS/任何輸入至LVDS轉換器。MAX9376具有超低的傳播延遲和高速度,因此非常適合各種高速網絡路由和背板應用。

MAX9376可接受電源軌內最小幅度為100mV的任何差分輸入信號。輸入完全符合LVDS、LVPECL、HSTL和CML差分信號標準。LVPECL輸出有足夠的電流來驅動50Ω傳輸線。LVDS輸出符合ANSI EIA/TIA-644 LVDS標準。

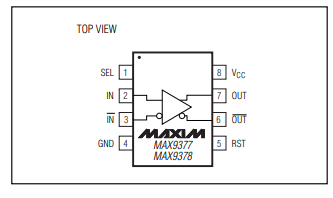

MAX9376采用10引腳 μMAX?封裝,采用+3.3V單電源供電,工作溫度范圍為-40°C至+85°C。

數據表:*附件:MAX9376 LVDS 任意邏輯至LVPECL LVDS、雙路電平轉換器技術手冊.pdf

應用

- 背板邏輯標準轉換

- DLCs

- DSLAM背板

- 局域網(LAN)

- LVDS至LVPECL、LVPECL至LVDS

- 上/下變頻器

- WANs

特性

- 支持2GHz開關頻率

- 支持LVDS/LVPECL/任何輸入

- 傳播延遲:421ps(典型值)

- 脈沖偏斜:30ps(最大值)

- 隨機抖動:2ps

RMS(最大值) - 差分輸入最低100mV,確保符合交流規格

- 溫度補償LVPECL輸出

- 電源工作范圍:+3.0V至+3.6V

2kV ESD保護(人體模型)

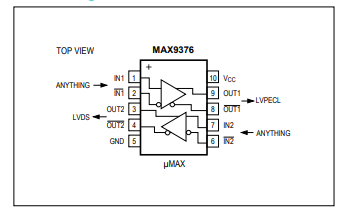

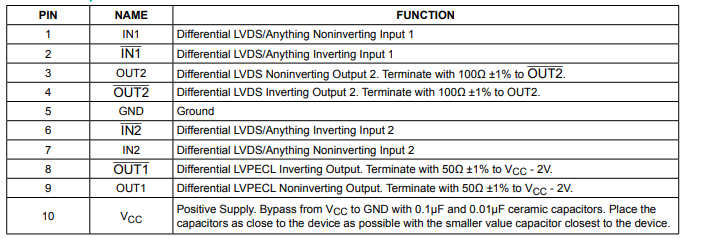

引腳配置描述

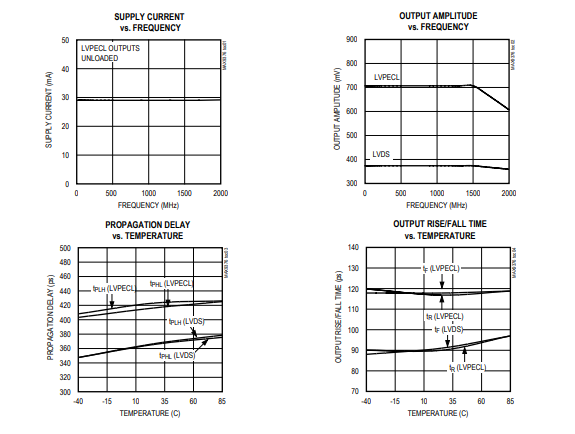

典型操作特性

應用信息

LVPECL輸出端端接

將MAX9376的LVPECL輸出端以50Ω電阻端接到(V_{CC} - 2V ),或使用等效的戴維南端接方式。分別對OUT1和OUT2進行相同的端接,以降低輸出失真。當從差分輸出端引出單端信號時,請勿同時端接OUT1和OUT2。

確保輸出電流不超過絕對最大額定值中的規定值。在所有工作條件下,都應遵守器件的總熱限制。

LVDS輸出端端接

MAX9376的LVDS輸出為電流導向型器件,輸出電壓無需通過端接電阻來產生。終端電阻應與傳輸線的差分阻抗匹配。輸出電壓電平取決于端接電阻上的電壓降。MAX9376針對點對點接口進行了優化,端接電阻值可在90Ω至132Ω之間變化,具體取決于傳輸介質的特性阻抗。

電源去耦

使用高頻表面貼裝陶瓷電容將 V_{CC} 旁路至地,電容值為0.1μF和0.01μF 。盡可能將電容放置在靠近器件引腳的位置,0.01μF的電容應離器件引腳最近。

走線

電路基板的走線布局對于保持高速差分信號的信號完整性至關重要。保持信號完整性可通過減少信號反射和偏斜,以及提高共模噪聲抗擾度來實現。

信號反射是由50Ω特性阻抗的走線不連續造成的。通過縮短差分走線之間的距離、不使用尖銳轉角或過孔來避免不連續情況。保持走線間距一致也能提高共模噪聲抗擾度。通過使差分走線的電氣長度匹配來減少信號偏斜。

-

轉換器

+關注

關注

27文章

9026瀏覽量

151524 -

lvds

+關注

關注

2文章

1124瀏覽量

67379 -

LVPECL

+關注

關注

2文章

45瀏覽量

18321

發布評論請先 登錄

LVPECL、VML、CML、LVDS 與LVDS之間的接口連接轉換

MAX9376,pdf datasheet (LVDS/An

LVDS和CML與LVPECL的同種差分邏輯電平之間的互連教程

SN65LVDS20/SN65LVP20帶使能功能的LVPECL和LVDS中繼器/轉換器數據表

SN65LVELT23 3.3雙通道差分LVPECL/LVDS緩沖器至LVTTL轉換器數據表

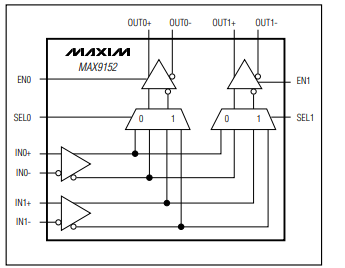

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉點開關技術手冊

MAX9375單LVDS/任意邏輯至LVPECL轉換器技術手冊

MAX9376 LVDS/任意邏輯至LVPECL/LVDS、雙路電平轉換器技術手冊

MAX9376 LVDS/任意邏輯至LVPECL/LVDS、雙路電平轉換器技術手冊

評論