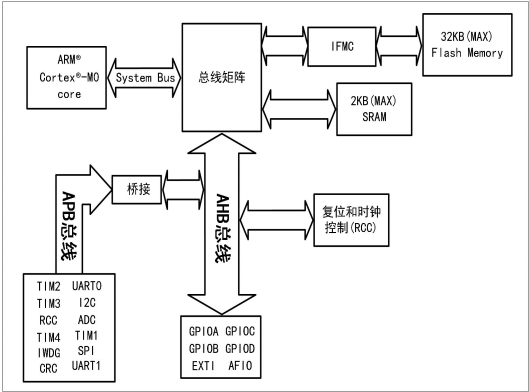

1存儲器和總線構(gòu)架

1.1系統(tǒng)構(gòu)架

l一個驅(qū)動單元

nCortex?-M0內(nèi)核系統(tǒng)總線(S-bus)

l四個被動單元

n內(nèi)部SRAM

n內(nèi)部Flash閃存存儲器

nAHB所連接的所有外設(shè)

nAHB到APB的橋,它連接的所有APB設(shè)備

1.1.1系統(tǒng)總線

此總線連接Cortex?-M0內(nèi)核的系統(tǒng)總線(外設(shè)總線)到總線矩陣,總線矩陣協(xié)調(diào)內(nèi)核與外部總線的訪問。

1.1.2 AHB/APB橋(APB)

“AHB/APB橋”在AHB和APB總線間提供同步連接。AHB和APB的操作速度均與系統(tǒng)時鐘SYS_CLK同步。

連接到每個橋的不同外設(shè)的地址映射請參考表1-1。在每一次復位過程當中,除SRAM以外的所有外設(shè)都被關(guān)閉。

注意:對AHB或APB總線上的寄存器進行8位或者16位操作時,由于數(shù)據(jù)字節(jié)以小端格式存放在存儲器中,故有:

1.讀操作:該操作會被自動轉(zhuǎn)換成32位的讀,對應的數(shù)據(jù)將按照小端格式被存儲在中間變量;

2.寫操作:總線和橋會自動將8位或者16位的寫入數(shù)據(jù)擴展,并將缺失的高位補0,以配合

32位的向量。

1.2存儲器組織

程序存儲器、數(shù)據(jù)存儲器、寄存器和輸入輸出端口被組織在同一個4GB的線性地址空間內(nèi)。

數(shù)據(jù)字節(jié)以小端格式存放在存儲器中。一個字里的最低地址字節(jié)被認為是該字的最低有效字節(jié),而最高地址字節(jié)是最高有效字節(jié)。

1.3嵌入式SRAM

PT32x00x內(nèi)置最大2K字節(jié)的SRAM。它可以以字節(jié)、半字(16位)或全字(32位)訪問。SRAM的起始地址是0x2000 0000。

1.4嵌入式Flash閃存

PT32x00x內(nèi)置的閃存存儲器可以用于在線編程(ICP),在線編程(In-Circuit Programming–ICP)方式用于更新閃存存儲器的全部內(nèi)容,它通過SWD協(xié)議或系統(tǒng)加載程序(Bootloader)下載

用戶應用程序到微控制器中。ICP是一種快速有效的編程方法,消除了封裝和管座的困擾。

高性能的閃存模塊有以下的主要特性:

最大32K字節(jié)的閃存存儲器結(jié)構(gòu),下面羅列存儲器的組成部分:

l主程序區(qū)

lBootloader區(qū)

l用戶配置區(qū)

通過片內(nèi)閃存控制器IFMC可以便捷的控制Flash閃存,有關(guān)IFMC的詳細信息,請參考”16片內(nèi)閃存控制器(IFMC)”。

注意:PT32x00x不支持中斷向量表重映射,故不支持IAP應用。

1.5啟動配置

PT32x00x支持兩種啟動模式:

l從主程序區(qū)啟動

l從Bootloader區(qū)啟動

這兩種啟動模式都基于Flash片內(nèi)閃存,通過特定的程序配置以實現(xiàn)不同的啟動模式,而無需外部硬件的介入。

注意:默認從主程序區(qū)啟動,關(guān)于從Bootloader 區(qū)啟動的詳細信息,請參考”16.3.6系統(tǒng)啟動配置”

審核編輯:湯梓紅

-

存儲器

+關(guān)注

關(guān)注

38文章

7637瀏覽量

166519 -

內(nèi)核

+關(guān)注

關(guān)注

3文章

1410瀏覽量

41143 -

sram

+關(guān)注

關(guān)注

6文章

783瀏覽量

115696 -

總線

+關(guān)注

關(guān)注

10文章

2953瀏覽量

89403

發(fā)布評論請先 登錄

Vishay Opto VEML6031X00汽車級環(huán)境光傳感器

EE-302:ADSP-BF53x Blackfin處理器與NAND FLASH存儲器的接口

TMS320C672x DSP外部存儲器接口(EMIF)用戶指南

什么是ROM存儲器的定義

使用SD Flash為TMS320C28x器件編程外部非易失性存儲器

內(nèi)存儲器分為隨機存儲器和什么

帶備份存儲器的獨立RTC,帶低成本MSP430 MCU應用說明

PLC主要使用的存儲器類型

內(nèi)部存儲器有哪些

PT32x00x存儲器和總線構(gòu)架說明

PT32x00x存儲器和總線構(gòu)架說明

評論