除了性能之外,可靠性和堅固性是SiC MOSFET討論最多的話題。我們將堅固性定義為器件承受特定的特殊壓力事件的能力,例如,短路能力或脈沖電流處理能力。可靠性指器件在目標壽命內額定工作條件下的穩(wěn)定性。與可靠性相關的現象包括某些電氣參數的漂移或毀壞性的故障。對于硬故障,通常以FIT率的形式進行量化。FIT率說明了某一類型的設備在一定時期內預期有多少次故障。目前,宇宙射線效應主要制約著大功率硅器件的FIT率。

就SiC而言,還需要考慮由于柵氧化層電場應力造成的柵極氧化層可靠性問題。如下圖所示,SiC的總FIT率是宇宙射線FIT率和氧化物FIT率之和。對于宇宙射線失效率,可以通過實驗的方式得到某種技術的FIT率,根據這些結果并結合應用的目標,就可以實現一個符合目標FIT率的產品設計。優(yōu)化漂移區(qū)的電場設計通常可以實現低的FIT率。對于氧化物的FIT率,則需要應用一個篩選過程來降低FIT率,因為與硅相比,SiC的缺陷密度仍然相當高。然而,即使在我們的硅功率器件中,柵極氧化物的篩選仍然是作為一種質量保證措施而采用的。

SiC MOS器件的柵極氧化物可靠性的挑戰(zhàn)是,在某些工業(yè)應用給定的工作條件下,保證最大故障率低于1 FIT,這與今天的IGBT故障率相當。

由于碳化硅和硅材料上生長的二氧化硅(SiO2)的質量和特性幾乎是相同的,因此理論上相同面積和氧化層厚度的Si MOSFET和SiC MOSFET可以在相同的時間內承受大致相同的氧化層電場應力(相同的本征壽命)。但是,這只有在器件不包含與缺陷有關的雜質,即非本征缺陷時才有效。與Si MOSFET相比,現階段SiC MOSFET柵極氧化物中的非本征缺陷密度要高得多。

電篩選降低了可靠性風險

與沒有缺陷的器件相比,有非本征缺陷的器件更早出現故障。無缺陷的器件雖然也會疲勞失效,但壽命很長。通常情況下,足夠厚的無缺陷氧化層的本征失效時間比正常應用下的使用時間要長幾個數量級。因此,在典型的芯片壽命內,氧化物的FIT率完全由非本征缺陷決定。

保證碳化硅MOSFET的柵極氧化層具有足夠的可靠性的挑戰(zhàn)是——如何將受非本征缺陷影響的器件數量,從最初工序結束時的高比例(如1%),減少到產品發(fā)運給客戶時可接受的低比例(如10ppm)。實現這一目標的一個公認的方法是使用電篩選。

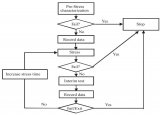

在電篩選過程中,每個器件都處于柵控應力模式。應力模式的選擇方式是,具有嚴重缺陷的器件將失效,而沒有這些缺陷的器件,或只有非關鍵性缺陷的器件可以通過測試。未通過篩選的器件將從產線移除。通過這種方式,我們將潛在的可靠性風險轉換為產量損失。

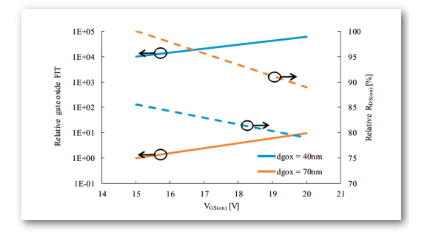

為了使器件能夠承受一定的柵極應力,柵極氧化層需要有一個特定的最小厚度。如果柵極氧化層的厚度太低,器件在篩選過程中會因為疲勞而出現本征失效,或者在篩選后出現閾值電壓和溝道遷移率下降的情況。另一方面,更厚的柵極氧化層會增加閾值電壓,并在給定的VGS(on)條件下降低溝道電導率。下圖說明了柵極氧化物FIT率和器件性能之間的權衡,這在中也有討論。

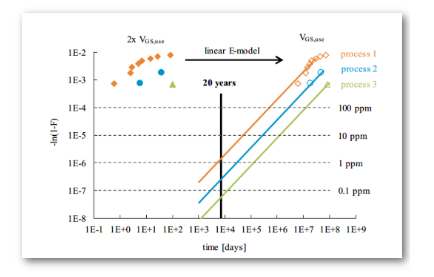

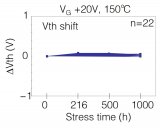

我們已經投入了大量的時間和樣品,得到了SiC MOSFET的柵氧化可靠性的大量數據。舉例來說,我們對通過電篩選的SiC MOSFET分成三組,每組施加不同的正負柵極應力偏置,在150℃下測試了的通態(tài)可靠性100天。每組樣品有1000個器件。下圖顯示了不同柵極氧化工藝條件下的結果,最終量產的工藝可靠性方面有明顯改進。

使用初始的工藝條件,在兩倍于建議的30V柵極偏壓下,1000個器件中只有不到10個失效。改進的實施工藝將這一數字減少到30V時僅有一個故障,25V和-15V時的故障為零。惟一的一個失效是非固有失效,然而,這并不關鍵,因為在額定的柵極偏壓使用條件下,失效發(fā)生的時間點會遠遠超過規(guī)定的產品壽命。

當然,除了評估通態(tài)氧化物的可靠性外,評估斷態(tài)氧化物的應力也很重要,因為SiC功率器件中的電場條件比硅功率MOS元件更接近SiO2的極限。

屏蔽是導通電阻和可靠性之間的權衡

關鍵的策略是通過對深p阱的適當設計來有效地屏蔽敏感的氧化物區(qū)域。屏蔽的效率是導通電阻和可靠性之間的權衡。在溝槽MOSFET中,深p阱在MOSFET的溝道區(qū)下面形成類似JFET的結構,可以有效地促進屏蔽。這種JFET(結型場效應晶體管)為導通電阻增加了一個額外的分量,主要取決于掩埋的p區(qū)之間的距離和摻雜。這種屏蔽結構的設計特點對于避免關斷狀態(tài)下的柵極氧化層退化或柵極氧化層擊穿至關重要。

為了驗證CoolSiC? MOSFET的斷態(tài)可靠性,我們在150°C、VGS=-5V和VDS=1000V的條件下對超過5000個1200V的SiC MOSFET進行了100天的應力測試。這些條件對應于工業(yè)應用已經夠嚴酷了。受器件的擊穿電壓的限制,VDS不能再繼續(xù)增加。

在更高的漏極電壓下進行測試會使結果失真,因為其他故障機制,如宇宙射線引起的故障可能出現。結果是,在這次斷態(tài)可靠性測試中,沒有一個被測試的器件發(fā)生故障。由于650V器件遵循與1200V器件相同的設計標準,因此預計會有相同的可靠性。

-

SiC

+關注

關注

30文章

2923瀏覽量

63107 -

Fit

+關注

關注

0文章

15瀏覽量

9349 -

SiC功率器件

+關注

關注

1文章

15瀏覽量

9261

發(fā)布評論請先 登錄

相關推薦

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

SiC-SBD關于可靠性試驗

SiC MOSFET:經濟高效且可靠的高功率解決方案

SiC MOSFET的器件演變與技術優(yōu)勢

如何消除SiC MOSFET——柵極電路設計中的錯誤及其對穩(wěn)健性的影響

SiC-MOSFET的可靠性

8.2.11 氧化層可靠性∈《碳化硅技術基本原理——生長、表征、器件和應用》

使用Keithley 4200-SCS半導體表征系統進行氧化物可靠性測試

金屬氧化物和柔性石墨烯MOS的區(qū)別

SiC MOS器件柵極氧化物可靠性的挑戰(zhàn)

SiC MOS器件柵極氧化物可靠性的挑戰(zhàn)

評論