引言:本文我們介紹GTX/GTH收發(fā)器時(shí)鐘架構(gòu)應(yīng)用,該文內(nèi)容對(duì)進(jìn)行PCIe和XAUI開發(fā)的FPGA邏輯設(shè)計(jì)人員具有實(shí)際參考價(jià)值,具體介紹:

PCIe參考時(shí)鐘設(shè)計(jì)

XAUI參考時(shí)鐘設(shè)計(jì)

1.PCIe參考時(shí)鐘設(shè)計(jì)

1.1參考輸入時(shí)鐘

GTX/GTH收發(fā)器使用參考時(shí)鐘產(chǎn)生內(nèi)部比特時(shí)鐘用于發(fā)送和接收數(shù)據(jù)。收發(fā)器使用PCIe模式時(shí),推薦的參考時(shí)鐘為100MHz,參考時(shí)鐘也可以選擇125MHz或者250MHz。

參考輸入時(shí)鐘經(jīng)過(guò)IBUFDS_GTE2原句驅(qū)動(dòng)GTX/GTH收發(fā)器參考時(shí)鐘。如果TX buffer旁路,TXOUTCLKSEL必須選擇GTX/GTH收發(fā)器的參考時(shí)鐘作為TXOUTCLK源時(shí)鐘。該參考時(shí)鐘在電源上電后必須保持穩(wěn)定和自由運(yùn)行。

對(duì)于異步時(shí)鐘應(yīng)用,最差的頻率偏移必須保持在±600ppm或者±300ppm。GTX/GTH收發(fā)器內(nèi)部產(chǎn)生的25MHz時(shí)鐘來(lái)自參考時(shí)鐘分頻,用于同步器和定時(shí)器以及各種GTX/GTH收發(fā)器操作,如復(fù)位、電源管理、速率改變、OOB等。

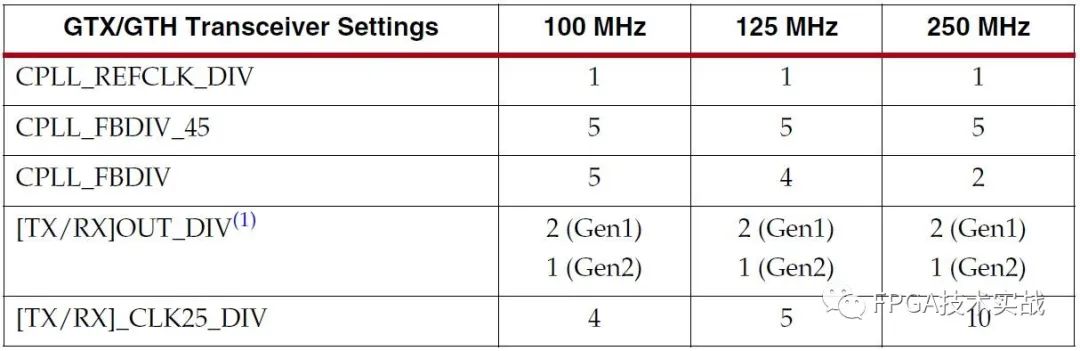

PCIe參考時(shí)鐘推薦的CPLL分頻器和時(shí)鐘設(shè)置如圖1所示。

圖1、PCIe參考時(shí)鐘推薦的CPLL分頻器和時(shí)鐘設(shè)置

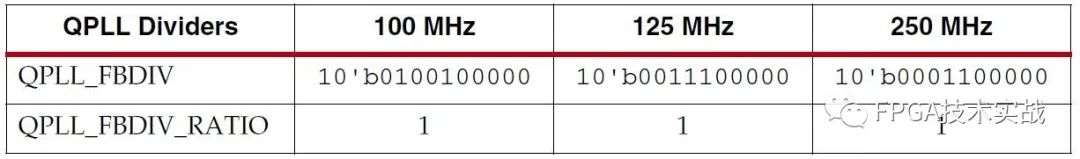

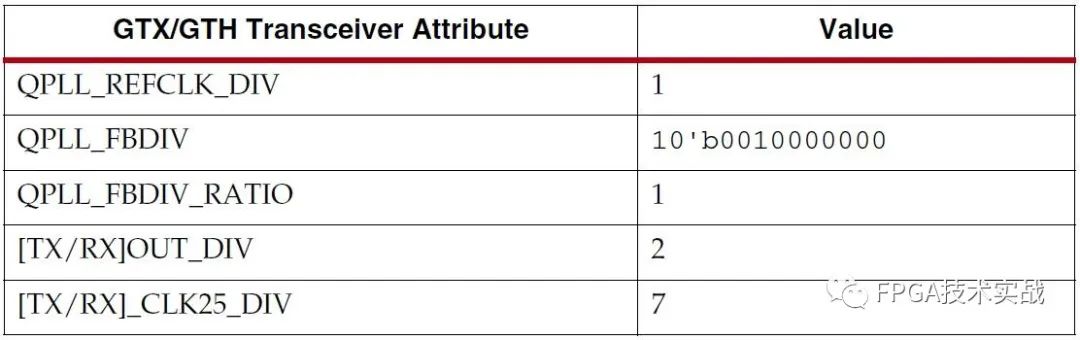

對(duì)于PCIe Gen3應(yīng)用,QPLL必須使用,圖2顯示了推薦的QPLL配置。

圖2、推薦的QPLL設(shè)置

1.2 并行時(shí)鐘(PCLK)

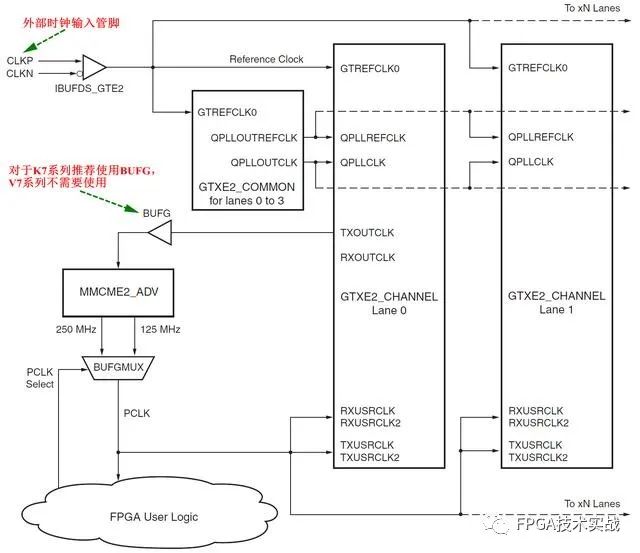

在PCIe模式中,PCLK是FPGA邏輯接口,用來(lái)同步并行接口數(shù)據(jù)傳輸。在Gen1應(yīng)用中推薦的PCLK時(shí)鐘為125MHz,在Gen2和Gen3中推薦的PCLK為250MHz。通常一個(gè)MMCME2_ADV通過(guò)參考輸入時(shí)鐘產(chǎn)生125MHz和250MHz時(shí)鐘。當(dāng)MMCME2_ADV使用時(shí),用戶可以通過(guò)BUFGMUX選擇想要的時(shí)鐘。推薦PCIe模式中內(nèi)部和外部數(shù)據(jù)位寬相同,此時(shí)[TX/RX]USRCLK和[TX/RX]USRCLK2時(shí)鐘頻率相同。

在Gen1、Gen2和Gen3中,推薦TX buffer旁路,此時(shí)TXOUTCLKSEL必須GTX/GTH收發(fā)器參考時(shí)鐘通過(guò)TXOUTCLK端口后作為TXUSRCLK2的源時(shí)鐘。為了最小化TX lane和lane之間偏移,所有l(wèi)ane的TXUSRCLK和TXUSRCLK2必須來(lái)源相同的時(shí)鐘源。

在Gen1、Gen2和Gen3中,推薦使用RX buffer。當(dāng)RX buffer應(yīng)用在同步時(shí)鐘應(yīng)用中,GTX/GTH收發(fā)器參考時(shí)鐘為RXUSRCLK和RXUSRCLK2的源時(shí)鐘。圖3顯示了PCIe同步時(shí)鐘應(yīng)用架構(gòu)。

圖3、PCIe同步時(shí)鐘架構(gòu)舉例

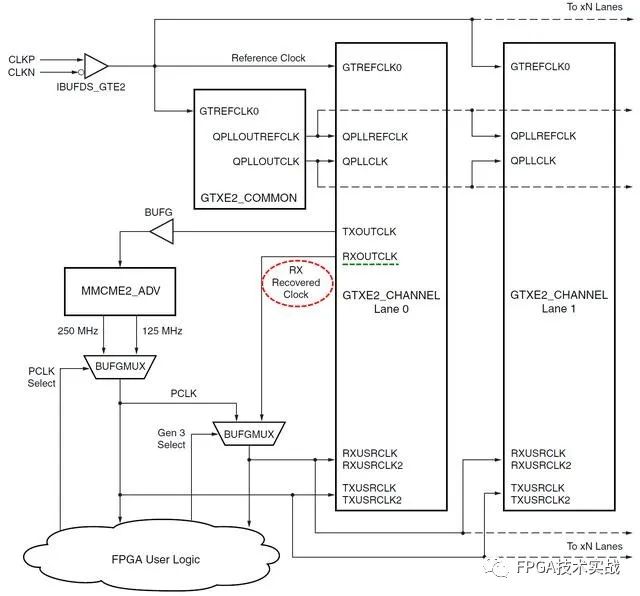

當(dāng)RX buffer用在異步時(shí)鐘應(yīng)用中,RX恢復(fù)時(shí)鐘來(lái)自主Lane0,作為RXUSRCLK和RXUSRCLK2時(shí)鐘源。圖4顯示了PCIe異步時(shí)鐘架構(gòu),圖中如果使用BUFGMUX原句,則BUFG可以插入PCLK路徑中用于平衡路徑時(shí)序。

圖4、PCIe異步時(shí)鐘架構(gòu)舉例

2.XAUI時(shí)鐘設(shè)計(jì)

2.1 參考輸入時(shí)鐘

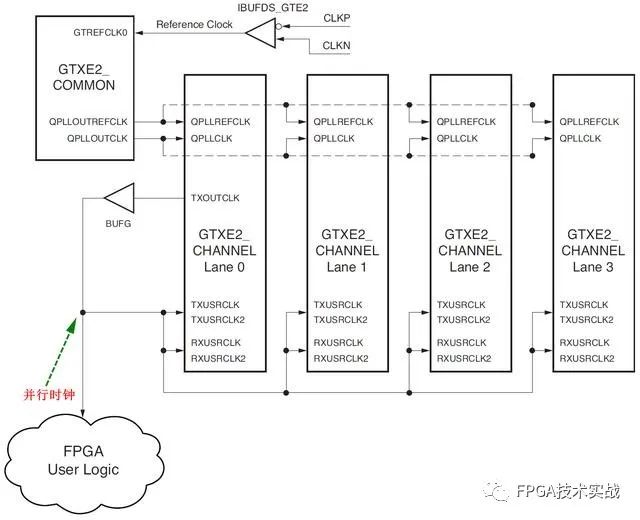

對(duì)于XAUI應(yīng)用,使用單一156.25MHz參考時(shí)鐘。如圖5所示,參考輸入時(shí)鐘通過(guò)IBUFDS_GTE2驅(qū)動(dòng)GTXE2_COMMON。

圖4、XAUI時(shí)鐘架構(gòu)舉例

圖5中QPLL推薦的時(shí)鐘配置如圖6所示。

圖6、QPLL推薦的時(shí)鐘配置

2.2 并行時(shí)鐘

在XAUI操作模式中,GTX/GTH收發(fā)器內(nèi)部數(shù)據(jù)位寬和FPGA接口位寬為2字節(jié)位寬,此時(shí),[TX/RX]USRCLK和[TX/RX]USRCLK2頻率相同,即都為156.25MHz。

對(duì)于XAUI應(yīng)用,推薦TX buffer旁路,此時(shí)TXOUTCLKSEL設(shè)置為3'b011,使用GTX/GTH收發(fā)器參考時(shí)鐘作為TXUSRCLK和TXUSRCLK2時(shí)鐘源。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615467 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3660瀏覽量

107590 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1887瀏覽量

132968

發(fā)布評(píng)論請(qǐng)先 登錄

gtx是光纖嗎

AD9253對(duì)時(shí)鐘抖動(dòng)的要求怎么樣,應(yīng)該選擇怎樣的時(shí)鐘架構(gòu)?

光纖收發(fā)器與IO-Link收發(fā)器的區(qū)別

無(wú)線收發(fā)器工作原理,無(wú)線收發(fā)器怎么使用

高速接口7系列收發(fā)器GTP介紹

影響光纖收發(fā)器性能的三大因素

ATC600無(wú)線測(cè)溫收發(fā)器搭配使用,實(shí)現(xiàn)配電室內(nèi)電氣設(shè)備溫度的實(shí)時(shí)監(jiān)測(cè),支持RS485通訊端口

射頻收發(fā)器就是基帶嗎

光纖收發(fā)器怎么判斷好壞

光纖收發(fā)器pwr是什么意思

光纖收發(fā)器怎么判斷好壞

光纖收發(fā)器AB能調(diào)換嗎

光纖收發(fā)器的作用、使用方法及應(yīng)用

光纖收發(fā)器怎么區(qū)分發(fā)射端和接收端

DS92CK16 3V BLVDS 1至6時(shí)鐘緩沖器/總線收發(fā)器數(shù)據(jù)表

GTX/GTH收發(fā)器時(shí)鐘架構(gòu)應(yīng)用

GTX/GTH收發(fā)器時(shí)鐘架構(gòu)應(yīng)用

評(píng)論