隨著半導體設計團隊競相利用“超越摩爾”,新的架構選擇和挑戰層出不窮。以超大規模硬件為例,其中一系列工作負載——數據庫分析、人工智能、微服務、視頻編碼和高復雜性計算算法——需要一系列處理器解決方案。性能、功耗和成本仍然至關重要,但現在架構師自己交付。沒有一種“最好”的架構;處理器必須設計為最好地服務于特定類別的工作負載和價格/性能配置文件。

多核架構挑戰

AWS Graviton2 有 64 個 Arm Neoverse N1 內核,它們平鋪在單個芯片上的連貫網狀網絡中。其他設計已經擴展到多芯片,芯片之間具有緩存一致的連接。多芯片實現為進一步增長和降低不太先進工藝成本的潛力開辟了空間。雖然這些新架構選項擴展了可能性,但它們也帶來了新的設計挑戰。在眾多選擇中,哪些架構真正能夠以合適的價格為合適的工作負載提供更高的吞吐量?

這里的一個問題是,應如何針對目標類應用程序的物理內存對相干網狀網絡中的分布式系統緩存進行分區。優化這些選擇,甚至優化哪些 CPU 內核最能滿足需求,都需要以周期級精度運行實際工作負載。高級模型根本不足以達到此目的。

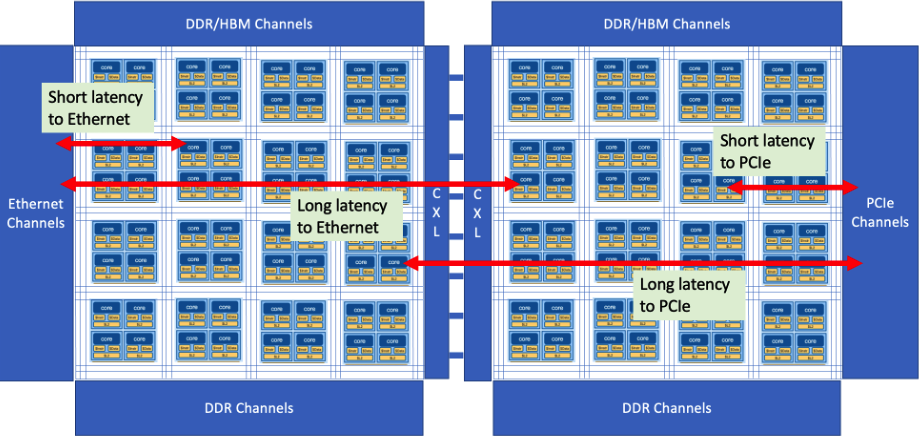

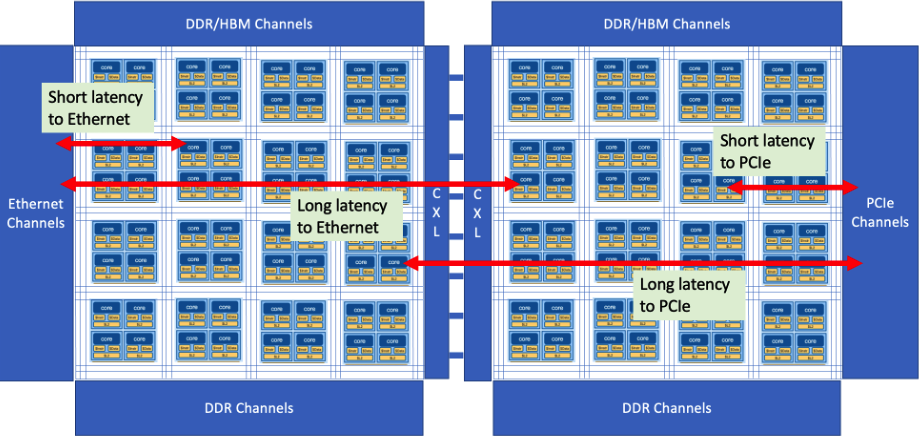

圖:多芯片實現中不同的 I/O 延遲。(來源:Cadence)

連貫網格中的處理器陣列之間的通信延遲在單個裸片內將相對一致,但在多裸片實現中裸片之間的延遲可能會有很大差異(見圖)。因此,設計發展出多種架構,可在未來使用——全連接網格、集線器和輻條內存系統或其他 2D 和 3D 結構,其中一個小芯片提供大系統緩存和主內存訪問。此外,堆棧中的其他小芯片相互通信,并通過集線器與主存儲器通信。

有效探索所有這些選項在很大程度上取決于針對實際工作負載準確建模性能。建模和分析只能在 RTL 域中使用仿真和原型進行探索。

SystemReady 合規性

服務器架構師面臨的另一種問題是操作系統兼容性。您可以直接在大多數筆記本電腦上啟動任何 Linux 發行版、虛擬機管理程序或 Windows。要在基于 Arm 的服務器上啟動,此責任由服務器制造商和 Arm 分擔。

Arm 開發了一個名為 SystemReady 的合規套件,以標準化一組最低要求,以解決這個問題和其他合規問題。PCIe 合規性是一個特別重要的組件,因為它直接為許多服務器接口協議提供或作為主要 I/O 的基礎,以實現快速存儲、快速網絡和芯片外連貫接口。這里特別重要的是通過 PCIe 進行遠程服務器引導。Arm 將此合規套件作為在 UEFI (BIOS) 層上運行的軟件提供。Cadence 與 Arm 合作了幾年,旨在將測試縮減為具有 PCIe 流量生成庫的最小裸機測試套件,該庫的仿真速度比 UEFI 測試套件更快,可以快速調整硬件調試。

服務器開發人員面臨的另一個挑戰是 PCIe 使用強排序的內存模型。Arm 支持標準允許的松散排序的內存模型。但只有強排序才能保證沒有死鎖。在松散訂購下,硬件/固件開發人員必須提供該保證。不幸的是,這無法通過合規性檢查。集成商必須再次在仿真器或原型系統上通過廣泛的用例測試證明設計是死鎖安全的。

使用 Cadence System 驗證 IP 的方法使工程師能夠在半天內啟動并運行系統級測試套件,該套件可以根據 SystemReady 要求驗證 PCIe 集成。此方法還可用于演示從連接到 PCIe 的閃存設備模型引導 SUSE Linux 和 Windows,這引起了高級服務器社區的極大興趣。

不僅適用于服務器

Arm Neoverse 平臺不僅是為高端服務器設計的。該家族已經開始進入其他云應用程序和通信基礎設施,一直到邊緣。在其中一些應用程序中,多核架構已經很重要。在大多數此類應用程序(例如汽車)中,對一系列開放和商業操作系統的開箱即用支持是必不可少的。

我相信用于自動生成系統級內容和驗證系統級目標合規性的工具將在許多市場中具有廣泛的適用性。EDA 行業需要超越傳統的單接口單協議驗證 IP (VIP) 范圍,走向多接口多協議系統級 VIP 的新時代。

-

處理器

+關注

關注

68文章

19824瀏覽量

233709 -

ARM

+關注

關注

134文章

9321瀏覽量

375375 -

服務器

+關注

關注

13文章

9717瀏覽量

87364 -

HPC

+關注

關注

0文章

333瀏覽量

24218

發布評論請先 登錄

HPM5E31IGN單核 32 位 RISC-V 處理器

端側 AI 音頻處理器:集成音頻處理與 AI 計算能力的創新芯片

康佳特推出高性能COM-HPC模塊conga-HPC/cBLS

HPC云計算的技術架構

Andes晶心科技推出AndesCore AX66亂序超純量多核處理器IP

QorIQ?T1042多核處理器

云計算HPC軟件關鍵技術

對稱多處理器和非對稱多處理器的區別

多核RISC-V處理器供應商超睿科技全力支持RT-Thread Smart,共同賦能“大芯片”生態

簡述微處理器的指令集架構

ARM處理器和CISC處理器的區別

微處理器的指令集架構介紹

TMS320C6674多核固定和浮點數字信號處理器數據表

HPC處理器的多核架構挑戰

HPC處理器的多核架構挑戰

評論