微處理器系統(tǒng)中的熱管理是確保工作流程高效執(zhí)行的重要因素。Teledyne e2v 展示了如何通過優(yōu)化處理器的硬件和軟件級(jí)別來降低能耗。Teledyne 數(shù)據(jù)處理解決方案應(yīng)用工程師 Thomas Porcez 在接受 EEWeb 采訪時(shí)強(qiáng)調(diào),與特定應(yīng)用的數(shù)據(jù)表上的值相比,所使用的技術(shù)如何將能耗降低 46%。

在設(shè)計(jì)過程結(jié)束時(shí),工程師經(jīng)常會(huì)遇到能源管理問題,而小尺寸為散熱器或風(fēng)扇留下的空間很小,從而導(dǎo)致性能下降。

通過對(duì)整體系統(tǒng)行為的深入分析,可以定義最佳方法來克服維持有限功率預(yù)算和節(jié)省空間措施的潛在挑戰(zhàn)。這可以通過查看處理器 CPU 負(fù)載數(shù)據(jù)、核心頻率和結(jié)溫來完成。Teledyne e2v 能夠提供一種優(yōu)化處理器的方法,同時(shí)節(jié)省能源并最大限度地減少熱量產(chǎn)生。

靜態(tài)和動(dòng)態(tài)功耗

高處理頻率對(duì)整個(gè)計(jì)算機(jī)系統(tǒng)的能量消耗施加了嚴(yán)格的限制。因此,應(yīng)始終將每個(gè)設(shè)備的能耗降至最低。功率計(jì)算不僅決定了電源的大小,還決定了最大的運(yùn)行可靠性。

處理器的能耗通常分為靜態(tài)能耗和動(dòng)態(tài)能耗。靜態(tài)功耗對(duì)應(yīng)于流經(jīng)器件的漏電流,并隨溫度線性變化。邏輯門的總漏電流包括兩個(gè)主要部分:亞閾值和門漏電流。亞閾值漏電流在 CMOS 數(shù)字電路中很顯著,并且隨著閾值電壓的降低呈指數(shù)增長(zhǎng)。

“靜態(tài)能量消耗的有趣之處在于它不能通過路徑重復(fù);您可以選擇降低能耗的途徑,”Porchez 說。

另一端的動(dòng)態(tài)功耗或多或少與結(jié)溫?zé)o關(guān),但取決于 CPU 負(fù)載、CPU 的平臺(tái)和頻率以及使用的外圍設(shè)備。這意味著動(dòng)態(tài)功耗取決于應(yīng)用。

動(dòng)態(tài)功耗是通過考慮兩個(gè)因素的總和來計(jì)算的:開關(guān)功率和短路功率。當(dāng)對(duì)內(nèi)部電容和網(wǎng)絡(luò)電容進(jìn)行充電或放電時(shí),會(huì)消耗開關(guān)功率。短路功率是柵極切換狀態(tài)時(shí)電源電壓和地之間的瞬時(shí)短路連接所消耗的功率。

Teledyne 解決方案

實(shí)際演示使用兩臺(tái)由 Teledyne e2v 合作伙伴設(shè)計(jì)的單板計(jì)算機(jī)進(jìn)行。每臺(tái)單板機(jī)上都放置了一個(gè)四核架構(gòu)的 T1042 處理器,運(yùn)行頻率最高可達(dá) 1.5 GHz。

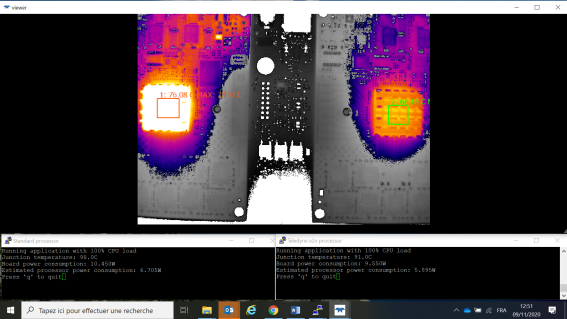

一個(gè)處理器運(yùn)行提供 100% CPU 負(fù)載的應(yīng)用程序。另一個(gè)是 Teledyne 優(yōu)化的處理器,運(yùn)行相同的應(yīng)用程序并提供 50% 的 CPU 負(fù)載。紅外熱像儀同時(shí)分析這兩個(gè)過程。攝像機(jī)圖像顯示在屏幕上。情況如圖 1 所示。

圖 2:降低熱負(fù)荷的演示。左側(cè)帶有標(biāo)準(zhǔn)處理器的板子;右側(cè)是 Teledyne 的優(yōu)化處理器。

“看看圖 2 中的左側(cè)處理器,我們的散熱器溫度約為 71?C,右側(cè)處理器的溫度約為 59?C,相差約 12?C,”Porchez 說。“在端子上,我們看到兩種工藝在結(jié)溫方面仍然存在巨大差異。

“如果我們?cè)敿?xì)查看這里有趣的能源消耗過程,我們會(huì)發(fā)現(xiàn)這兩個(gè)過程之間的差異在 1.5 和 2 W 之間,這是一個(gè)巨大的差異,”他補(bǔ)充道。

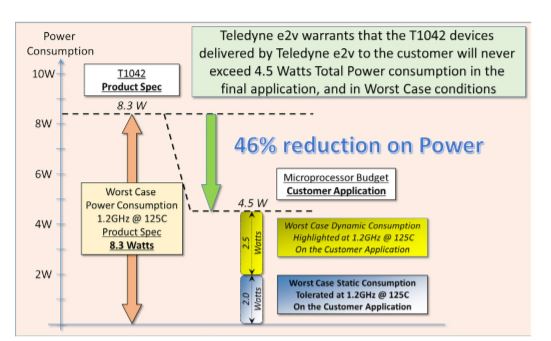

Teledyne e2v 指出,該案例研究可以使 T1042 的功耗降低 46%,這與閱讀 T1042 規(guī)范所期望的結(jié)果相比。

圖 3:總功耗降低

“在與客戶的深入討論中,我們得出結(jié)論,他們的應(yīng)用不需要處理器的最大功能,”Porchez 說。“客戶實(shí)際上擔(dān)心數(shù)據(jù)表中的功率數(shù)據(jù)(在高計(jì)算場(chǎng)景中列出的值)。因此,我們幫助他們縮小了實(shí)際功率估計(jì)的范圍。在此之后,我們能夠?qū)⑵滢D(zhuǎn)化為靜態(tài)功耗限制,并同意交付符合此要求的部件。”

功耗是集成電路面臨的主要挑戰(zhàn)之一。動(dòng)態(tài)功率在 CMOS 電路中占主導(dǎo)地位。動(dòng)態(tài)耗散是由于電流短路和負(fù)載容量充電和放電引起的開關(guān)活動(dòng)的結(jié)果。

更低的功耗(除了更高的帶寬)將是下一代處理器的主要因素。更高速度的全球趨勢(shì)需要新的解決方案來優(yōu)化能源管理。一種旨在降低動(dòng)態(tài)功耗的技術(shù)涉及動(dòng)態(tài)調(diào)整 CPU 中的電壓和頻率。此操作稱為動(dòng)態(tài)電壓和頻率縮放 (DVFS)。它受益于 CPU 具有離散的頻率和電壓設(shè)置這一事實(shí)。

Porchez 強(qiáng)調(diào),這種方法為設(shè)計(jì)人員提供了一個(gè)機(jī)會(huì),可以在他們最初認(rèn)為由于功率限制而無法實(shí)現(xiàn)的應(yīng)用中安裝更大的處理器。這使他們能夠在系統(tǒng)中獲得更大的計(jì)算能力余量,以適應(yīng)未來的用例演變。“對(duì)于 Teledyne e2v 來說,這是一個(gè)額外的技術(shù)差異化因素,與此同時(shí),我們已經(jīng)知道,這會(huì)提高客戶的親密度,”他說。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19863瀏覽量

234369 -

微處理器

+關(guān)注

關(guān)注

11文章

2378瀏覽量

84046

發(fā)布評(píng)論請(qǐng)先 登錄

EV10AS940單芯片通道模數(shù)轉(zhuǎn)換器(ADC)

恩智浦i.MX 94應(yīng)用處理器如何變革工業(yè)和汽車連接

QorIQ?T1042多核處理器

Teledyne 為 Photonics West 帶來其最具創(chuàng)新性的成像解決方案

Teledyne e2v發(fā)布LX2160-Space工程樣片

官宣!OpenWrt正式支持賽昉科技JH-7110 RISC-V應(yīng)用處理器

走進(jìn)北大 | 算能RISC-V通用處理器設(shè)計(jì)成功開課

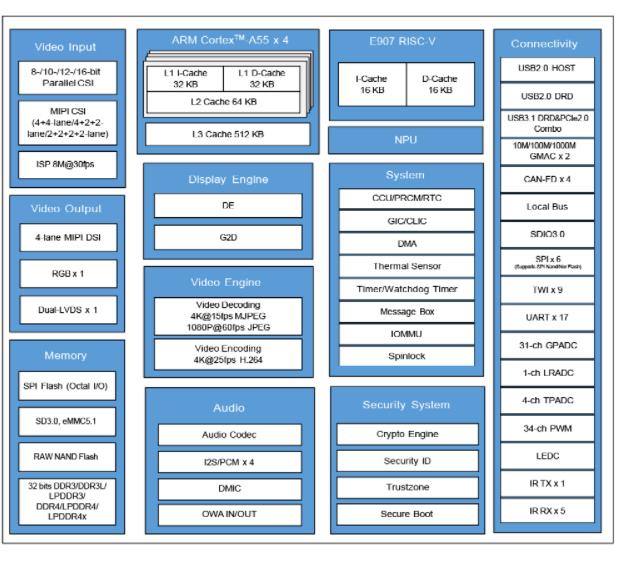

全志T536系列處理器特性概述 集成RISC-V E907協(xié)處理器

RK3566高性能低功耗四核應(yīng)用處理器數(shù)據(jù)手冊(cè)

0.5mm層疊封裝應(yīng)用處理器的PCB組裝指南,第II部分

DRA71x信息娛樂應(yīng)用處理器數(shù)據(jù)表

DRA78x信息娛樂應(yīng)用處理器數(shù)據(jù)表

OMAP5912應(yīng)用處理器數(shù)據(jù)表

OMAP3515和OMAP3503應(yīng)用處理器數(shù)據(jù)表

OMAPL137-HT低功耗應(yīng)用處理器數(shù)據(jù)表

Teledyne e2v改進(jìn)了商用處理器的熱管理

Teledyne e2v改進(jìn)了商用處理器的熱管理

評(píng)論