這就是 BeagleBone Black 的設計師所做的。他們必須將成本保持在極低的水平,而仿真揭示了他們在生產功能板的同時切入的角落。

每個工程師都必須設計滿足預算限制和質量要求的電路和系統。對于消費者和制造商/愛好者的產品設計,每一分錢都很重要。當一塊電路板將由數百萬生產時,一個額外的部件——甚至是一個電阻器——可以產生影響。如果你的產品不能滿足市場承受的售價,游戲就結束了。

這就是 BeagleBone、Adruino、Raspberry Pi 和其他面向業余愛好者和創客市場的微控制器板等低成本產品的設計者所面臨的困境。即使沒有高端仿真工具,設計人員是如何降低成本并讓電路板工作的?為了找出答案,Mentor Graphics 的 Todd Westerhoff 使用他公司的信號完整性軟件來分析 BeagleBone Black 板的設計。

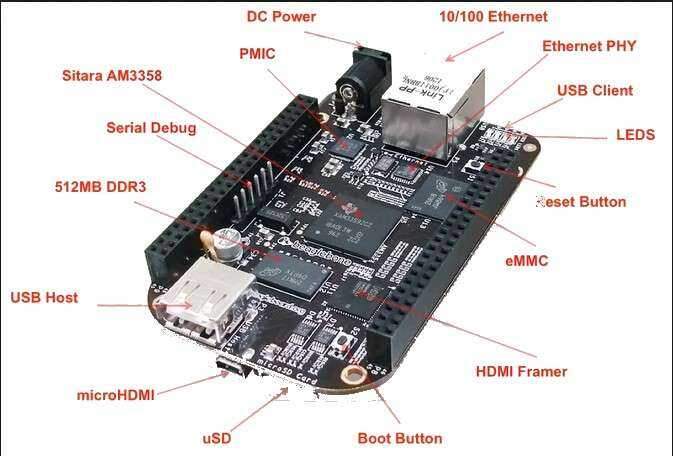

BeagleBone Black 的設計師違反了典型的設計規則,但它的效果很好,價格也很低。(圖片:導師圖形)

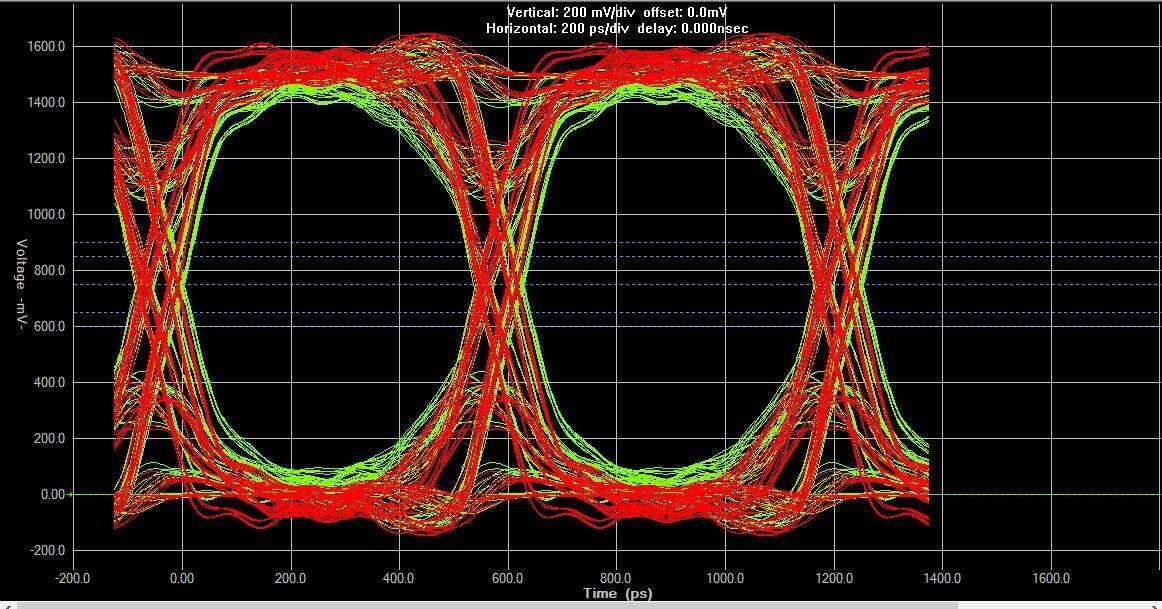

BeagleBone Black 于 2012 年設計,當時還沒有這樣的高端分析工具,BeagleBone Black 的設計師不得不依靠他們的工程技能來設計一些巧妙的技巧。Westerhoff 的分析表明,為了滿足比賽成本限制,Black 的設計師打破了許多常見的設計規則。例如,他們沒有在 DDR3 內存的傳輸線上使用終端電阻。分析還顯示了 Black 的設計人員如何找到合適的驅動電流 (7 mA) 以用最少的電流獲得最大的眼圖張開。

這兩種顏色顯示了不同數量的驅動電流(7 mA 和 8 mA),但眼圖張開幾乎相同,并且有足夠的余量,那么當您一無所獲時,為什么還要費心使用更多電流呢?

由于違反了另一條設計規則,布萊克的設計師劃分了電源平面。這是大多數信號完整性和 EMI 工程師告訴你不要做的事情。此外,Black 的 PCB 具有較厚的內核,這會在電源層和接地層之間留出過多的空間,從而減少可能導致 EMI 的耦合。那么為什么有一個厚的核心呢?它使電路板增加了剛度。最重要的是,信號線在 PCB 層之間移動。這是降低信號完整性和增加 EMI 的另一種方法。然而,黑色的效果足以滿足其預期用途。

Westerhoff 的分析證明,設計規則有時只是指導方針。在某些設計中,您可以打破其中一些常見規則以降低制造成本,而信號衰減很少或沒有,并且對功能沒有不利影響。這并不是說您應該在設計時偷工減料,但有時您可以不遵循所有最佳實踐而僥幸——至少在創客世界中是這樣。

審核編輯:郭婷

-

微控制器

+關注

關注

48文章

7675瀏覽量

152320 -

電阻器

+關注

關注

21文章

3806瀏覽量

62448 -

電路板

+關注

關注

140文章

5009瀏覽量

99264

發布評論請先 登錄

相關推薦

SK海力士如何在eSSD領域應用虛擬化技術

工作管理實戰指南:利用Jira、Confluence等Atlassian工具打破信息孤島,增強團隊協作【含免費指南】

打破網絡邊界:P2Link助力實現高效遠程訪問與內網穿透

網關的設置規則

CMOS晶體管的尺寸規則

AD9元器件間距規則如何設置

規則音頻是一種連續變化的什么信號

ESP32 WIFI SOFTAP模式可以有多個STA連接到它并讓STA相互通信嗎?

高速pcb布線規則有哪些

Synopsys推出一款低功耗靜態規則檢查工具—VCLP

Altium Designer電氣規則設置后無報錯原因解析

打破設計規則并擺脫它

打破設計規則并擺脫它

評論