課程中運用QuarusⅡ工具講解可編程器件PLD的設計流程,QuarusⅡ工具是Altera公司的產品。同時課程說明了針對Xilinx公司的ISE工具的PLD設計流程也是相似的。

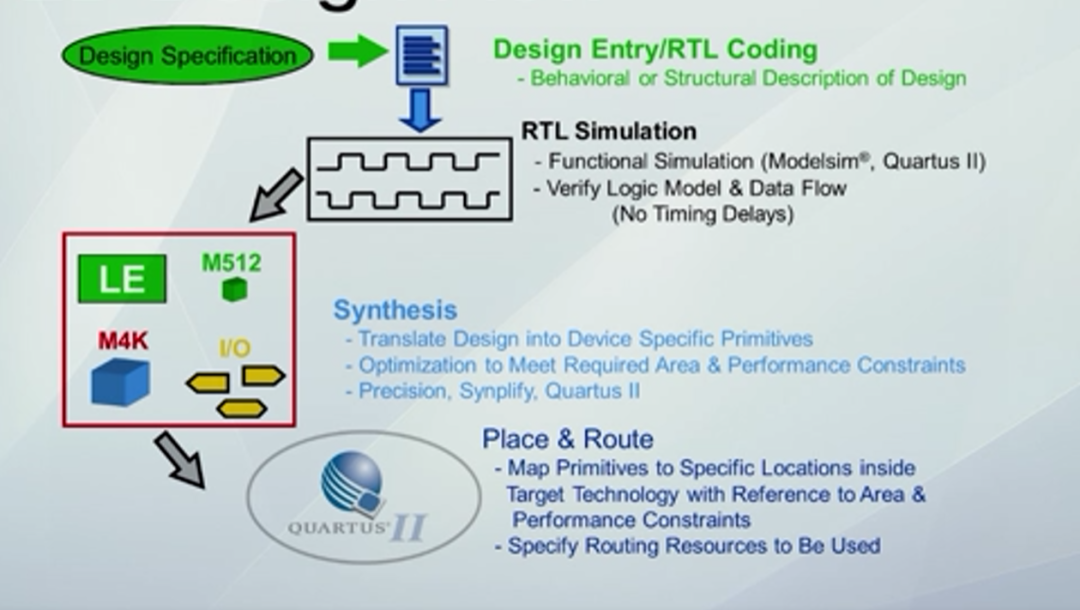

PLD的設計流程與ASIC(專用集成電路)的設計流程類似,具體設計流程如下:

(1)明確設計需求(Design Entry)。根據設計需求,在RTL的結構層次(運用Verilog代碼設計芯片的一種方式)完成電路設計(RTL Coding),完成初始Verilog代碼。

(2)RTL級的電路仿真(RTL Simulation)。進行仿真的工具既可以運用Altera公司的QuarusⅡ內嵌仿真工具,也可以運用Modelsim仿真工具(課程中講解的仿真工具)。驗證代碼是否滿足設計要求,這一階段的驗證沒有時序相關信息,即未考慮器件延時。

(3)邏輯綜合(Synthesis),將RTL級代碼映射成具體的器件實現電路設計,生成對應的門級網單(芯片設計中間階段的電路圖)。

(4)布局和布線(Place&Route),將邏輯綜合過程中使用的元器件替換成Altera公司提供的元器件,并在電路內布線,完成電路連接。

PLD的邏輯綜合與布局和布線兩個步驟可以運用Altera公司提供QuarusⅡ工具一步完成,其他公司提供的PLD設計工具也可以一步完成上述兩個步驟。

圖片來源:學堂在線《IC設計與方法》

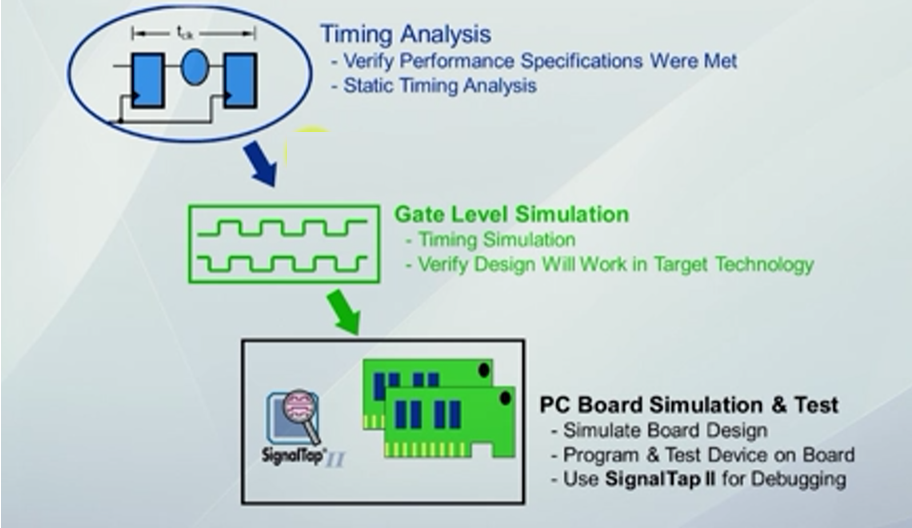

(5)時序分析(Time Analysis),證明電路性能滿足時序要求。

ASIC的設計流程中時序分析步驟在門級仿真步驟后進行,這是因為ASIC設計工具功能限制的原因,門級仿真中的時序只能采用估算的方式得出。

QuarusⅡ工具集成了時序分析功能,時序分析可以方便地進行,所以PLD設計流程的時序分析步驟先于門級仿真步驟。

在芯片設計中,如果時序不能滿足要求,如計數器的要求是100MHz,但設計出的計數器只能滿足10MHz的要求,即使門級仿真的結果正確,也不能滿足設計需求。所以在條件允許的情況下,時序分析步驟先于門級仿真步驟。

(6)門級仿真(Gate Level Simulation),門級仿真結果滿足要求,說明電路滿足設計的功能需求。

(7)電路板仿真和測試(PC Board Simulation&Test)。將經過以上步驟得出的數據流文件下載到可編程芯片中,再將可編程芯片安裝到PC板(個人理解:PCB板,印刷電路板,芯片實現對應功能所需安裝的電路板)中,進行測試。

圖片來源:學堂在線《IC設計與方法》

PLD設計芯片需要進行編譯,與一般編程軟件的編譯目的不同,PLD設計芯片的編譯的目的是將RTL級代碼轉化成物理器件上可以實現的電路。

具體的編譯過程有以下幾個方面:

(1)前端設計的邏輯綜合。

(2)后端設計的布局布線。

(3)后端設計產生的相關輸出。相關輸出包括:用于時序分析的門級網單、用于仿真的門級網單、對器件編程的配置文件。對器件編程的配置文件可以將沒有功能的可編程器件改變為可以實現設計需求的專用器件。

審核編輯 :李倩

-

電路設計

+關注

關注

6701文章

2531瀏覽量

213744 -

PLD

+關注

關注

6文章

230瀏覽量

60068 -

Quarus

+關注

關注

0文章

4瀏覽量

6479

原文標題:芯片設計相關介紹(27)——PLD設計流程

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

NX CAD軟件:數字化工作流程解決方案(CAD工作流程)

什么是PLD的定義和應用 PLD與FPGA的區別和聯系

如何快速入門PLD電路設計

PLD設計流程的詳細步驟

PLD的優勢與劣勢分析

PLD在嵌入式系統中的應用實例

如何選擇合適的PLD型號

PLD芯片的工作原理解析

MOSFET晶體管的工藝制造流程

數字設計ic芯片流程

接單流程設計探索

PLD的設計流程

PLD的設計流程

評論