FPGA畢竟不是ASIC,對(duì)時(shí)序收斂的要求更加嚴(yán)格,本文主要介紹本人在工程中學(xué)習(xí)到的各種時(shí)序約束技巧。

首先強(qiáng)烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒有之一。它提倡要在設(shè)計(jì)的早期階段就要排除問題,越到后期時(shí)序的改善就越困難。其中HLS層次對(duì)性能的影響是最大的。

本文將從代碼風(fēng)格,時(shí)序修正,工程設(shè)置等幾個(gè)方面介紹本人的實(shí)踐經(jīng)驗(yàn),希望讓各位初學(xué)者快速提高,也希望FPGAer能給出寶貴建議。

1. 代碼風(fēng)格

推薦使用Xilinx language templates的代碼塊,這里的代碼能夠綜合出正確且結(jié)構(gòu)簡(jiǎn)潔的電路,包括移位寄存器,乘法,復(fù)數(shù)乘法,F(xiàn)IR濾波器等,凡是涉及到的模塊盡量使用官方寫法。

合理的設(shè)計(jì)代碼框架。IO相關(guān)的代碼、時(shí)鐘管理單元盡量放在頂層,后者有助于以共享資源從而提高性能降低功耗。模塊的輸出最好是使用寄存器輸出,有助于降低路徑延時(shí)幫助時(shí)序收斂。

復(fù)位也是非常重要的問題。和ASIC不同,Xilinx FPGA的寄存器是高電平復(fù)位,支持異步復(fù)位和同步復(fù)位,但是DSP和BRAM內(nèi)部的寄存器不支持異步復(fù)位。因此,官方更推薦設(shè)計(jì)采用高電平同步復(fù)位,可以降低資源的使用和功耗,有助于時(shí)序收斂。由于FPGA的初始狀態(tài)是確定的(可以在定義說明中指定),為了更快地時(shí)序收斂,官方文檔認(rèn)為,能不用復(fù)位是最好的,尤其數(shù)據(jù)路徑和移位寄存器的設(shè)計(jì)中。不過使用同步復(fù)位仍需要注意控制集不能太多的問題。關(guān)于這方面的內(nèi)容,UG949第三章Control Signals and Control Sets給了詳細(xì)的說明。

數(shù)學(xué)運(yùn)算使用DSP單元速度會(huì)更快一些,根據(jù)DSP的結(jié)構(gòu)重組數(shù)學(xué)運(yùn)算,充分利用FPGA的DSP、BRAM資源。并且能做到對(duì)代碼映射的硬件資源心里有數(shù)。

如果并不需要優(yōu)先級(jí),盡量將If語(yǔ)句轉(zhuǎn)化為case語(yǔ)句。

盡量不要使用Don't Touch這類語(yǔ)句。如今Vivado綜合工具已經(jīng)很完善了,除非代碼有問題或者手動(dòng)復(fù)制寄存器,否則一般不會(huì)發(fā)生電路被綜合掉的現(xiàn)象。使用這些語(yǔ)句會(huì)覆蓋Vivado綜合設(shè)置,導(dǎo)致電路沒有得到充分的優(yōu)化,給時(shí)序收斂造成困難。

2. 時(shí)序修正

嚴(yán)格遵守Vivado開發(fā)流程,在第一次跑綜合時(shí)最好是在沒有任何物理約束的情況下,Vivado在越少物理約束的情況下綜合出來的效果越好。查看每個(gè)階段的時(shí)序報(bào)告,將每一階段的時(shí)序違例控制在300ps以內(nèi),盡早消除問題。以前本人RTL Analysis階段過了之后選擇運(yùn)行Implementation跳過Synthesis報(bào)告,這是不可取的行為。有時(shí)候會(huì)發(fā)現(xiàn)Synthesis有時(shí)序問題而在Implementation階段反而沒問題,這是因?yàn)閂ivado在Implementation階段對(duì)時(shí)序不滿足的地方傾斜了更多的資源保證時(shí)序收斂。但是忽略Synthesis的時(shí)序問題會(huì)在后期頂層模塊集成占用大資源時(shí)爆發(fā)出來。

下面介紹主要面對(duì)的兩個(gè)時(shí)序問題的處理技巧。

1)setup time 建立時(shí)間問題

建立時(shí)間是工程設(shè)計(jì)中最常遇到的問題了。一般說來,導(dǎo)致建立時(shí)間違例主要有兩個(gè)原因:邏輯級(jí)數(shù)太大或者扇出太大。

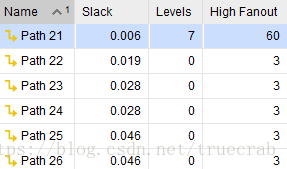

打開Report Timing Summary界面查看路徑延遲信息,如下圖所示。

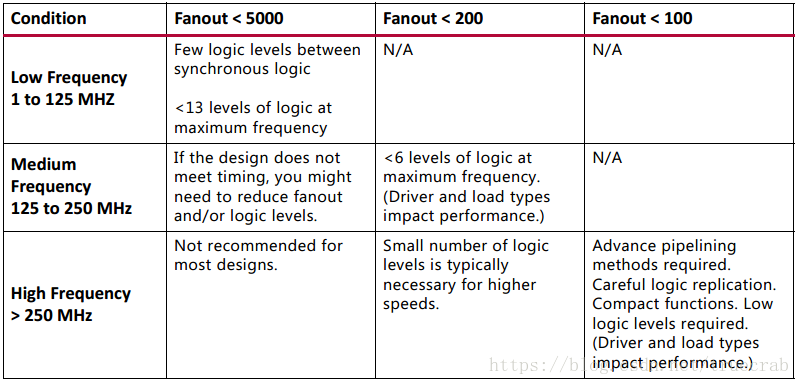

Levels指的是邏輯級(jí)數(shù)logic level,一個(gè)logic level的延遲對(duì)應(yīng)的是一個(gè)LUT和一個(gè)Net的延遲,對(duì)于不同的器件,不同頻率的設(shè)計(jì)能容納的logic level是不同的。假設(shè)7系列的-2速度等級(jí)250MHz的設(shè)計(jì),電路設(shè)計(jì)的大部分levels最好不要超過8,否則會(huì)造成時(shí)序收斂困難。

Logic level太大的處理方法就是重定時(shí)(Retiming)了,典型的重定時(shí)方法就是流水線,將過于冗長(zhǎng)的組合邏輯增加寄存器進(jìn)行打拍。

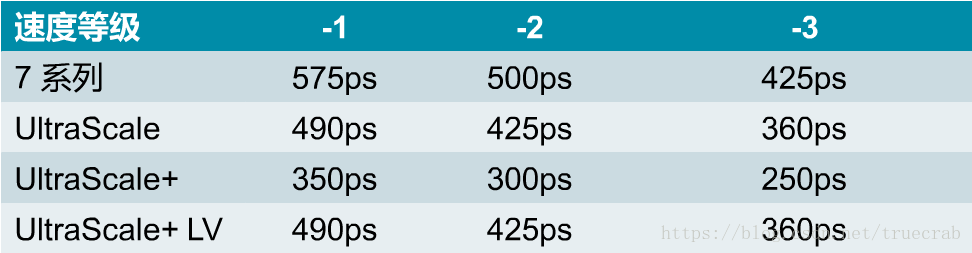

High Fanout指的是扇出,同樣和器件、設(shè)計(jì)頻率等有關(guān),如下圖所示:

降低扇出最好不要在綜合設(shè)置中指定,過低的扇出限制會(huì)造成設(shè)計(jì)堵塞反而不利于時(shí)序收斂,最好的方法是根據(jù)設(shè)計(jì)中時(shí)序最差路徑的扇出進(jìn)行針對(duì)性的優(yōu)化。如果是寄存器的輸出扇出很大,可以使用max_fanout屬性標(biāo)記寄存器聲明,也可以手動(dòng)復(fù)制寄存器,

如果不是關(guān)鍵時(shí)序路徑,而且高扇出網(wǎng)絡(luò)直接連接到觸發(fā)器,對(duì)扇出超過25K的net插入BUFG:

set_property CLOCK_BUFFER_TYPE BUFG [get_nets netName]

當(dāng)然,也可以在后期Implementation的物理優(yōu)化設(shè)置中優(yōu)化扇出。

2)hold time 保持時(shí)間問題

在實(shí)踐中,我發(fā)現(xiàn)保持時(shí)間問題的問題往往是異步處理的問題。

對(duì)于一個(gè)信號(hào)的跨時(shí)鐘域問題,一般使用雙寄存器法(對(duì)于慢采快的結(jié)繩法這里不討論)。為了降低MTBF(Mean Time Between Failures,平均無障礙時(shí)間),這兩個(gè)寄存器最好位于同一個(gè)slice中。可以使用tcl語(yǔ)言指定,如:

set_property ASYNC_REG TRUE [get_cells [list sync0_reg sync1_reg]]

也可以直接在代碼中指定:

(* ASYNC_REG = "TRUE" *) (* keep = "true" *)reg sync0_reg, sysnc1_reg;

也可以參考代碼模板使用XPM模板進(jìn)行處理。

多個(gè)信號(hào)一般是使用FIFO或者握手的方法,這里不再贅述原理。同步CDC處理比較復(fù)雜,本人打算之后另外寫一篇文章詳細(xì)講述。

3. 工程設(shè)置

Vivado綜合實(shí)現(xiàn)本質(zhì)是時(shí)序驅(qū)動(dòng)的,和ISE不同,因此再也沒有ISE那種用隨機(jī)種子綜合實(shí)現(xiàn)滿足時(shí)序收斂的工具。不過Vivado在布局布線方面提供了幾種不同的策略(directive),通過不同策略的組合可以產(chǎn)生上千種不同的布局布線結(jié)果,還可以使用tcl鉤子腳本自定義布局布線過程,足以滿足需求。而且,Vivado可支持同時(shí)運(yùn)行多個(gè)Implementation,這為這種設(shè)計(jì)時(shí)間換取性能的方法提供了工具上的便利。

Implementation里Post-place Phys Opt Design和Post-route Phys Opt Design是沒有使能的。工程后期使能這兩個(gè)配置也能在一定程度上改善時(shí)序收斂。

FPGA工程師的工作不只是將電路功能實(shí)現(xiàn),由于器件和工具不是理想的,所以還需要研究器件特性和工具的局限,尤其是在如今算法結(jié)構(gòu)越來越成熟的背景下,不斷被工具折磨,也許這也是FPGA工程師的悲哀吧。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618790 -

Vivado

+關(guān)注

關(guān)注

19文章

835瀏覽量

68824

原文標(biāo)題:Vivado工程經(jīng)驗(yàn)與時(shí)序收斂技巧

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

VIVADO時(shí)序約束及STA基礎(chǔ)

FPGA的IO口時(shí)序約束分析

FPGA時(shí)序約束之衍生時(shí)鐘約束和時(shí)鐘分組約束

一文詳解Vivado時(shí)序約束

學(xué)習(xí)時(shí)序約束 遇到的問題,求助

時(shí)序約束與時(shí)序分析 ppt教程

時(shí)序約束用戶指南

深入了解時(shí)序約束以及如何利用時(shí)序約束實(shí)現(xiàn)FPGA 設(shè)計(jì)的最優(yōu)結(jié)果

FPGA時(shí)序約束的概念和基本策略

FPGA設(shè)計(jì)之時(shí)序約束

時(shí)序約束怎么用?時(shí)序約束到底是要干嘛?

在工程中學(xué)習(xí)到的各種時(shí)序約束技巧

在工程中學(xué)習(xí)到的各種時(shí)序約束技巧

評(píng)論