之前,和EE的小伙伴交流,談到高速信號。他說:你們SI只要看看那些頻率大于100MHz的信號,什么USB、PCIe就行了,其他的就不用關心了。那些時鐘Buffer出的100M,那些UART,SPI等低速信號我們就看看線長,隨意管控就行了。

查了查,整理一下市面上對高速信號的相關定義:

1.頻率大于100MHz的信號;

2.上升沿(或下降沿)小于100ps的信號;

3.上升時間小于5倍的信號傳輸延時。

想一想:時鐘Buffer出的100M,算不算高速信號?

從理論上來說,這個信號是不是高速信號,就是判斷這個信號是否在傳輸過程中有SI 的問題,需不需要管控?

關于高速信號定義的第一點。頻率大于多少就定性為是否是高速信號,那就是高頻和高速的區別。高頻是否就是高速?

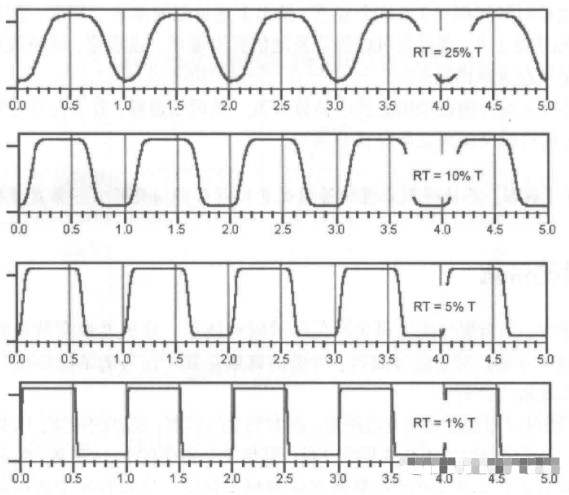

話不多說,直接上圖:

同樣是1GHz的信號,信號的邊沿越陡峭,高頻分量就越多,就需要管控其信號完整性。同樣,信號的邊沿不陡峭,就不需要管控了,所以頻率大于多少的信號,是否是高速信號,要看情況。不能簡單地認為高頻就是高速,不能把高頻和高速混為一談。

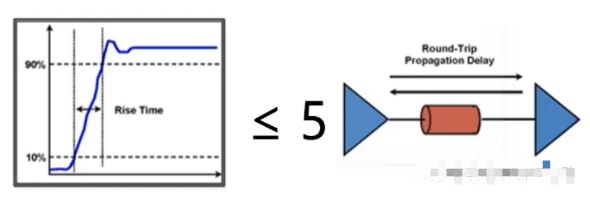

接下來講高速信號定義的兩點,都是關于上升時間有關。實際上,SI 的大多數問題也都是和信號的上升時間(RT)有關。

上升時間:低電平到高電平,電壓幅值從10%~90%的時間。也有一種說法:20%~80%。我們這里選擇10%~90%。

當傳輸線時延大于信號上升邊20%,會有信號完整性問題,振鈴噪聲可能影響電路功能,需要加以管控。反推出,傳輸時延和信號上升時間的關系:

注:5倍只是一個理論預估值,不是絕對值

接下來,我們舉例子來說明一下 :

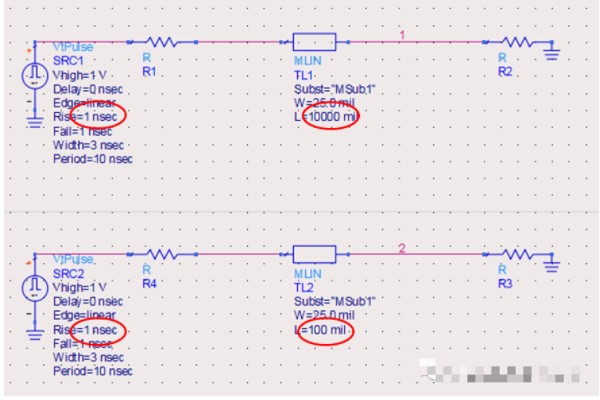

100 M時鐘的線長,方便計算,我們這里取10000 mil。考慮建模搭建的是微帶線,信號傳輸時延取值約為170 ps/in ,時延時間為170 * 10 =1700 ps =1.7 ns。推算出五倍時延為1.7 * 5 =8.5 ns。

微處理的產品,典型的上升邊一般是周期的10%,當然也有的是5%,我們這里取10%,得出100 M時鐘信號的上升邊約為1 ns。

8.5 ns 大于信號上升時間1 ns。也就是說,從理論上來看,需要對信號進行管控。對比傳輸線長為100 mil時候,時延只有17 ps ,不會對信號產生影響,則不需要管控。

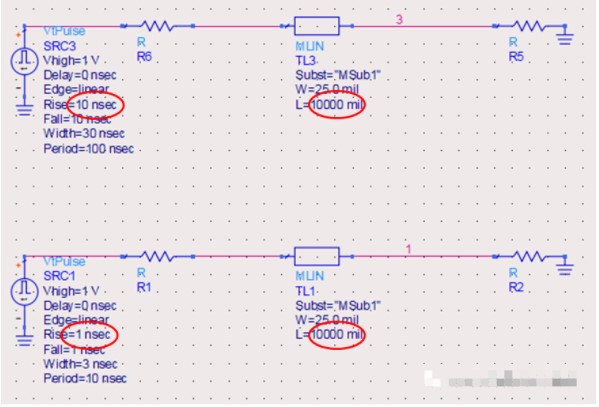

用仿真軟件搭建相關電路:

第一種情況

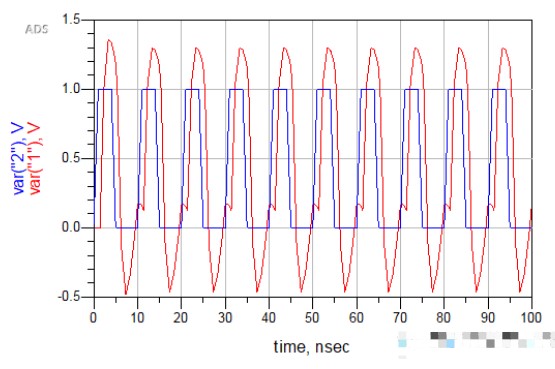

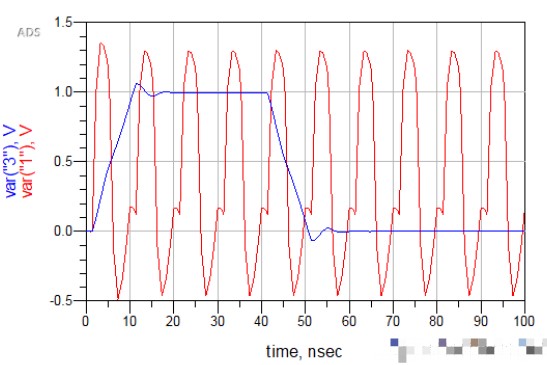

仿真出相應節點的波形:

當信號線長為10000 mil時,振鈴現象很嚴重,阻抗突變帶來很明顯的影響。而信號線長為100 mil時,阻抗突變帶來的變化對信號根本沒有任何影響。

第二種情況

將信號的上升時間調整為10 ns,10 ns大于 8.5 ns,理論來看,阻抗突變對信號的影響有限。來看一看仿真的結果:

隨著上升時間變大,阻抗突變對信號的影響可以忽略。

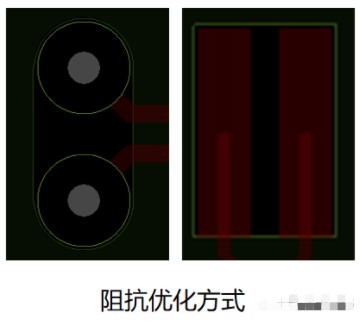

當高速信號需要管控的時候,考慮到阻抗不匹配反射對信號質量的影響,針對本例來看,需要對鏈路中的過孔和SMT連接器進行阻抗優化處理,來減少阻抗突變對信號質量的影響。

優化方式見下圖:

審核編輯:劉清

-

連接器

+關注

關注

99文章

15289瀏覽量

139737 -

時鐘

+關注

關注

11文章

1891瀏覽量

132998 -

smt

+關注

關注

43文章

3026瀏覽量

71649 -

buffer

+關注

關注

2文章

120瀏覽量

30548 -

高速信號

+關注

關注

1文章

243瀏覽量

18019

發布評論請先 登錄

使用adc08200 100M采樣,當有高壓脈沖干擾時,AD輸出出錯怎么解決?

高速AD加上時鐘后,輸入信號會有一個兩倍于時鐘信號的毛刺產生是什么原因

擴頻時鐘技術分享:SSC技術是什么、SSC對測試高速總線信號的影響

時鐘Buffer出的100M算不算高速信號?

時鐘Buffer出的100M算不算高速信號?

評論