可重構(gòu)計(jì)算芯片(Reconfigurable Computing Chip)是基于可重構(gòu)計(jì)算架構(gòu)設(shè)計(jì)的芯片。可重構(gòu)計(jì)算是一種時(shí)空二維編程的并行計(jì)算模式。與之相對(duì),傳統(tǒng)的通用處理器是時(shí)域編程的計(jì)算模式,FPGA是空域編程的計(jì)算模式。可重構(gòu)計(jì)算芯片是集成電路領(lǐng)域的顛覆性技術(shù),具有廣泛適用性。

所謂可重構(gòu)計(jì)算是指在配置信息的控制下,利用系統(tǒng)中的可編程計(jì)算資源,根據(jù)應(yīng)用的需要構(gòu)造出最適配的計(jì)算架構(gòu),達(dá)到或接近專用集成電路的高性能。可重構(gòu)計(jì)算的本質(zhì)是通過多次重新配置可編程計(jì)算資源的功能和互連,使系統(tǒng)兼具高性能、低功耗、易維護(hù)、低成本等多種優(yōu)良特性。

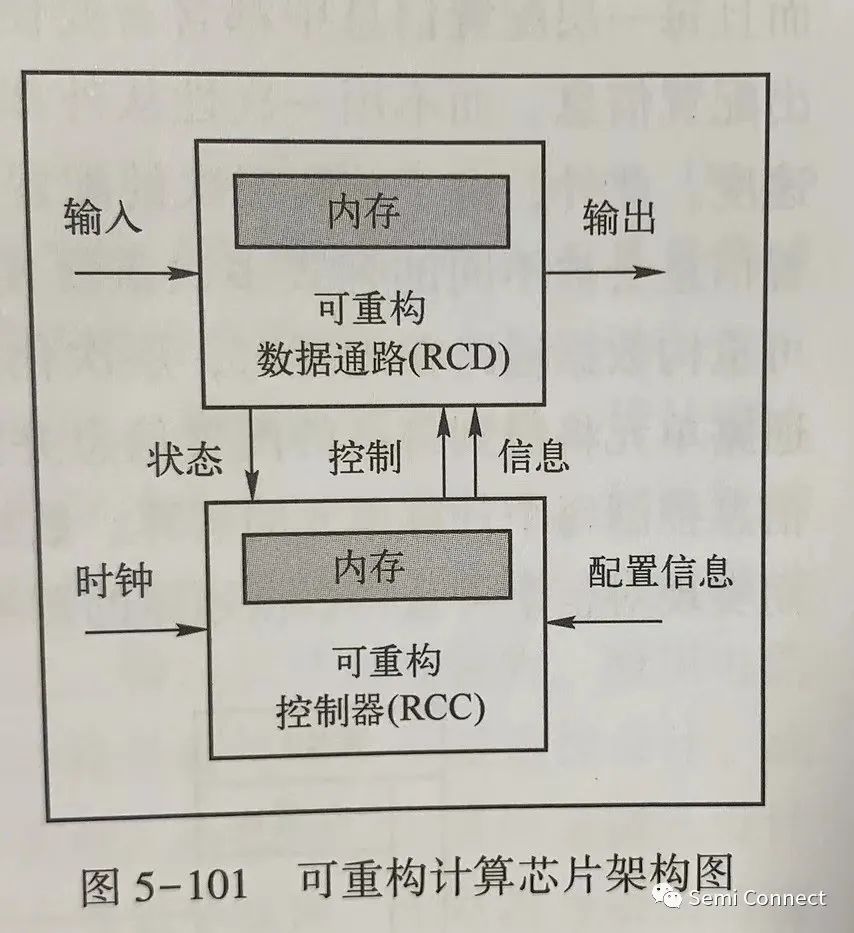

可重構(gòu)計(jì)算芯片硬件架構(gòu)由可重構(gòu)數(shù)據(jù)通路(Reconfigurable Datapath,RCD)和可重構(gòu)控制器(Reconfigurable Controller,RCC)兩部分組成,如圖5-101所示。其中可重構(gòu)數(shù)據(jù)通路負(fù)責(zé)數(shù)據(jù)流的并行處理,可重構(gòu)控制器負(fù)責(zé)配置信息管理和任務(wù)映射調(diào)度。在可重構(gòu)數(shù)據(jù)通路負(fù)責(zé)數(shù)據(jù)流的并行處理,可重構(gòu)控制器負(fù)責(zé)配置信息管理和任務(wù)映射調(diào)度。在可重構(gòu)計(jì)算系統(tǒng)中,數(shù)據(jù)通路可通過調(diào)用或修改配置信息被動(dòng)態(tài)重配,這樣既保留了用定制電路(硬件方法)實(shí)現(xiàn)計(jì)算的性能,又具有用處理器方法(軟件方法)實(shí)現(xiàn)計(jì)算的靈活性。

可重構(gòu)計(jì)算芯片的配置策略可分為靜態(tài)重構(gòu)和動(dòng)態(tài)重構(gòu)。靜態(tài)重構(gòu)只能在可重構(gòu)計(jì)算芯片的數(shù)據(jù)通路進(jìn)行計(jì)算之前對(duì)其進(jìn)行功能重構(gòu)。靜態(tài)重構(gòu)只能在可重構(gòu)計(jì)算芯片的數(shù)據(jù)通路進(jìn)行計(jì)算之前對(duì)其進(jìn)行對(duì)過大而無法對(duì)數(shù)據(jù)通路進(jìn)行功能重構(gòu)。最典型的具有靜態(tài)重構(gòu)特征的可重構(gòu)計(jì)算芯片是FPGA。FPGA的常見工作方式是系統(tǒng)上電時(shí)從片外存儲(chǔ)器中加載配置信息進(jìn)行功能重構(gòu)。FPGA配置信息的規(guī)模一般很大,重構(gòu)過程通常會(huì)持續(xù)幾十至幾百毫秒甚至多大幾秒的時(shí)間。等功能重構(gòu)完成之后,F(xiàn)PGA才能進(jìn)行相應(yīng)的計(jì)算。

在計(jì)算過程中,F(xiàn)PGA的功能無法再被重構(gòu)。如需重構(gòu),一定要首先中斷FPGA當(dāng)前正在進(jìn)行的計(jì)算任務(wù)。因?yàn)槭菃伪忍鼐幊唐骷?xì)粒度可重構(gòu)計(jì)算芯片),所以FPGA的靈活性非常高,在不考慮容量的前提下幾乎可以實(shí)現(xiàn)任何形式的數(shù)字邏輯。這也是FPGA能夠在商業(yè)上獲得極大成功的重要原因之一。然而,細(xì)粒度給FPGA帶來了海量的配置信息,重構(gòu)的時(shí)間代價(jià)和功耗代價(jià)就變得非常大。而典型的動(dòng)態(tài)可重構(gòu)芯片的重構(gòu)時(shí)間一般在幾納秒到幾十納秒的范圍。

由于功能重構(gòu)的時(shí)間代價(jià)相對(duì)較小,可重構(gòu)計(jì)算芯片的數(shù)據(jù)通路在計(jì)算過程中也能夠進(jìn)行功能重構(gòu)的特性被稱為動(dòng)態(tài)重構(gòu)。最典型的具有動(dòng)態(tài)重構(gòu)特性的可重構(gòu)計(jì)算芯片是粗粒度可重構(gòu)陣列(Coarse-Grained Reconfigurable Architecture, CGRA)。CGRA的常見工作方式是:在CGRA完成某個(gè)既定的計(jì)算任務(wù)之后,迅速對(duì)其加載新的配置比特流進(jìn)行功能重構(gòu)。重構(gòu)過程通常僅會(huì)持續(xù)幾個(gè)到幾百個(gè)時(shí)鐘周期。等功能重構(gòu)完成之后,CGRA再繼續(xù)執(zhí)行該新配置的計(jì)算任務(wù)。

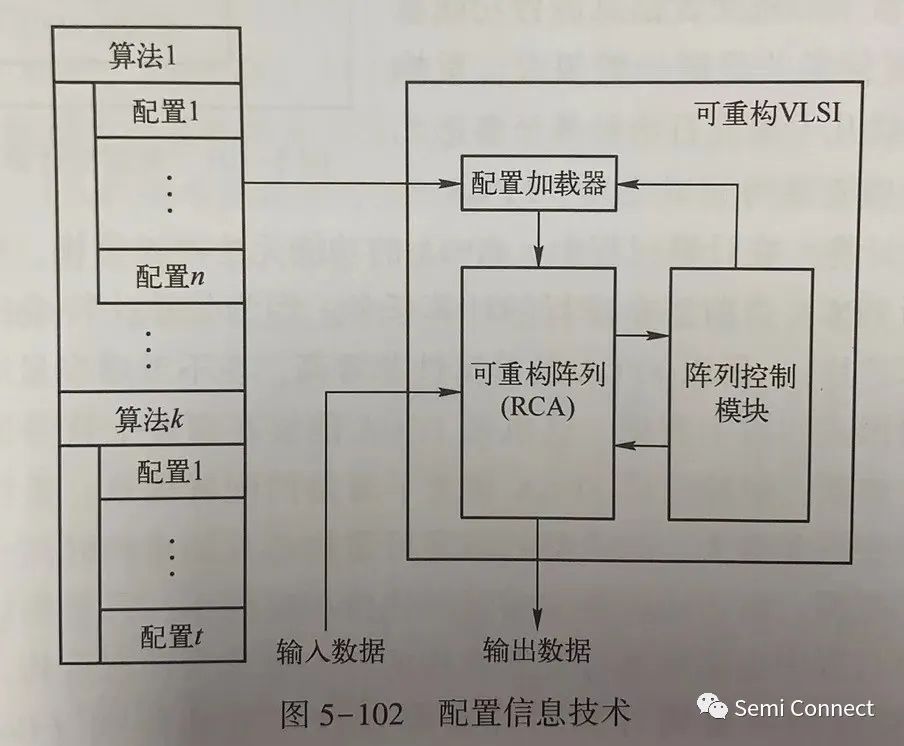

可重構(gòu)計(jì)算芯片區(qū)別于其他電路實(shí)現(xiàn)形式的一大特點(diǎn)就是需要對(duì)數(shù)據(jù)通路進(jìn)行配置,配置完成后它就像ASIC電路一樣以較高的性能實(shí)現(xiàn)指定的功能。如圖5-102所示,可重構(gòu)數(shù)據(jù)通路通過配置加載器從外部加載配置,這部分構(gòu)成了可重構(gòu)數(shù)據(jù)通路的配置部分。縮短可重構(gòu)數(shù)據(jù)通路通過配置加載器從外部加載配置,這部分構(gòu)成了可重構(gòu)數(shù)據(jù)通路的配置部分。縮短可重構(gòu)數(shù)據(jù)通路的配置時(shí)間是十分重要的,這樣可以很快地完成不同配置之間的切換,提高電路的實(shí)時(shí)響應(yīng)能力。

常用的縮短配置時(shí)間的方式有兩種:一是提高數(shù)據(jù)通路的粒度以減少配置信息的總量,配置時(shí)間相應(yīng)減少;二是通過層次化的配置結(jié)構(gòu)減少從數(shù)據(jù)通路外部輸入的配置信息數(shù)量,并且實(shí)現(xiàn)對(duì)配置信息存儲(chǔ)在不同的存儲(chǔ)器中,而且每一層配置信息中都含有要使用的下一層配置信息的列表,這樣逐層地調(diào)出配置信息,而不用一次性從外部將大量配置信息全部輸入,從而提高了配置速度。此外,由于較高層次的配置信息只含有底層配置信息的列表,底層的配置信息會(huì)被不同的列表多次重復(fù)使用,從而達(dá)到了減少配置信息總量的目的。

可重構(gòu)數(shù)據(jù)通路在配置時(shí),層次化的配置結(jié)構(gòu)被一層一層打開,最終每個(gè)數(shù)據(jù)通路單元將得到自己的配置信息并完成配置。數(shù)據(jù)通路控制模塊通過解析配置信息控制每個(gè)計(jì)算單元的運(yùn)算、數(shù)據(jù)的輸入/輸出、配置信息的加載時(shí)間等,從而實(shí)現(xiàn)對(duì)整個(gè)可重構(gòu)數(shù)據(jù)通路的調(diào)度。

近年來,可重構(gòu)計(jì)算技術(shù)已成為集成電路研究的新熱點(diǎn)。可重構(gòu)計(jì)算芯片具備硬件隨軟件變化而變化、軟硬件雙編程的特點(diǎn),突破了傳統(tǒng)的基于硬件進(jìn)行軟件編程的計(jì)算模式,實(shí)現(xiàn)了“電路跟隨算法變,架構(gòu)跟隨應(yīng)用變“的高能效動(dòng)態(tài)可重構(gòu)計(jì)算技術(shù)。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

459文章

52344瀏覽量

438475 -

集成電路

+關(guān)注

關(guān)注

5420文章

12008瀏覽量

367750

原文標(biāo)題:可重構(gòu)計(jì)算芯片

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

工業(yè)4.0的“全能戰(zhàn)士”——如何用一顆芯片重構(gòu)智能工廠的算力版圖?

清微智能官宣:國產(chǎn)可重構(gòu)芯片全球出貨量突破2000萬顆

計(jì)算效率提升3倍,MaPU如何提升儲(chǔ)能產(chǎn)品性能

芯片架構(gòu)設(shè)計(jì)的關(guān)鍵要素

突破傳統(tǒng)桎梏,富唯可重構(gòu)柔性裝配系統(tǒng)引領(lǐng)行業(yè)新變革

HPC云計(jì)算的技術(shù)架構(gòu)

開源芯片系列講座第24期:基于SRAM存算的高效計(jì)算架構(gòu)

基于相變材料的可重構(gòu)超構(gòu)表面用于圖像處理

《算力芯片 高性能 CPUGPUNPU 微架構(gòu)分析》第二篇閱讀心得:芯片拓?fù)鋵W(xué):并行擴(kuò)展與CPU設(shè)計(jì)的巨頭對(duì)決

深入理解 Llama 3 的架構(gòu)設(shè)計(jì)

邊緣計(jì)算架構(gòu)設(shè)計(jì)最佳實(shí)踐

FPGA芯片架構(gòu)和資源有深入的理解,精通Verilog HDL、VHDL

AI芯片的混合精度計(jì)算與靈活可擴(kuò)展

主流芯片架構(gòu)包括哪些類型

自動(dòng)駕駛?cè)笾髁?b class='flag-5'>芯片架構(gòu)分析

基于可重構(gòu)計(jì)算架構(gòu)設(shè)計(jì)的芯片

基于可重構(gòu)計(jì)算架構(gòu)設(shè)計(jì)的芯片

評(píng)論