HDLBits: 在線學(xué)習(xí) SystemVerilog(三)-Problem 10-14

HDLBits 是一組小型電路設(shè)計(jì)習(xí)題集,使用 Verilog/SystemVerilog 硬件描述語(yǔ)言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)~

網(wǎng)址如下:

https://hdlbits.01xz.net/

關(guān)于HDLBits的Verilog實(shí)現(xiàn)可以查看下面專欄:

https://www.zhihu.com/column/c_1131528588117385216

縮略詞索引:

- SV:SystemVerilog

向量

從這個(gè)題目到后面八道題目左右是關(guān)于向量的,所以我們先回顧一下向量。

SystemVerilog有兩種類型的數(shù)組:壓縮數(shù)組和非壓縮數(shù)組。壓縮數(shù)組是連續(xù)存儲(chǔ)的位的集合,通常稱為向量。非壓縮數(shù)組是網(wǎng)絡(luò)或變量的集合。

集合中的每個(gè)網(wǎng)絡(luò)或變量稱為數(shù)組元素。未壓縮數(shù)組的每個(gè)元素的類型、數(shù)據(jù)類型和向量大小都完全相同。每個(gè)未壓縮的數(shù)組元素可以獨(dú)立于其他元素存儲(chǔ);這些元素不需要連續(xù)存儲(chǔ)。軟件工具,如仿真器和綜合編譯器,可以以工具認(rèn)為最佳的任何形式組織未壓縮數(shù)組的存儲(chǔ)。

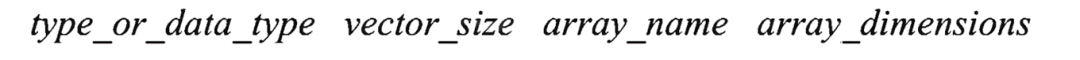

未壓縮數(shù)組的基本聲明語(yǔ)法為:

數(shù)組的維度定義了數(shù)組可以存儲(chǔ)的元素總數(shù)。未壓縮的數(shù)組可以用任意數(shù)量的維度聲明,每個(gè)維度存儲(chǔ)指定數(shù)量的元素。聲明數(shù)組維度有兩種編碼樣式:顯式地址和數(shù)組大小。

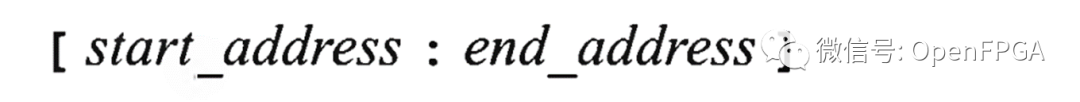

顯式地址樣式指定方括號(hào)之間數(shù)組維度的起始地址和結(jié)束地址,格式為:

Start_address 和 end_address可以是任何整數(shù)值,數(shù)組可以以地址0、地址512或被建模硬件所需的任何地址開始。起始地址和結(jié)束地址之間的范圍表示數(shù)組維度的大小(元素?cái)?shù))。

數(shù)組大小樣式定義要存儲(chǔ)在方括號(hào)中的元素?cái)?shù)(類似于C語(yǔ)言數(shù)組聲明樣式)。

[size]

使用array_size樣式,起始地址始終為0,結(jié)束地址始終為size-1

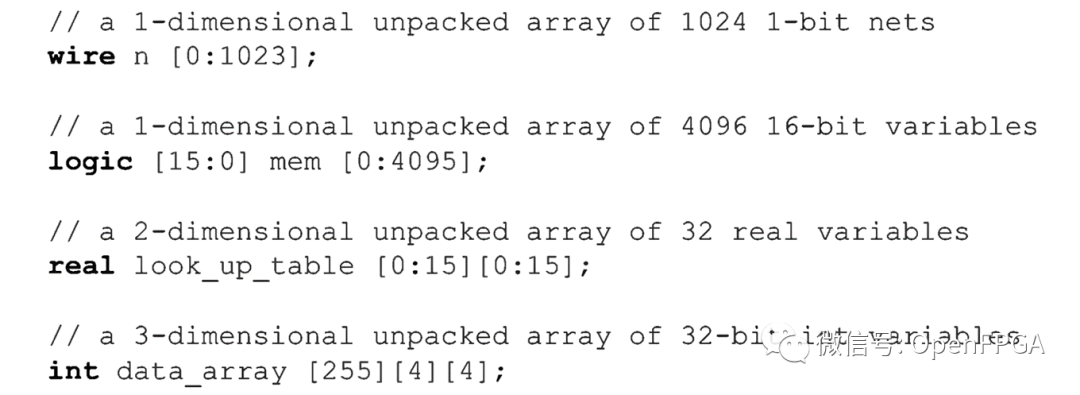

以下是一些未壓縮的數(shù)組聲明示例:

前面的mem聲明是16位logic變量的一維數(shù)組。一維陣列有時(shí)被稱為內(nèi)存陣列,因?yàn)樗ǔS糜?a target="_blank">仿真硬件內(nèi)存設(shè)備(如RAM和ROM)的存儲(chǔ)。

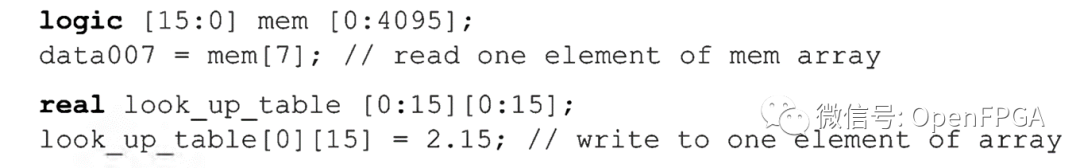

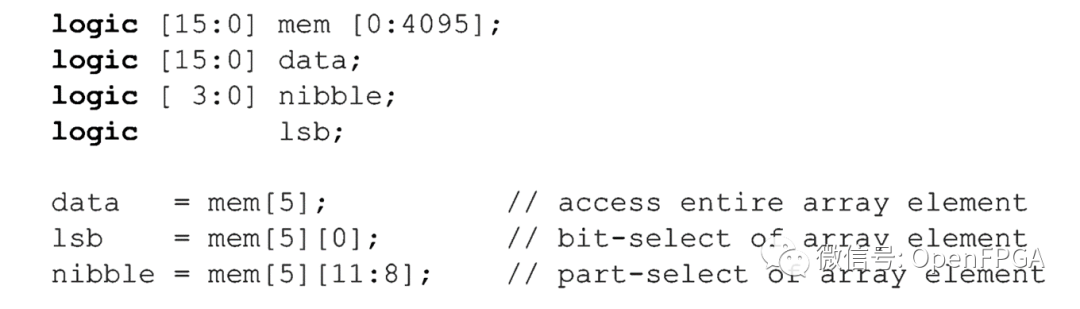

訪問數(shù)組元素

可以使用數(shù)組索引引用未壓縮數(shù)組的每個(gè)元素,索引緊跟在數(shù)組名稱之后,并且位于方括號(hào)中,多維數(shù)組需要多組方括號(hào)才能從數(shù)組中選擇單個(gè)元素:

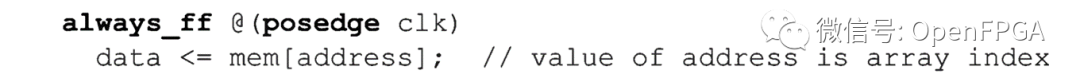

數(shù)組索引也可以是網(wǎng)絡(luò)或變量的值,如下一個(gè)示例所示:

復(fù)制數(shù)組(陣列)

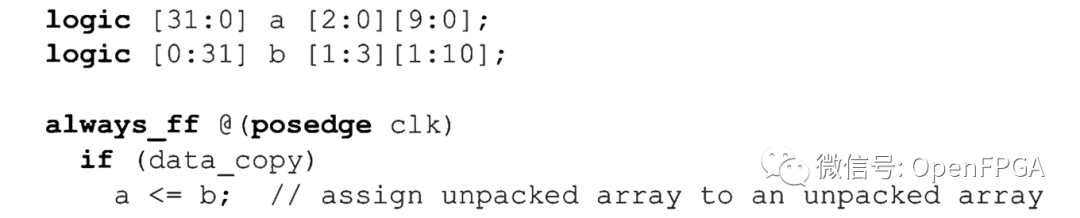

如果兩個(gè)數(shù)組(陣列)具有相同的布局,則可以使用賦值語(yǔ)句將一個(gè)未壓縮的數(shù)組(陣列)復(fù)制到另一個(gè)未壓縮的數(shù)組(陣列)。也就是說,這兩個(gè)數(shù)組(陣列)必須存儲(chǔ)相同向量大小的相同數(shù)據(jù)類型,必須具有相同的維度數(shù),并且每個(gè)維度的大小都相同-

數(shù)組(陣列)復(fù)制會(huì)將源數(shù)組(賦值的右側(cè))的每個(gè)元素復(fù)制到目標(biāo)數(shù)組(陣列)(賦值的左側(cè))中相應(yīng)的元素。兩個(gè)數(shù)組(陣列)的索引編號(hào)不需要相同。數(shù)組(陣列)的布局和類型必須完全匹配。

與復(fù)制數(shù)組(陣列)的方式類似,如果兩個(gè)切片的布局相同,則可以將數(shù)組(陣列)的一部分(稱為數(shù)組(陣列)切片)復(fù)制到另一個(gè)數(shù)組(陣列)的切片。切片是數(shù)組(陣列)一維內(nèi)的一個(gè)或多個(gè)連續(xù)編號(hào)的元素。

在成為SystemVerilog之前,最初的Verilog語(yǔ)言將對(duì)數(shù)組(陣列)的訪問限制為一次只能訪問數(shù)組中的一個(gè)元素。不允許對(duì)數(shù)組(陣列)的多個(gè)元素進(jìn)行數(shù)組(陣列)復(fù)制和讀/寫操作。

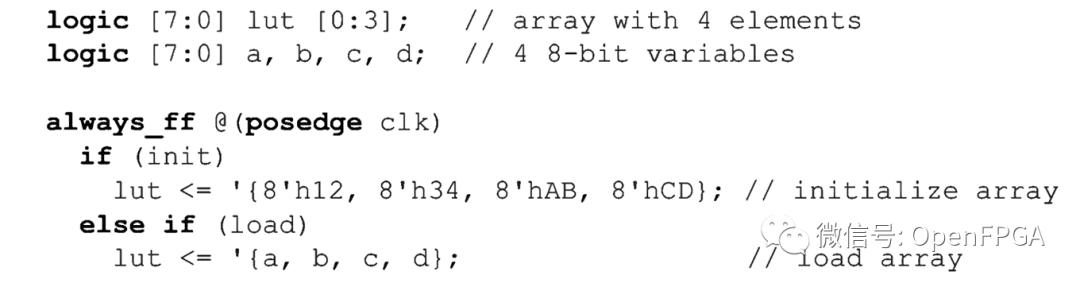

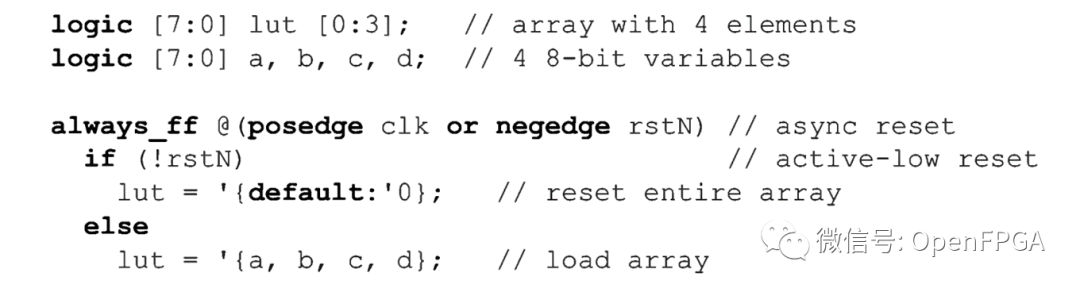

數(shù)組列表賦值

可以為未壓縮的數(shù)組或數(shù)組的一個(gè)片段分配一個(gè)值列表,這些值包含在每個(gè)數(shù)組維度的’{and}大括號(hào)之間。

列表語(yǔ)法類似于在C中為數(shù)組指定值列表,但在大括號(hào)前添加了撇號(hào)使用’-“作為開頭分隔符”表明,所包含的值是表達(dá)式列表,而不是SystemVerilog連接運(yùn)算符(后面會(huì)詳細(xì)介紹)。

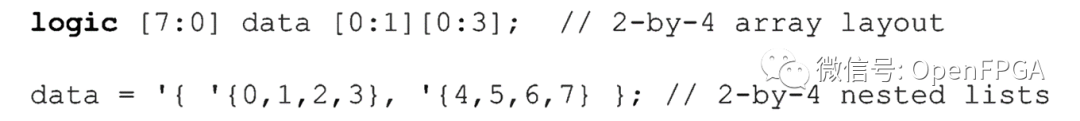

還可以使用嵌套列表為多維數(shù)組分配值列表。嵌套的列表集必須與數(shù)組的維度完全匹配。

此數(shù)組分配相當(dāng)于以下各項(xiàng)的單獨(dú)分配:

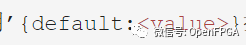

通過指定默認(rèn)值,可以為未壓縮數(shù)組的所有元素指定相同的值。默認(rèn)值是使用

指定的,如以下代碼段所示:

數(shù)組元素的位選擇和部分選擇

可以從數(shù)組元素向量中選擇一位或一組位。必須首先選擇數(shù)組的單個(gè)元素,然后進(jìn)行位選擇或部分選擇。

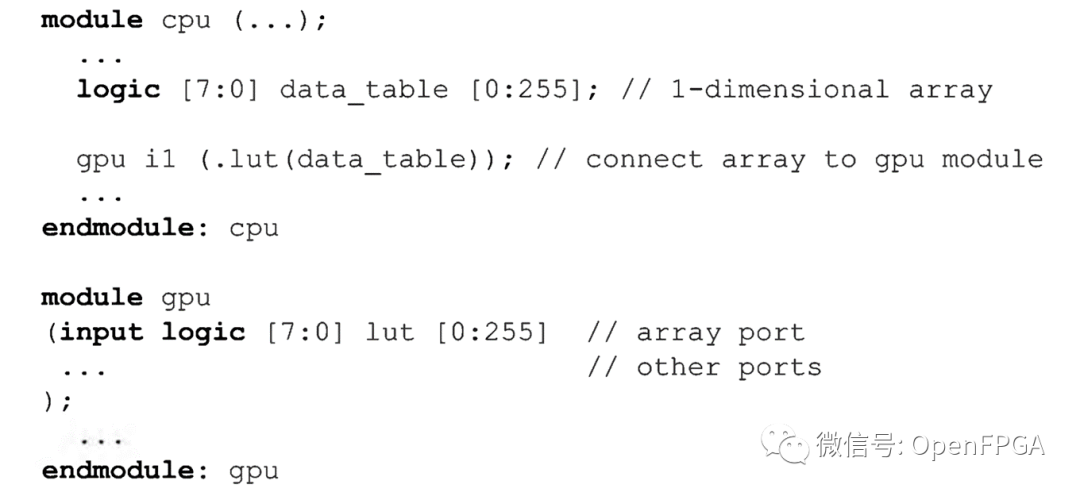

通過端口將數(shù)組傳遞給任務(wù)和函數(shù)。任何類型和任意數(shù)量的未壓縮數(shù)組都可以通過模塊端口傳遞,也可以傳遞到任務(wù)和函數(shù)參數(shù)。端口或任務(wù)/函數(shù)形式參數(shù)也必須聲明為數(shù)組,端口或參數(shù)數(shù)組必須與要傳遞的數(shù)組具有相同的布局(與數(shù)組復(fù)制的規(guī)則相同)。

最初的Verilog語(yǔ)言只允許簡(jiǎn)單的向量通過模塊端口,或傳遞到任務(wù)或函數(shù)參數(shù)。要傳遞上述示例中表數(shù)組的值,需要256個(gè)端口,數(shù)組的每個(gè)元素一個(gè)端口。

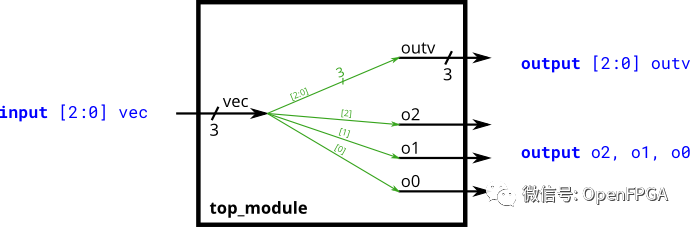

Problem 10-Vector0

題目說明

構(gòu)造一個(gè)電路,擁有 1 個(gè) 3 bit 位寬的輸入端口,4 個(gè)輸出端口。其中一個(gè)輸出端口直接輸出輸入的向量,剩下 3 個(gè)輸出端口分別各自輸出 3 bit 中的 1 bit。

這個(gè)題目的核心就是上面的圖片,模塊和端口已經(jīng)被定義好了,黑色的框圖以及箭頭代表模塊和端口。我們需要做的工作是完成圖中綠色的部分,其中箭頭上的小斜杠旁邊的數(shù)字代表該向量(總線)的位寬,用于將向量同 wire 信號(hào)區(qū)別開來。

模塊端口聲明

moduletop_module(

inputwire[2:0]vec,

outputwire[2:0]outv,

outputwireo2,

outputwireo1,

outputwireo0);

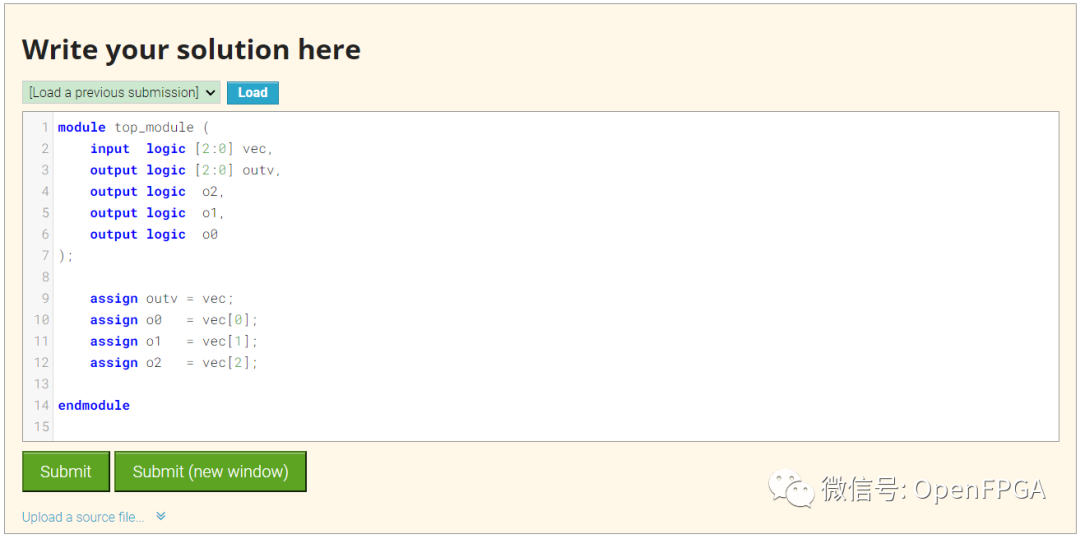

題目解析

這個(gè)題目重點(diǎn)是向量的選取和賦值,在文章最前面已經(jīng)介紹過了,大家仔細(xì)看過應(yīng)該很好理解。

moduletop_module(

inputlogic[2:0]vec,

outputlogic[2:0]outv,

outputlogico2,

outputlogico1,

outputlogico0

);

assignoutv=vec;

assigno0=vec[0];

assigno1=vec[1];

assigno2=vec[2];

endmodule

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅(后面會(huì)展示)。

這一題就結(jié)束了。

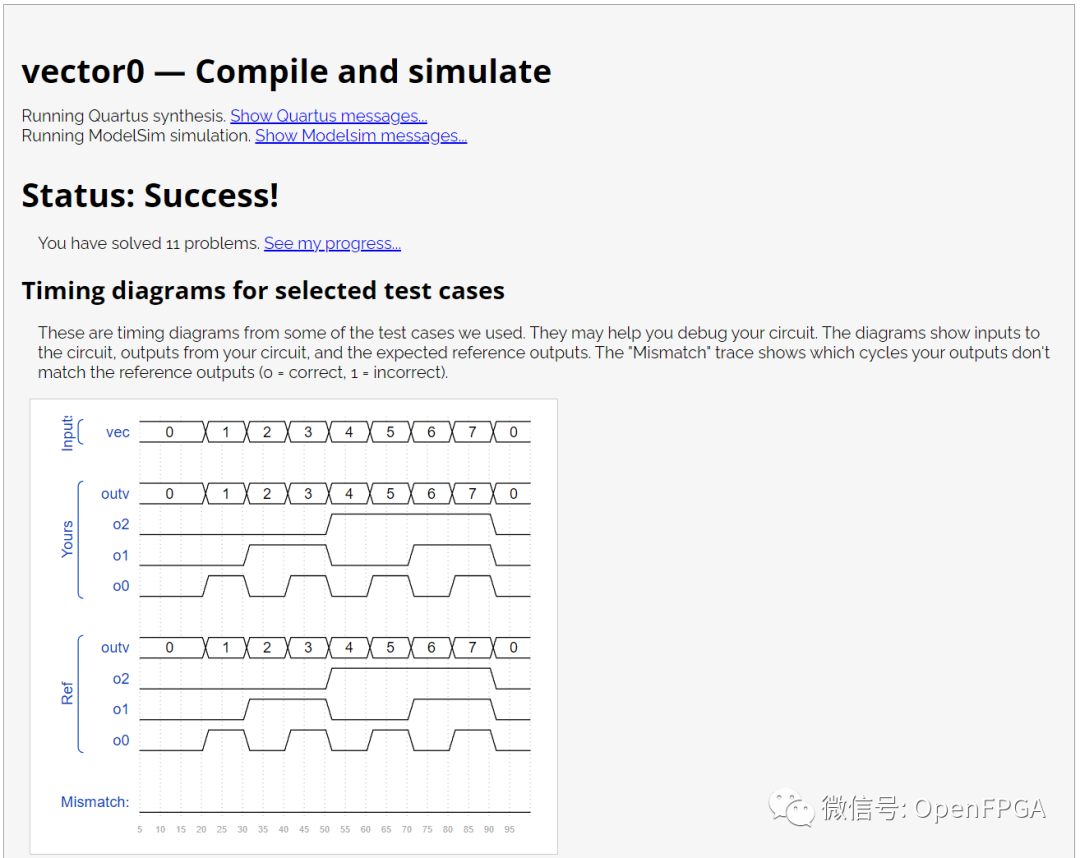

Problem 11-Vector1

題目說明

16 位輸入信號(hào)分別輸出 高 8 位 和低 8 位。

模塊端口聲明

`default_nettypenone//Disableimplicitnets.Reducessometypesofbugs.

moduletop_module(

inputwire[15:0]in,

outputwire[7:0]out_hi,

outputwire[7:0]out_lo);

通過添加`default_nettype none 宏定義會(huì)關(guān)閉隱式聲明功能,那么這樣一來,使用未聲明的變量就會(huì)變成一個(gè) Error 而不再只是 Warning。

題目解析

這道題難度不大主要是向量的選擇,但是要掌握的知識(shí)很多,這題前面由很多這方面的知識(shí)點(diǎn),包括壓縮數(shù)組和非壓縮數(shù)組,隱式轉(zhuǎn)換等,建議大家在做題前仔細(xì)閱讀題目前的知識(shí)點(diǎn)。

也可以查看下面的文章:

https://zhuanlan.zhihu.com/p/57452966

`default_nettypenone//Disableimplicitnets.Reducessometypesofbugs.

moduletop_module(

inputwirelogic[15:0]in,

outputvarlogic[7:0]out_hi,

outputvarlogic[7:0]out_lo);

assignout_hi=in[15:8];

assignout_lo=in[7:0];

endmodule

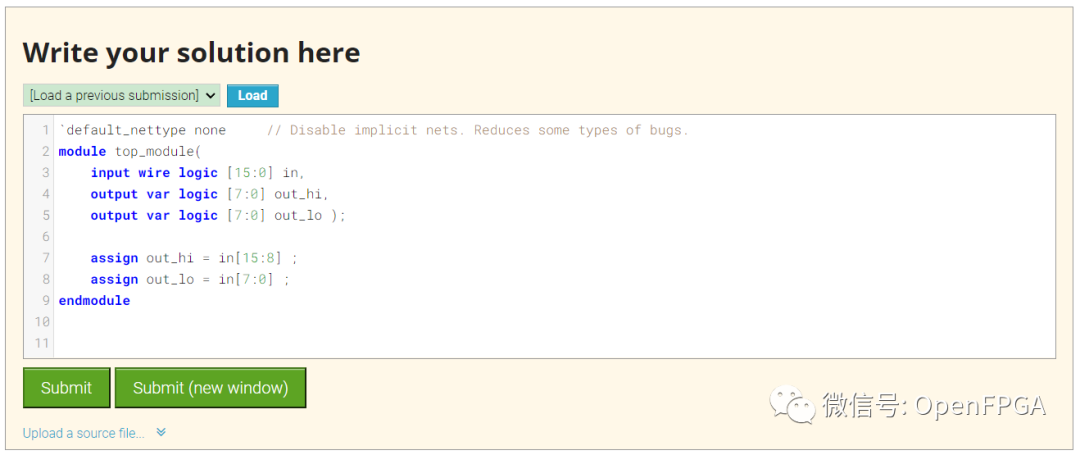

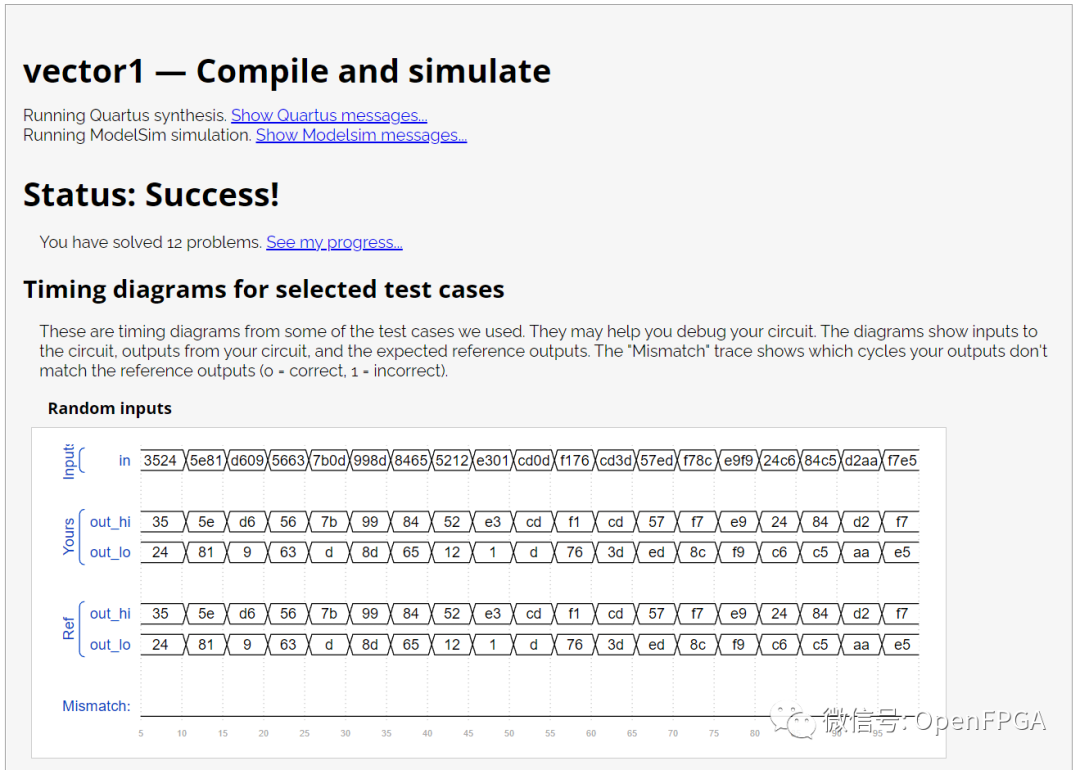

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅(后面會(huì)展示)。

這一題就結(jié)束了。

Problem 12-Vector2

題目說明

一個(gè) 32 位的向量可以看做由 4 個(gè)字節(jié)組成(bits[31:24],[23:16],等等)。構(gòu)建一個(gè)電路,將輸入向量的字節(jié)順序顛倒,也就是字節(jié)序大小端轉(zhuǎn)換。

如:

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

模塊端口聲明

moduletop_module(

input[31:0]in,

output[31:0]out);

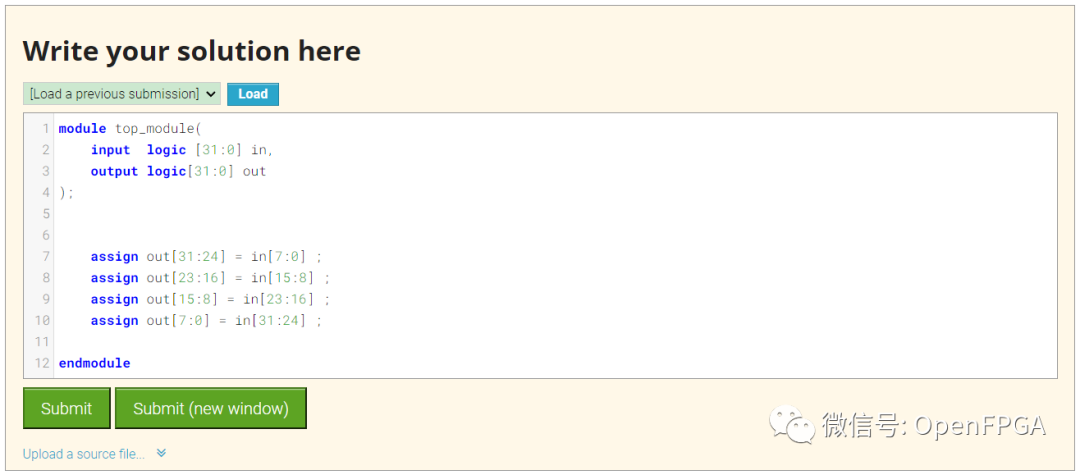

題目解析

還是在聯(lián)系向量的提取和賦值。

moduletop_module(

inputlogic[31:0]in,

outputlogic[31:0]out

);

assignout[31:24]=in[7:0];

assignout[23:16]=in[15:8];

assignout[15:8]=in[23:16];

assignout[7:0]=in[31:24];

endmodule

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅(后面會(huì)展示)。

這一題就結(jié)束了。

PS:下面的答案也是對(duì)的

assignout={in[7-:8],in[15-:8],in[23-:8],in[31-:8]};

可以自行查找知識(shí)學(xué)習(xí)上面的寫法。

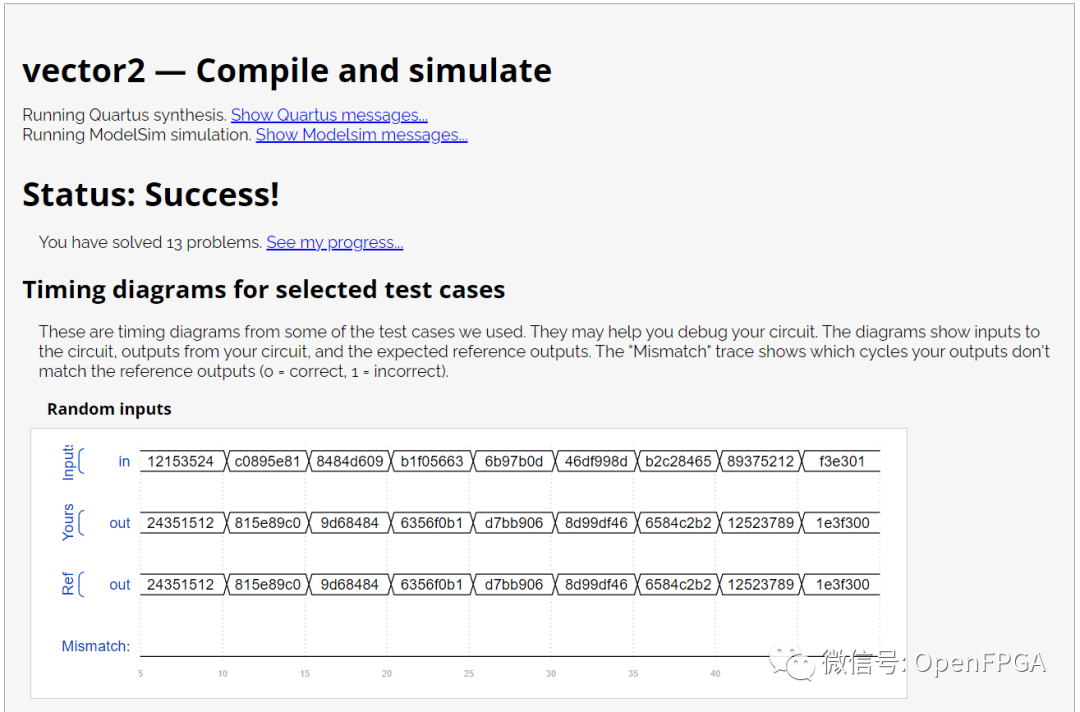

Problem 13-Vectorgates

題目說明

a,b是兩個(gè) 3bit 寬的輸入變量,要求輸出 a,b 逐位或,a,b 邏輯或以及 a,b 按位取反的結(jié)果,其中 b 在高位。

問題的核心就是上面的圖片,模塊和端口已經(jīng)被定義好了,黑色的框圖以及箭頭代表模塊和端口。我們需要做的工作是完成圖中綠色的部分。

模塊端口聲明

moduletop_module(

input[2:0]a,

input[2:0]b,

output[2:0]out_or_bitwise,

outputout_or_logical,

output[5:0]out_not

);

題目解析

這個(gè)題目還是挺繞的,難度不是很大,理解題目就能寫出來,這里除了上一個(gè)題目的向量提取和賦值以外,還由一個(gè)知識(shí)點(diǎn)-邏輯求反運(yùn)算符(!)和按位反轉(zhuǎn)運(yùn)算符(~)之間的區(qū)別~

之前簡(jiǎn)單介紹了以下,這次就詳細(xì)介紹,后續(xù)就不展開說了。

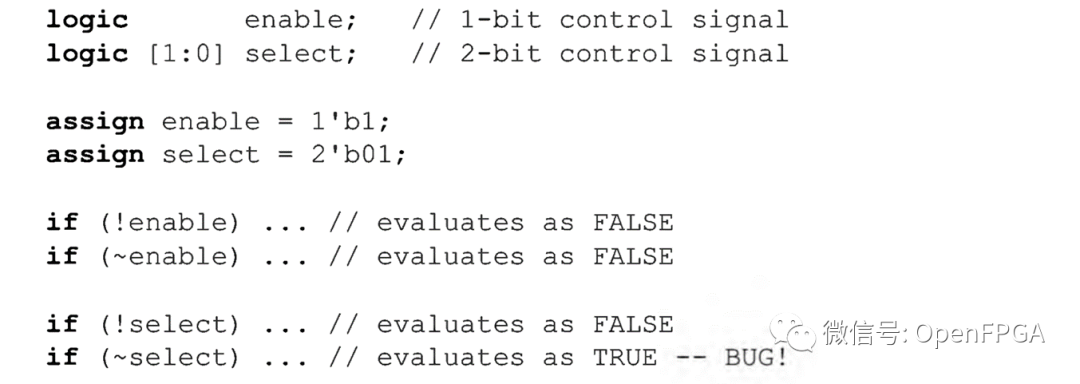

應(yīng)注意不要混淆邏輯求反運(yùn)算符(!)以及按位反轉(zhuǎn)運(yùn)算符(~)。求反運(yùn)算符對(duì)其操作數(shù)執(zhí)行真/假求值,并返回表示真、假或未知結(jié)果的1位值。按位反轉(zhuǎn)運(yùn)算符對(duì)操作數(shù)的每一位(補(bǔ)碼)執(zhí)行邏輯反轉(zhuǎn),并返回與操作數(shù)相同位寬的值。

在某些操作中,這些操作的結(jié)果恰好相同,但在其他操作中,它們返回的值非常不同。當(dāng)運(yùn)算符與決策語(yǔ)句一起被錯(cuò)誤使用時(shí),這種差異可能導(dǎo)致錯(cuò)誤代碼。考慮下面的例子:

前面代碼片段的最后兩行之所以不同,是因?yàn)檫@兩個(gè)運(yùn)算符的工作方式不同——邏輯求反運(yùn)算符(!)通過將兩位相加或相減,對(duì)2位選擇執(zhí)行真/假計(jì)算,然后反轉(zhuǎn)1位結(jié)果,按位反轉(zhuǎn)運(yùn)算符(~)只反轉(zhuǎn)2位選擇向量的每一位的值,并返回2位結(jié)果。if語(yǔ)句然后對(duì)2位向量進(jìn)行真/假測(cè)試,該向量的計(jì)算結(jié)果為真,因?yàn)榉崔D(zhuǎn)后的值仍有一位設(shè)置為1。

| 最佳實(shí)踐指南5-1 |

|---|

| 使用按位反轉(zhuǎn)運(yùn)算符反轉(zhuǎn)值的位,不要使用按位反轉(zhuǎn)運(yùn)算符對(duì)邏輯求反運(yùn)算符求反。相反,使用邏輯求反運(yùn)算符來否定真/假測(cè)試的結(jié)果。不要使用邏輯求反運(yùn)算符反轉(zhuǎn)值。 |

| 最佳實(shí)踐指南5-2 |

|---|

| 僅使用邏輯求反運(yùn)算符求反來測(cè)試標(biāo)量(1位)值,而不是 對(duì)向量執(zhí)行真/假測(cè)試。 |

如果向量的任何位為1,邏輯運(yùn)算將返回true,這可能會(huì)導(dǎo)致在測(cè)試特定位時(shí)出現(xiàn)設(shè)計(jì)錯(cuò)誤。計(jì)算向量值時(shí),使用等式或關(guān)系運(yùn)算符測(cè)試可接受的值。

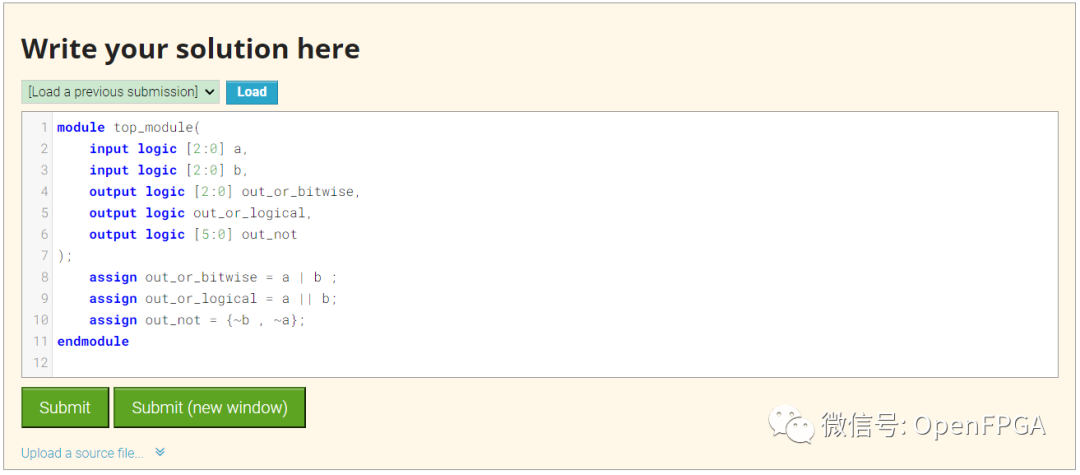

moduletop_module(

inputlogic[2:0]a,

inputlogic[2:0]b,

outputlogic[2:0]out_or_bitwise,

outputlogicout_or_logical,

outputlogic[5:0]out_not

);

assignout_or_bitwise=a|b;

assignout_or_logical=a||b;

assignout_not={~b,~a};

endmodule

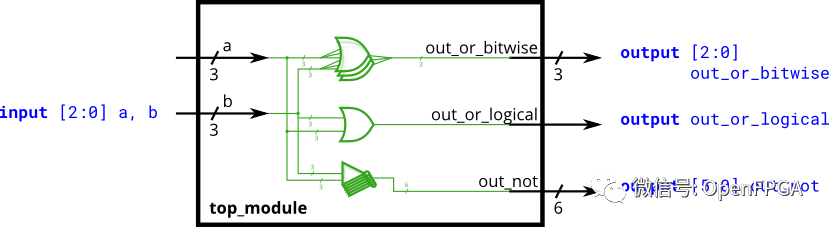

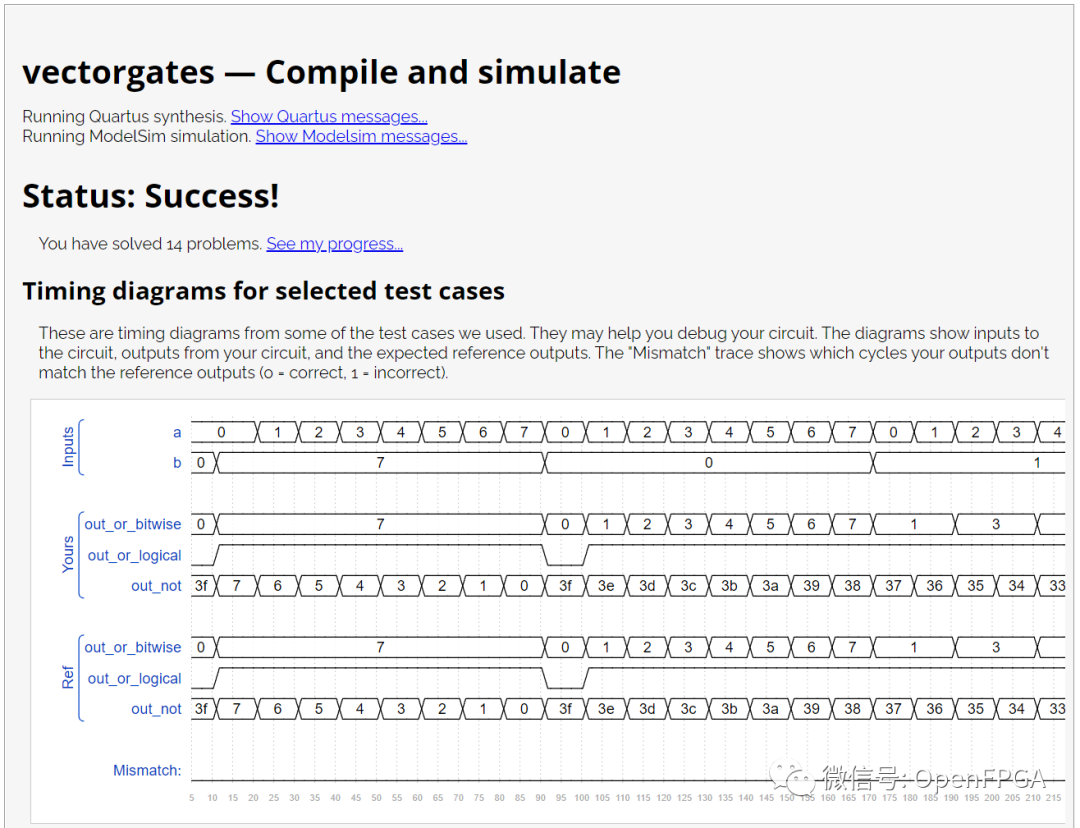

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅(后面會(huì)展示)。

這一題就結(jié)束了。

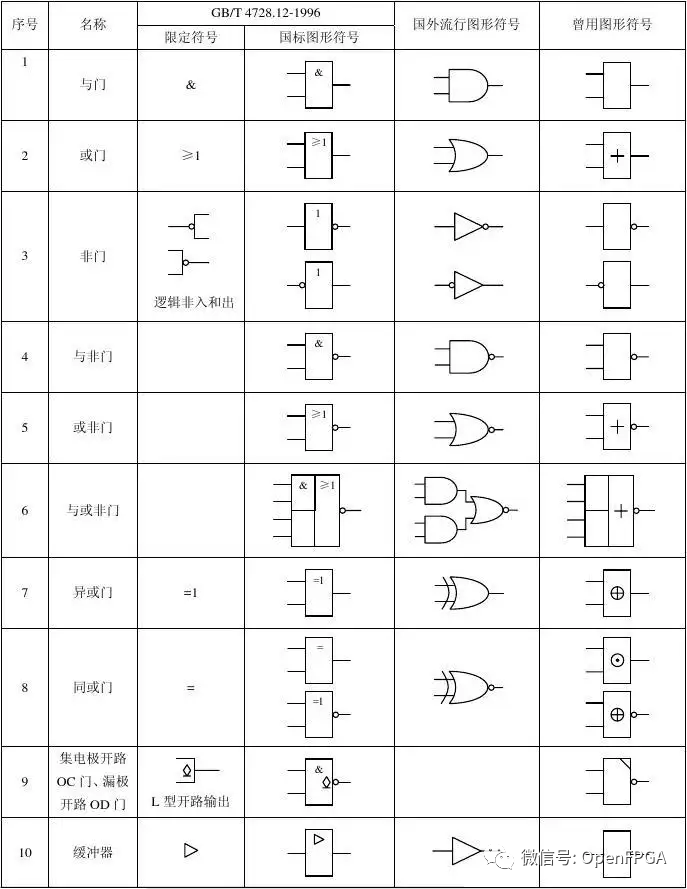

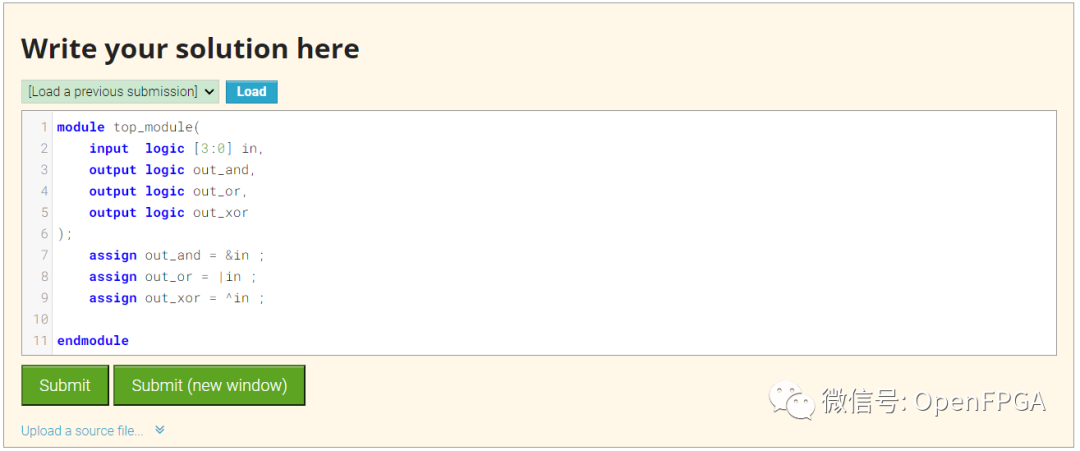

Problem 14-Gates4

題目說明

分別構(gòu)建一個(gè) 4 輸入與門,或門以及異或門。

模塊端口聲明

moduletop_module(

input[3:0]in,

outputout_and,

outputout_or,

outputout_xor

);

題目解析

這一題的關(guān)鍵是多輸入與、或以及異或門的實(shí)現(xiàn),學(xué)過數(shù)電的化難度就不是很大了。

moduletop_module(

inputlogic[3:0]in,

outputlogicout_and,

outputlogicout_or,

outputlogicout_xor

);

assignout_and=∈

assignout_or=|in;

assignout_xor=^in;

endmodule

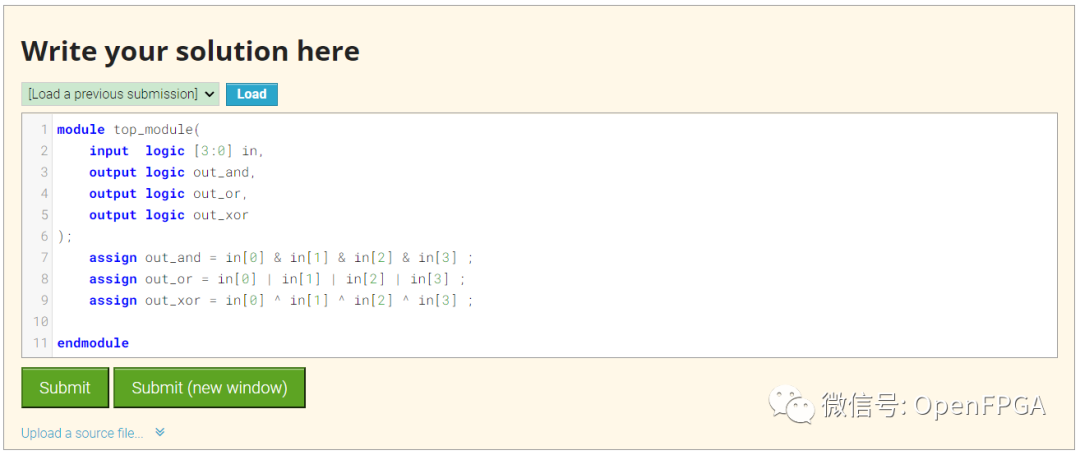

或者

moduletop_module(

inputlogic[3:0]in,

outputlogicout_and,

outputlogicout_or,

outputlogicout_xor

);

assignout_and=in[0]&in[1]&in[2]&in[3];

assignout_or=in[0]|in[1]|in[2]|in[3];

assignout_xor=in[0]^in[1]^in[2]^in[3];;

endmodule

第二種方式更易于理解,第一種方式就是上面的按位操作符,可以翻看上面的說明。

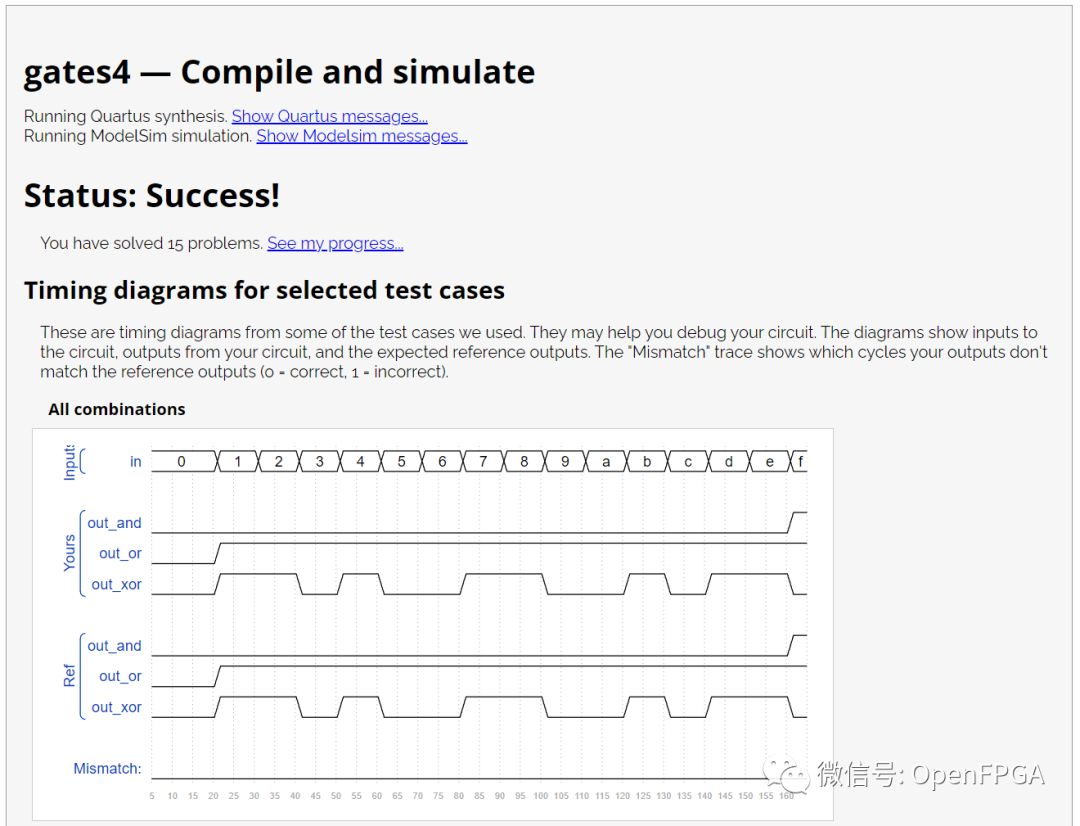

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

總結(jié)

今天的5道題就結(jié)束了,整體難度不大,后面的題目難度會(huì)越來越大~

最后我這邊做題的代碼也是個(gè)人理解使用,有錯(cuò)誤歡迎大家批評(píng)指正,祝大家學(xué)習(xí)愉快~

代碼鏈接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

審核編輯 :李倩

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111966 -

向量

+關(guān)注

關(guān)注

0文章

55瀏覽量

11861 -

數(shù)組

+關(guān)注

關(guān)注

1文章

419瀏覽量

26408

原文標(biāo)題:HDLBits: 在線學(xué)習(xí) SystemVerilog(三)-Problem 10-14

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

KMPHM在線監(jiān)測(cè)系統(tǒng) 讓設(shè)備故障無處遁形#在線監(jiān)測(cè)#振動(dòng)在線監(jiān)測(cè)

KMPHM在線監(jiān)測(cè)平臺(tái)賦能設(shè)備管理升級(jí)#在線監(jiān)測(cè)#振動(dòng)監(jiān)測(cè)

微氣象在線監(jiān)測(cè)裝置氣象環(huán)境實(shí)時(shí)在線監(jiān)測(cè)數(shù)據(jù)穩(wěn)定可靠

KMPHM在線監(jiān)測(cè)平臺(tái)實(shí)現(xiàn)設(shè)備高效管理#在線監(jiān)測(cè)#振動(dòng)監(jiān)測(cè)#振動(dòng)在線監(jiān)測(cè)

TSW14J10 FMC-USB轉(zhuǎn)接卡用戶指南

淺談10kV高壓開關(guān)柜在線測(cè)溫技術(shù)以及選型

賽盛在線平臺(tái)疑問解答系列(二)

快來KM振動(dòng)在線監(jiān)測(cè)系統(tǒng)參與石化設(shè)備運(yùn)維大會(huì)的風(fēng)采吧!#振動(dòng)在線監(jiān)測(cè)#振動(dòng)監(jiān)測(cè)

KM振動(dòng)在線監(jiān)測(cè)系統(tǒng)助力設(shè)備煥新升級(jí)#振動(dòng)在線監(jiān)測(cè)#振動(dòng)監(jiān)測(cè)#在線監(jiān)測(cè)

賽盛EMC在線學(xué)習(xí)平臺(tái):揭秘學(xué)習(xí)寶典&amp;工具秘籍!

三星電子將在線舉辦晶圓代工論壇

KMPHM振動(dòng)在線監(jiān)測(cè)助力企業(yè)輕裝上陣#振動(dòng)在線監(jiān)測(cè) #在線監(jiān)測(cè) #振動(dòng)監(jiān)測(cè)

Verilog testbench問題求助

HDLBits: 在線學(xué)習(xí)SystemVerilog(三)-Problem 10-14

HDLBits: 在線學(xué)習(xí)SystemVerilog(三)-Problem 10-14

評(píng)論