在高速PCB設(shè)計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現(xiàn)功能不正常的現(xiàn)象。

串擾(crosstalk)

指當信號在傳輸線上傳播時,因電磁耦合而對相鄰的傳輸線產(chǎn)生的不期望的電壓噪聲干擾。這種干擾是由于傳輸線之間的互感和互容引起的。PCB板層的參數(shù)、信號線間距、驅(qū)動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

克服串擾的主要措施是:

加大平行布線的間距,遵循3W規(guī)則;

在平行線間插入接地的隔離線;

減小布線層與地平面的距離。

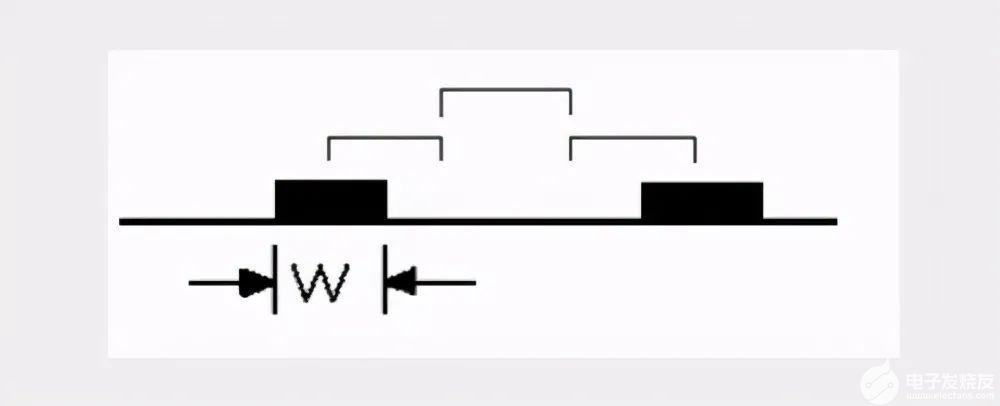

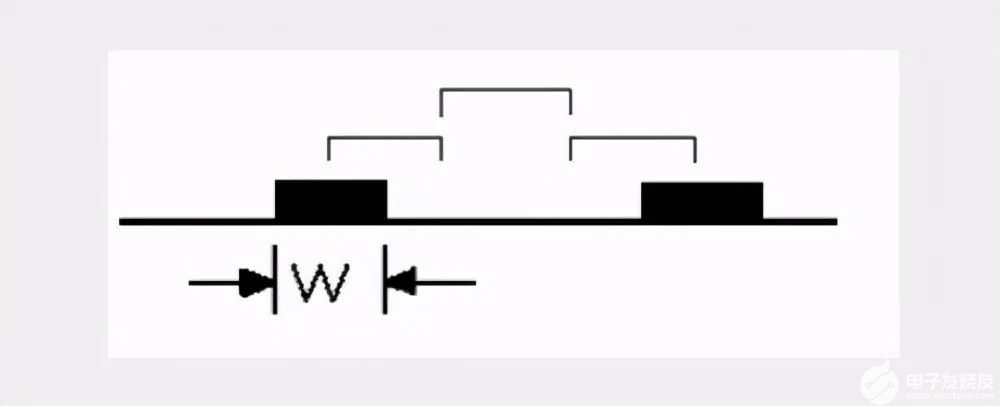

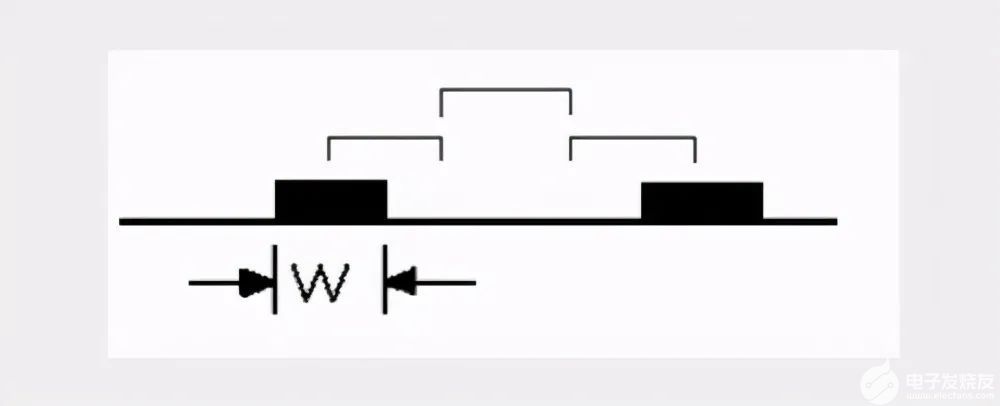

3W規(guī)則

為了減少線間串擾,應(yīng)保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持70%的電場不互相干擾,稱為3W規(guī)則。如要達到98%的電場不互相干擾,可使用10W的間距。

https://www.oneyac.com/

注:在實際PCB設(shè)計中,3W規(guī)則并不能完全滿足避免串擾的要求。

避免PCB中出現(xiàn)串擾的方法

為避免PCB中出現(xiàn)串擾,工程師可以從PCB設(shè)計和布局方面來考慮,如:

1、根據(jù)功能分類邏輯器件系列,保持總線結(jié)構(gòu)被嚴格控制。

2、最小化元器件之間的物理距離。

3、高速信號線及元器件(如晶振)要遠離I/O互連接口及其他易受數(shù)據(jù)干擾及耦合影響的區(qū)域。

4、對高速線提供正確的終端。

5、避免長距離互相平行的走線布線,提供走線間足夠的間隔以最小化電感耦合 。

6、相臨層(微帶或帶狀線)上的布線要互相垂直,以防止層間的電容耦合。

7、降低信號到地平面的距離間隔。

8、分割和隔離高噪聲發(fā)射源(時鐘、I/O、高速互連),不同的信號分布在不同的層中。

9、盡可能地增大信號線間的距離,這可以有效地減少容性串擾。

10、降低引線電感,避免電路使用具有非常高阻抗的負載和非常低阻抗的負載,盡量使模擬電路負載阻抗穩(wěn)定在10Ω~10kΩ之間。因為高阻抗的負載將增加容性串擾,在使用非常高阻抗負載的時候,由于工作電壓較高,導致容性串擾增大,而在使用非常低阻抗負載的時候,由于工作電流很大,感性串擾將增加。

11、將高速周期信號布置在PCB板內(nèi)層。

12、使用阻抗匹配技術(shù),以保證信號完整性,防止過沖。

13、注意對具有快速上升沿(tr≤3ns)的信號,進行包地等防串擾處理,將一些受EFTlB或ESD干擾且未經(jīng)濾波處理的信號線布置在PCB的邊緣。

14、盡量采用地平面,使用地平面的信號線相對于不使用地平面的信號線來說將獲得15~20dB的衰減。

15、信號高頻信號和敏感信號進行 包地處理,雙面板中使用包地技術(shù)將獲得10~15dB的衰減。

16、使用平衡線,屏蔽線或同軸線。

17、對騷擾信號線和敏感線進行濾波處理。

18、合理設(shè)置層和布線,合理設(shè)置布線層和布線間距,減小并行信號長度,縮短信號層與平面層的間距,增大信號線間距,減小并行信號線長度(在關(guān)鍵長度范圍內(nèi)),這些措施都可以有效減小串擾。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4358文章

23442瀏覽量

407694 -

串擾

+關(guān)注

關(guān)注

4文章

189瀏覽量

27366

發(fā)布評論請先 登錄

關(guān)于高速PCB設(shè)計的串擾知識這篇文章講清楚了

高速PCB設(shè)計常見問題

什么是小間距QFN封裝PCB設(shè)計串擾抑制?

解決PCB設(shè)計消除串擾的辦法

高速PCB設(shè)計中的串擾分析與控制

串擾在高速PCB設(shè)計中的影響分析

高速PCB設(shè)計中如何消除串擾?

如何解決PCB串擾問題

10個和高速PCB設(shè)計相關(guān)的重要知識分享

關(guān)于高速PCB設(shè)計的串擾知識

關(guān)于高速PCB設(shè)計的串擾知識

評論