之前在網(wǎng)上看到了感芯科技MC3172MCU,看介紹有硬件64位多線程處理,甚是感興趣,最近有幸收到一塊開(kāi)發(fā)板,所以進(jìn)行部分性能方面的測(cè)試。

MC3172簡(jiǎn)介

感芯科技第一款32 位 RISC 處理器 MC3172 ,業(yè)內(nèi)首個(gè)64線程同步并行運(yùn)行,線程資源可按需配置,

共享代碼段空間與數(shù)據(jù)段空間,硬件級(jí)實(shí)時(shí)響應(yīng),無(wú)需中斷服務(wù)程序,無(wú)需實(shí)時(shí)操作系統(tǒng)。

基于RISC-V RV32IMC 指令集,100%單周期指令,最高200MHz主頻,3.37coremark/MHz。

數(shù)據(jù)段與代碼段共享128K字節(jié)SRAM,可按需配置為96K代碼空間加32K數(shù)據(jù)空間,或64K代碼空間加

64K數(shù)據(jù)空間,或32K代碼空間加96K數(shù)據(jù)空間,靈活應(yīng)對(duì)各種應(yīng)用場(chǎng)景。

擁有豐富片內(nèi)外設(shè):12個(gè)可配置通信接口,可按需配置為UASRT或SPI或USB或CAN總線形式,滿(mǎn)足多通

信端口需求;6個(gè)雙緩沖24位計(jì)數(shù)器,可提供高精度PWM與輸入捕捉;64個(gè)GPIO,可提供豐富的自定義控制

接口。

產(chǎn)品特性

內(nèi)核 Core:

- 基于 RV32IMC 指令集,單周期乘法

- 64路線程同步并行運(yùn)行,無(wú)需線程切換

- 線程資源可按需配置且無(wú)需操作系統(tǒng)

- 3.37coremark/MHz

- 100%單周期指令,時(shí)序確定

- 最高 200MHz 系統(tǒng)主頻

存儲(chǔ)器:

- 128KB SRAM可按需分配為:

96K代碼空間+32K數(shù)據(jù)空間

64K代碼空間+64K數(shù)據(jù)空間

32K代碼空間+96K數(shù)據(jù)空間

電源管理和低功耗:

- 核心供電電壓范圍:1.8V~1.98V,

- GPIO供電電壓:1.8V~3.3V

系統(tǒng)時(shí)鐘、復(fù)位

- 內(nèi)嵌 200MHz RC 振蕩器

- 內(nèi)嵌 8MHz RC 振蕩器

- 外部支持 4MHz~40MHz 高速振蕩器

- 外部支持 最高133MHz 輸入時(shí)鐘

- 上電復(fù)位(POR)

多線程實(shí)時(shí)性測(cè)試

由于這個(gè)芯片其他的測(cè)試?yán)缫_配置、定時(shí)器配置、串口配置等網(wǎng)友已經(jīng)有諸多帖子,所以我只對(duì)目前我感覺(jué)好奇的多線程實(shí)時(shí)性進(jìn)行測(cè)試。

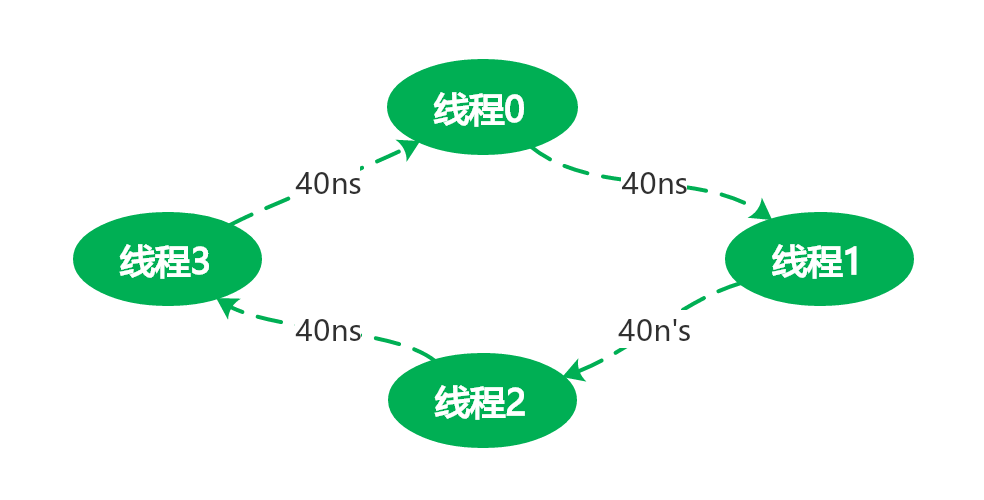

1.多線程配置(使用線程0、1、2、3,分頻?主頻)

這里我們4個(gè)線程組每個(gè)僅使用1個(gè)線程,分頻每個(gè)均為?主頻。線程空間定位2048字節(jié)。

2.測(cè)試思路和主要程序代碼

在僅配置4個(gè)線程的情況下,我們?cè)诓煌木€程中通過(guò)切換GPIO0、1、2的引腳電平來(lái)判斷具體線程的響應(yīng)時(shí)序。具體配置如下:

線程0:用來(lái)初始化GPIOA引腳的0、1、2為輸出引腳。初始化完成后,設(shè)定全局變量u8g_sysInitSuccessFlg為1;

初始化完成后,每等待150個(gè)延時(shí)周期,對(duì)u8g_gpioAllowToggleFlg取反,并反轉(zhuǎn)GPIOA0。

線程1:等待線程0對(duì)GPIO初始化完成后,實(shí)時(shí)檢測(cè)u8g_gpioAllowToggleFlg的狀態(tài),并對(duì)GPIOA1進(jìn)行翻轉(zhuǎn)。

線程2:等待線程0對(duì)GPIO初始化完成后,實(shí)時(shí)檢測(cè)u8g_gpioAllowToggleFlg的狀態(tài),并對(duì)GPIOA2進(jìn)行翻轉(zhuǎn)。

通過(guò)對(duì)比上升沿的時(shí)間差,即可知道線程運(yùn)行的時(shí)序差。

volatile u8 u8g_sysInitSuccessFlg=0;

volatile u8 u8g_gpioAllowToggleFlg=0;

void thread0_main(void)

{

while(1){

u32 u32gpioToggleDelayCnt;

INTDEV_SET_CLK_RST(GPIOA_BASE_ADDR,(INTDEV_RUN|INTDEV_IS_GROUP0|INTDEV_CLK_IS_CORECLK_DIV2));

GPIO_SET_OUTPUT_EN_VALUE(GPIOA_BASE_ADDR,GPIO_PIN0,GPIO_SET_ENABLE);

GPIO_SET_OUTPUT_EN_VALUE(GPIOA_BASE_ADDR,GPIO_PIN1,GPIO_SET_ENABLE);

GPIO_SET_OUTPUT_EN_VALUE(GPIOA_BASE_ADDR,GPIO_PIN2,GPIO_SET_ENABLE);

GPIO_SET_OUTPUT_EN_VALUE(GPIOA_BASE_ADDR,GPIO_PIN3,GPIO_SET_ENABLE);

u8g_sysInitSuccessFlg = 1;

while(1){

u32gpioToggleDelayCnt = 150;

while(u32gpioToggleDelayCnt--){NOP();}

u8g_gpioAllowToggleFlg = !u8g_gpioAllowToggleFlg;

GPIO_SET_OUTPUT_PIN_INV(GPIOA_BASE_ADDR,GPIO_PIN0);

}

}

thread_end();

}

void thread1_main(void)

{

while(1){

while(!u8g_sysInitSuccessFlg){NOP();}

while(1){

if(u8g_gpioAllowToggleFlg){

GPIO_SET_OUTPUT_PIN_TO_1(GPIOA_BASE_ADDR,GPIO_PIN1);

}else{

GPIO_SET_OUTPUT_PIN_TO_0(GPIOA_BASE_ADDR,GPIO_PIN1);

}

}

}

thread_end();

}

void thread2_main(void)

{

while(1){

while(!u8g_sysInitSuccessFlg){NOP();}

while(1){

if(u8g_gpioAllowToggleFlg){

GPIO_SET_OUTPUT_PIN_TO_1(GPIOA_BASE_ADDR,GPIO_PIN2);

}else{

GPIO_SET_OUTPUT_PIN_TO_0(GPIOA_BASE_ADDR,GPIO_PIN2);

}

}

}

thread_end();

}

3.測(cè)試結(jié)果

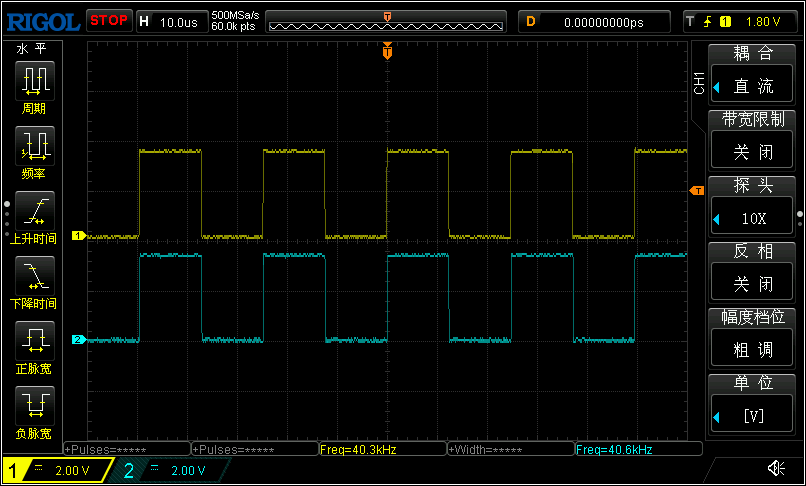

信號(hào)說(shuō)明:

黃色:GPIOA0電平 藍(lán)色:GPIOA1電平

(1).整體波形

整體波形看起來(lái)線程基本時(shí)同時(shí)切換,同步運(yùn)行,下面放大看看。

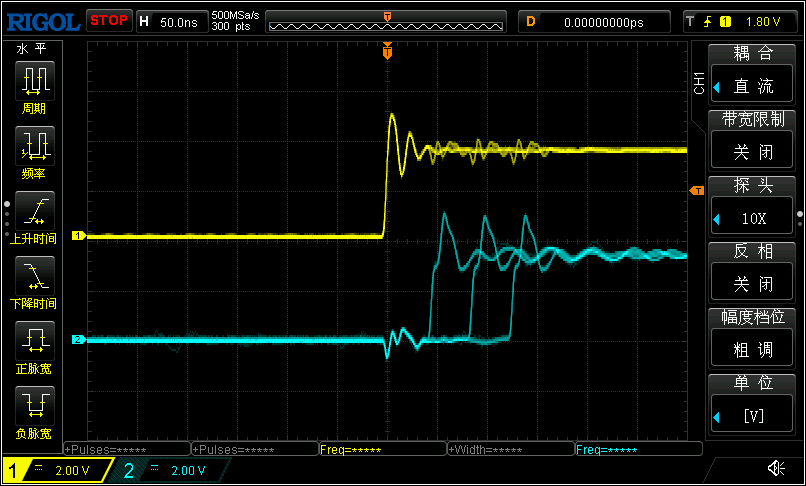

(2).上升沿觸發(fā)波形

注意:這里采用示波器的auto觸發(fā)模式,可以抓到每次觸發(fā)的時(shí)間會(huì)有不同,

- 最快從線程1切換到線程2的時(shí)間為40ns左右。

- 最慢從線程1切換到線程2的時(shí)間為120ns左右。

(3)結(jié)果分析

目前芯片配置為內(nèi)部高速RC時(shí)鐘200Mhz,配置每個(gè)線程的主頻為?主頻,也就是50Mhz。

此時(shí)對(duì)應(yīng)的線程切換時(shí)間范圍應(yīng)該在40ns~120ns之間。

我分析在當(dāng)前配置下,硬件核心線程切換邏輯是:

審核編輯:湯梓紅

-

mcu

+關(guān)注

關(guān)注

146文章

17886瀏覽量

361596 -

多線程

+關(guān)注

關(guān)注

0文章

279瀏覽量

20339 -

RISC-V

+關(guān)注

關(guān)注

46文章

2510瀏覽量

48383

發(fā)布評(píng)論請(qǐng)先 登錄

一種實(shí)時(shí)多線程VSLAM框架vS-Graphs介紹

迅為RK3588開(kāi)發(fā)板實(shí)時(shí)系統(tǒng)編譯-Preemption系統(tǒng)/ Xenomai系統(tǒng)編譯-實(shí)時(shí)系統(tǒng)測(cè)試-Preemption測(cè)試

請(qǐng)問(wèn)如何在Python中實(shí)現(xiàn)多線程與多進(jìn)程的協(xié)作?

請(qǐng)問(wèn)rt-thread studio如何進(jìn)行多線程編譯?

華為云 X 實(shí)例 CPU 性能測(cè)試詳解與優(yōu)化策略

socket 多線程編程實(shí)現(xiàn)方法

航電實(shí)時(shí)測(cè)試系統(tǒng)解決方案

Python中多線程和多進(jìn)程的區(qū)別

摩爾線程與羽人科技完成大語(yǔ)言模型訓(xùn)練測(cè)試

延時(shí)僅33us,Linux-RT實(shí)時(shí)性能測(cè)試分享—基于瑞芯微RK3562J國(guó)產(chǎn)平臺(tái)

實(shí)測(cè)14us,Linux-RT實(shí)時(shí)性能及開(kāi)發(fā)案例分享—基于全志T507-H國(guó)產(chǎn)平臺(tái)

LWIP多線程強(qiáng)烈建議開(kāi)啟LWIP_ASSERT_CORE_LOCKED宏,這個(gè)在RTT里面要怎么實(shí)現(xiàn)?

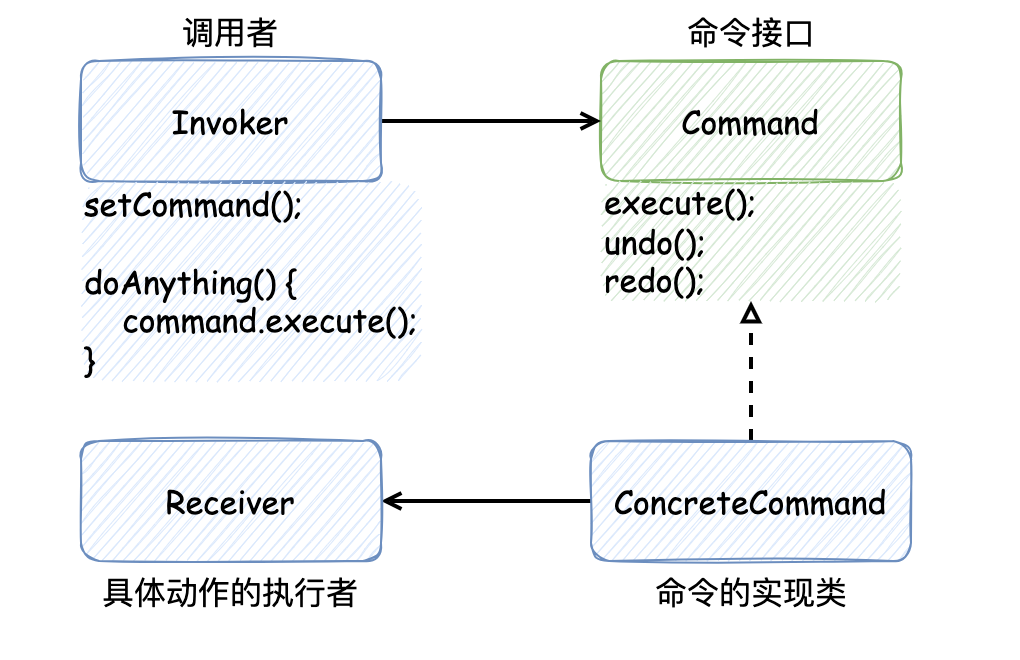

從多線程設(shè)計(jì)模式到對(duì) CompletableFuture 的應(yīng)用

感芯科技MC3172多線程實(shí)時(shí)性測(cè)試

感芯科技MC3172多線程實(shí)時(shí)性測(cè)試

評(píng)論