在射頻電路研究學(xué)習(xí)的過(guò)程中,相信大家都遇到過(guò)在電路中信號(hào)頻率的變高、邊沿變陡、電路板的尺寸變小、布線的密度變大等問(wèn)題,這些幾乎是不可避免的問(wèn)題。

這種影響信號(hào)完整性的問(wèn)題叫做串?dāng)_,在電路計(jì)中普遍存在,有可能出現(xiàn)在芯片、PCB板、連接器、芯片封裝和連接器電纜等器件上。如果串?dāng)_超過(guò)一定的限度就會(huì)引起電路的誤觸發(fā),導(dǎo)致系統(tǒng)無(wú)法正常工作。

因此了解串?dāng)_問(wèn) 題產(chǎn)生的機(jī)理并掌握解決串?dāng)_的設(shè)計(jì)方法,對(duì)于工程師來(lái)說(shuō)是相當(dāng)重要的,如果處理不好可能會(huì)嚴(yán)重影響整個(gè)電路的效果。

A、什么是串?dāng)_

串?dāng)_是兩條信號(hào)線之間的耦合、信號(hào)線之間的互感和互容引起線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。PCB板層的參數(shù)、信號(hào)線間距、驅(qū)動(dòng)端和接收端的電氣特性及線端接方式對(duì)串?dāng)_都有一定的影響。

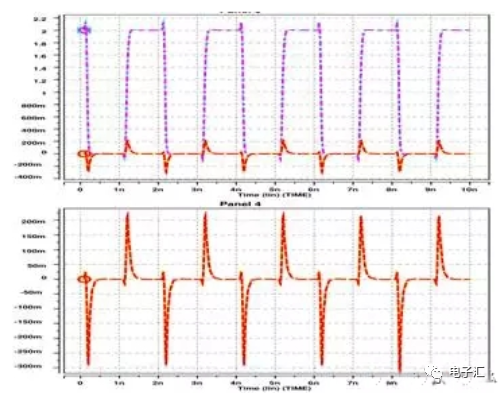

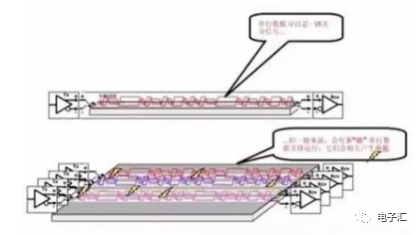

串?dāng)_是信號(hào)完整性中最基本的現(xiàn)象之一,在板上走線密度很高時(shí)串?dāng)_的影響尤其嚴(yán)重。我們知道,線性無(wú)緣系統(tǒng)滿足疊加定理,如果受害線上有信號(hào)的傳輸,串?dāng)_引起的噪聲會(huì)疊加在受害線上的信號(hào),從而使其信號(hào)產(chǎn)生畸變。

B、串?dāng)_是怎么引起的?

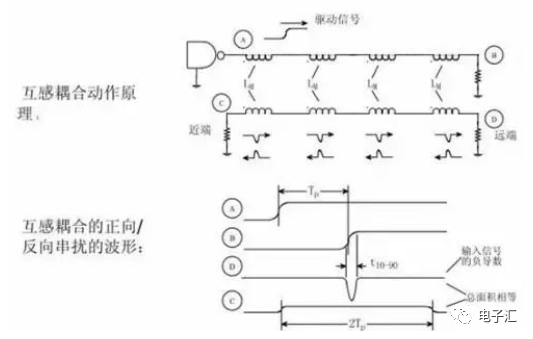

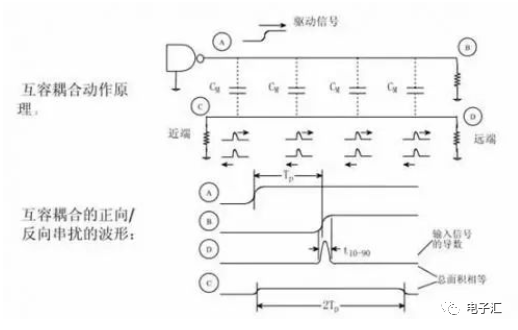

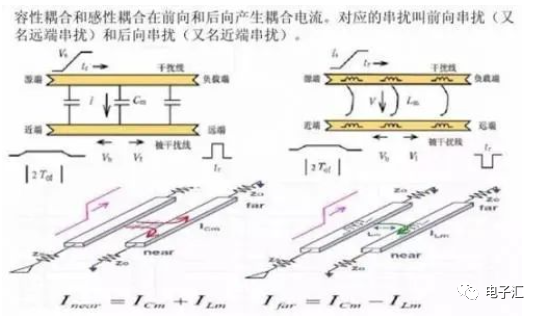

串?dāng)_是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。

串?dāng)_是指當(dāng)信號(hào)在傳輸線上傳播時(shí),因電磁耦合對(duì)相鄰的傳輸線產(chǎn)生不期望的電壓噪聲。

容性耦合是由于干擾源(Aggressor)上的電壓變化在被干擾對(duì)象(Victim)上引起感應(yīng)電流從而導(dǎo)致的電磁干擾;而感性耦合則是由于干擾源上的電流變化產(chǎn)生的磁場(chǎng)在被干擾對(duì)象上引起感應(yīng)電壓從而導(dǎo)致的電磁干擾。

因此,信號(hào)通過(guò)一導(dǎo)體時(shí)會(huì)在相鄰的導(dǎo)體上引起兩類不同的噪聲信號(hào):容性耦合信號(hào)和感性耦合信號(hào)。

感性耦合:

容性耦合:

C、降低串?dāng)_有哪些方法?

當(dāng)兩個(gè)網(wǎng)絡(luò)靠近時(shí),一個(gè)網(wǎng)絡(luò)的電流變化會(huì)引起另外一個(gè)網(wǎng)絡(luò)的電流變化,即產(chǎn)生串?dāng)_。也就是兩個(gè)網(wǎng)絡(luò)之間的電磁場(chǎng)耦合產(chǎn)生。串?dāng)_只在上升、下降沿電流變化時(shí)產(chǎn)生。

降低串?dāng)_的方法有:

1、選擇慢變化邊沿信號(hào)的器件。

2、選擇輸出擺幅和電流小的器件。

3、為了減少PCB上的線間耦合,可以采取:

(1)加大電源地層與信號(hào)層間距;

(2)提高相鄰信號(hào)層間距;

(3)減少并行走線長(zhǎng)度;

(4)增加線間距抑制;

(5)地線隔離

(6)在受害線上采用匹配技術(shù);

(7)關(guān)鍵信號(hào)線走STRIPLINE。

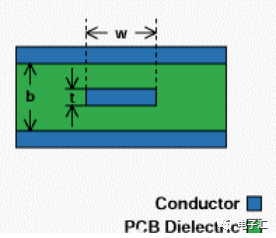

帶狀線:走在內(nèi)層(stripline/double stripline),埋在PCB內(nèi)部的帶狀走線,

如下圖所示:

藍(lán)色部分是導(dǎo)體,綠色部分是PCB的絕緣電介質(zhì),stripline是嵌在兩層導(dǎo)體之間的帶狀導(dǎo)線。

因?yàn)閟tripline是嵌在兩層導(dǎo)體之間,所以它的電場(chǎng)分布都在兩個(gè)包它的導(dǎo)體(平面)之間,不會(huì)輻射出去能量,也不會(huì)受到外部的輻射干擾。但是由于它的周圍全是電介質(zhì)(介電常數(shù)比1大),所以信號(hào)在stripline 中的傳輸速度比在microstrip line中慢!

-

pcb

+關(guān)注

關(guān)注

4354文章

23436瀏覽量

407097 -

射頻電路

+關(guān)注

關(guān)注

35文章

437瀏覽量

43856 -

電磁耦合

+關(guān)注

關(guān)注

2文章

30瀏覽量

13474 -

串?dāng)_

+關(guān)注

關(guān)注

4文章

189瀏覽量

27343

原文標(biāo)題:了解信號(hào)的串?dāng)_

文章出處:【微信號(hào):電子匯,微信公眾號(hào):電子匯】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

高速數(shù)字電路設(shè)計(jì)串擾問(wèn)題產(chǎn)生的機(jī)理原因

消除串擾的方法

PCB設(shè)計(jì)中避免串擾的方法

在設(shè)計(jì)fpga的pcb時(shí)可以減少串擾的方法有哪些呢?

防止串擾的方法不止3W規(guī)則

解決串?dāng)_的設(shè)計(jì)方法

解決串?dāng)_的設(shè)計(jì)方法

評(píng)論