第三章 CXL事務層

3.1 CXL.io

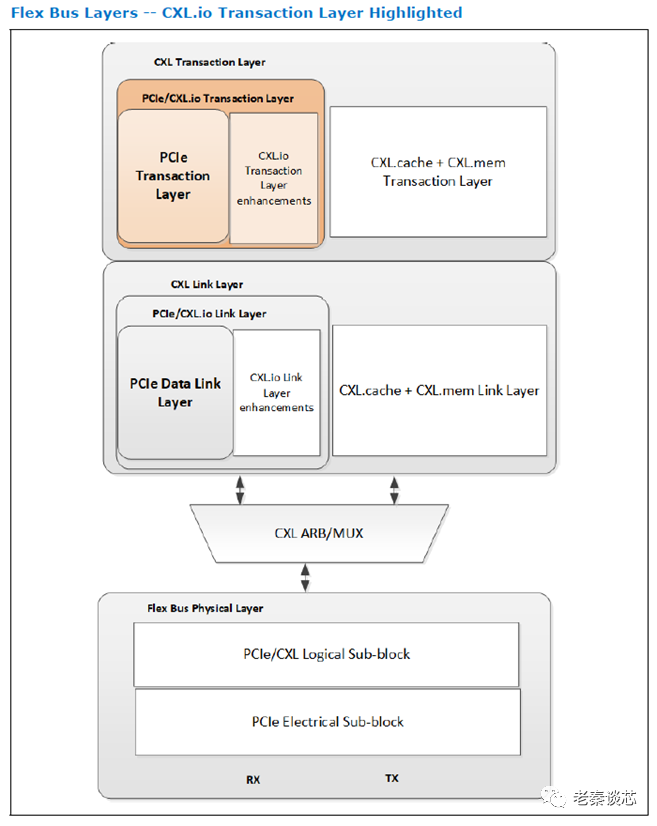

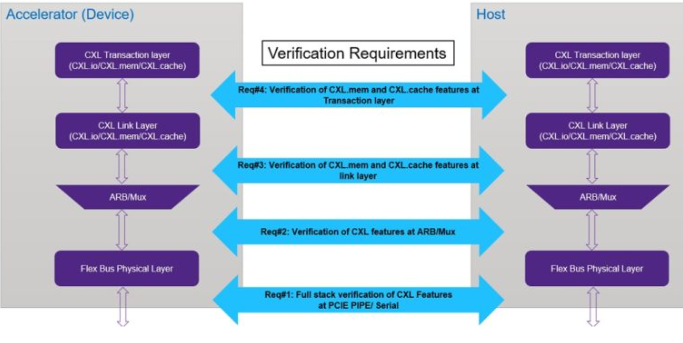

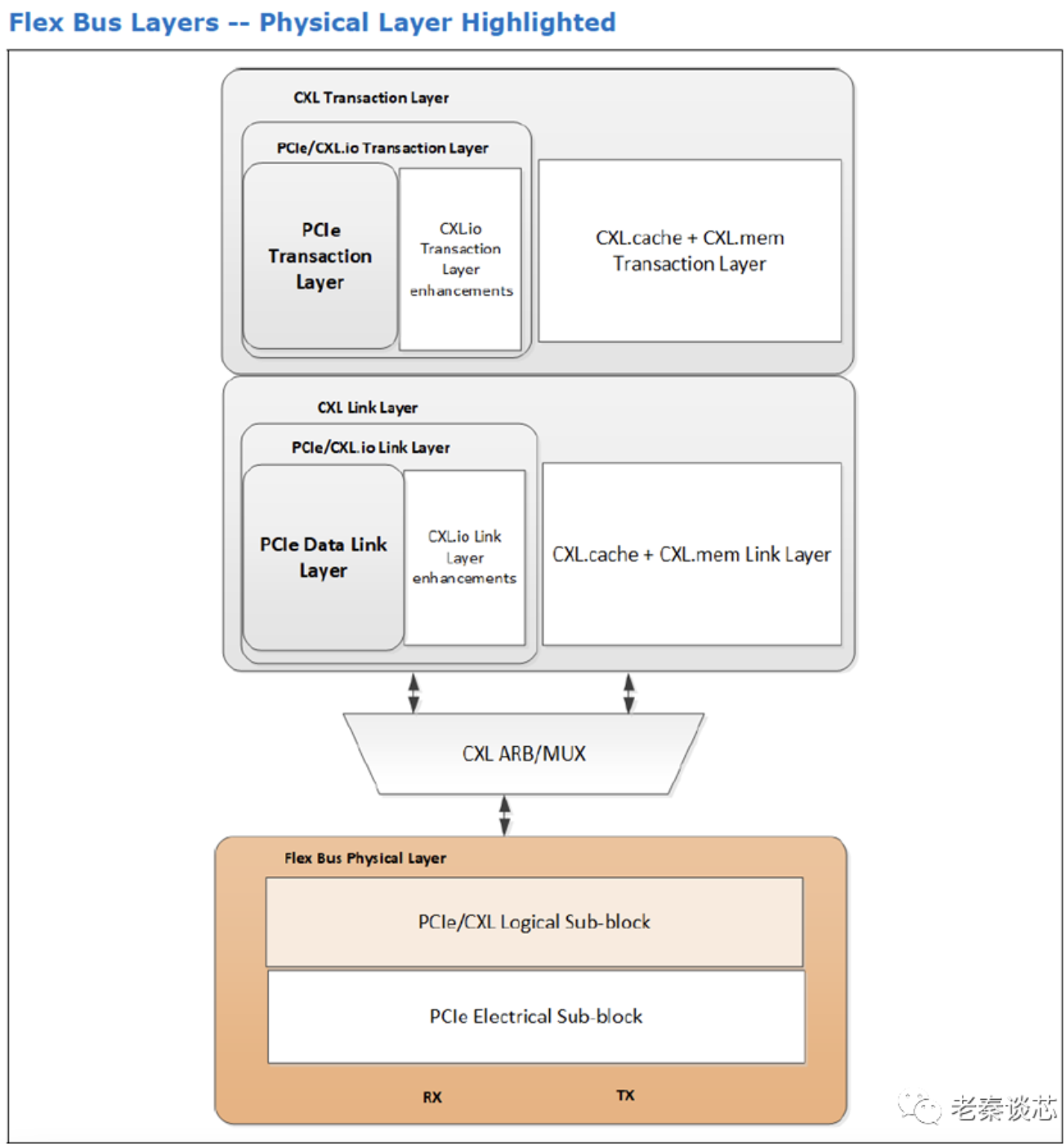

CXL.io為IO設備提供非一致性的load/strore接口。事務類型、事務數據包格式、信用流量控制、虛擬通道管理、事務順序的規則等遵循PCIe協議。CXL.io的事務層如下圖中的黃色部分所示。

3.1.1 CXL.io端點(Endpoint)

CXL設備需要支持在CXL 1.1和CXL 2.0模式下運行。當鏈路配置為在CXL 1.1模式下運行時,CXL.io端點必須作為PCIe RCiEP;而當配置為在CXL 2.0模式下運行時,必須作為PCI Express端點。

RCiEP是Root Complex Integrated Endpoints的縮寫,PCIe端點的一種。

3.1.2 CXL電源管理VDM(Vendor Defined Message)格式

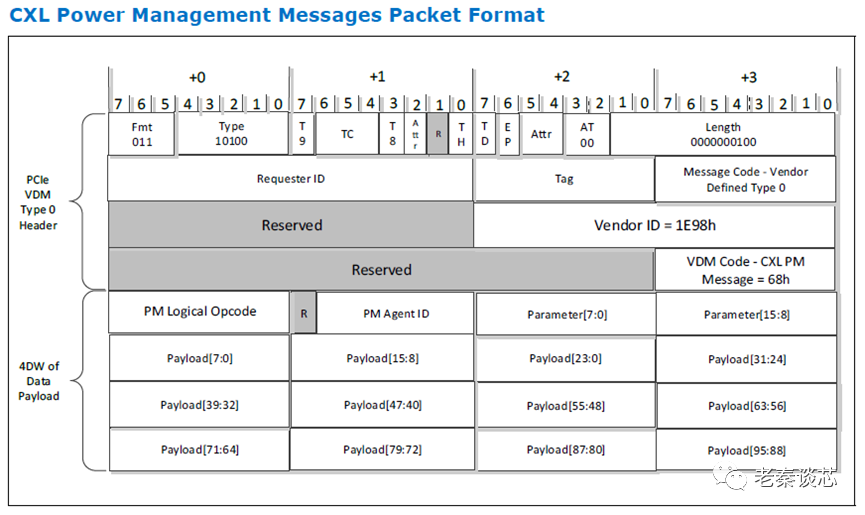

CXL電源管理消息使用PCIe的VDM Type 0,帶有4DW的負載數據,包括PMREQ,PMRSP和PMGO消息。

CXL電源管理VDM的格式如下:

如果接收方CXL組件接收到“有毒”的電源管理VDM,則應丟棄此類消息。由于接收方在接收到此類VDM后能夠繼續正常運行,因此應將此事件視為非致命性錯誤(non-fatal)。如果接收方的電源管理單元(PMU)不理解電源管理VDM數據負載的內容,則應無聲地丟棄該消息,并且不發出無法糾正錯誤(uncorrectableerror)的信號。

數據負載的字段定義比較多,就不貼圖了。

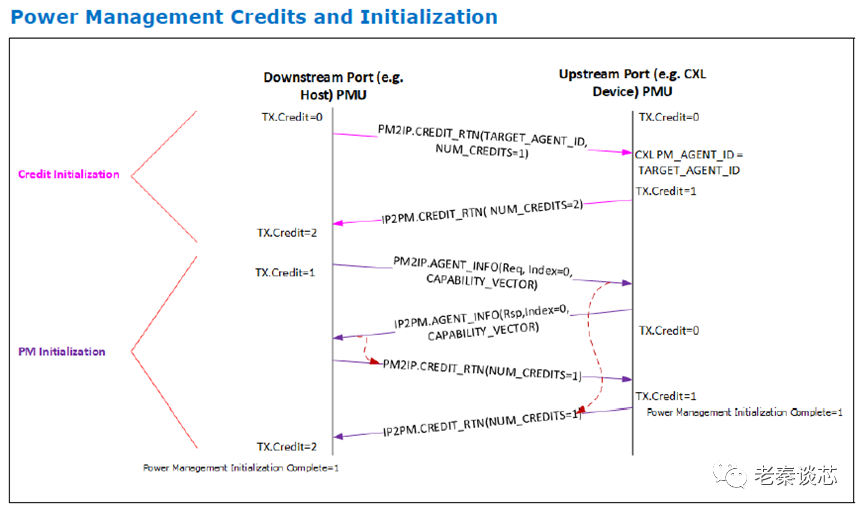

電源管理信用和初始化過程是本地鏈接。設備和主機之間通過CXL.io通道發送的消息類型主要涉及兩種,分別是CREDIT_RTN和AGENT_INFO,其中PM2IP是主機發給設備的電源管理消息,而IP2PM是設備發給主機的電源管理消息。至于“信用”機制就不解釋了,在前面講CCIX的時候已經介紹過了。

所謂的上游端口(Upstream Port)指的是設備的端口;而下游端口(Downstream Port)是主機端口。CXL上游端口PMU必須能夠接收和處理CREDIT_RTN消息,而不依賴于任何其它PM2IP消息。此外,CREDIT_RTN消息不使用信用。CREDIT_RTN消息用于初始化和更新每側的TX信用,以便可以適當地管理流量控制。在PM初始化期間的第一條CREDIT_RTN消息,通過NUM_CREDITS字段發送的信用表示CREDIT_RTN的發起方可以從另一端接收的信用相關PM消息的數量。在后續CREDIT_RTN消息期間,NUM_CREDITS字段表示自上一條CREDIT_RTN消息以來在同一方向釋放的PM信用數。下游端口PMU還使用第一條CREDIT_RTN消息為上游端口PMU分配PM_AGENT_ID。此ID通過CREDIT_RTN消息中的TARGET_AGENT_ID字段進行通信。在啟動任何IP2PM消息之前,上游端口PMU必須等待來自下游端口PMU的CREDIT_RTN消息

參考下圖,第一條消息,PM2IP.CREDIT_RTN(Target_Agent_ID,Num_Credits=1) ,這個消息里面包含了2個內容,一個是Target_Agent_ID,另一個是主機給了設備1個信用值。之后,設備也給主機發送了一個消息IP2PM. CREDIT_RTN(Num_Credits=2),授權了主機2個信用值。在初始化的時候,設備必須先等待接受來自主機的CREDIT_RTN消息,而不能先向主機發送消息。

上游端口PMU必須遵循的規則:

在啟動任何IP2PM消息之前,上游端口PMU必須等待接收PM2IP.CREDIT_RTN消息。

上游端口PMU必須從下游端口PMU接收到的第一條PM2IP消息中提取TARGET_AGENT_ID字段,并將其用作未來消息中的PM_AGENT_ID。

上游端口PMU必須實現足夠的資源來接收和處理任何CREDIT_RTN消息,而不依賴于任何其他PM2IP或IP2PM消息或其他消息類。

上游端口PMU必須實現至少一個信用,以接收PM2IP消息。

上游端口PMU必須盡快向下游端口PMU返回信用,以防止通過CXL鏈路阻塞電源管理消息通信。

建議上游端口PMU占用信用額度不得超過10us。

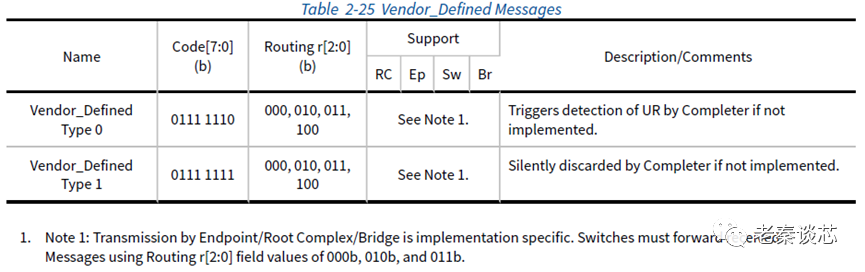

插播一句,是不是看的暈暈的?這里簡單介紹一下供應商定義的消息(VDM),PCIe協議里是這么說的“TheVendor Defined Messages allow expansion of PCI Express messaging capabilities,either as a general extension to the PCI Express Specification or avendor-specific extension”。

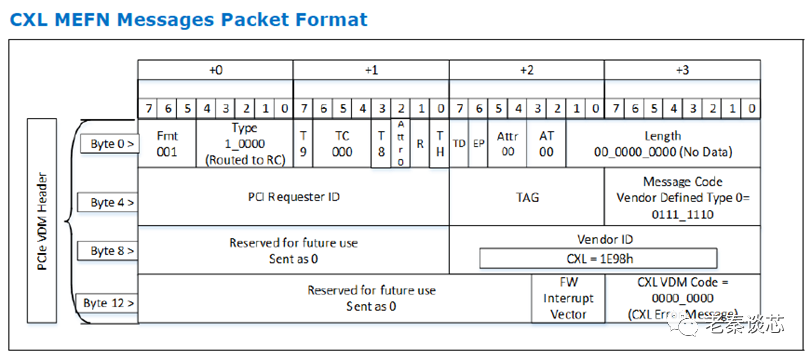

3.1.3 CXL錯誤VDM格式

CXL錯誤消息使用PCIe的VDM Type 0,沒有負載數據,格式如下。

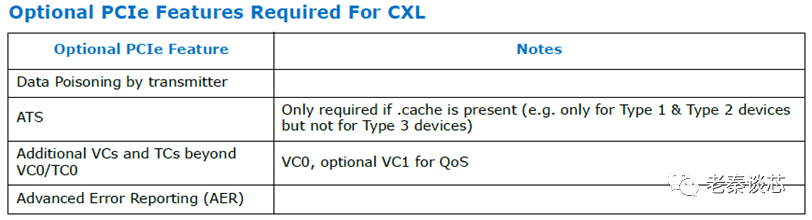

3.1.4 CXL所需的可選PCIe功能

3.1.5 錯誤傳播

設備檢測到的CXL.cache和CXL.mem錯誤通過CXL.io通信流傳播到上游端口。這些錯誤在PCIe AER寄存器中記錄為可糾正(Correctable)和不可糾正(Uncorrectable)的內部錯誤。

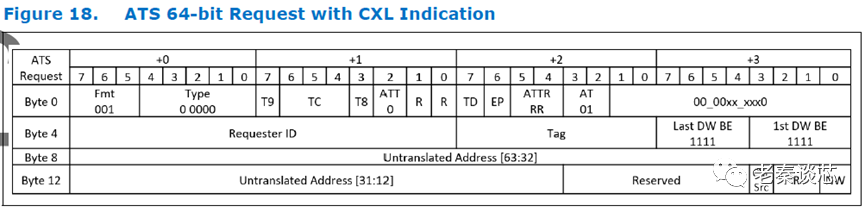

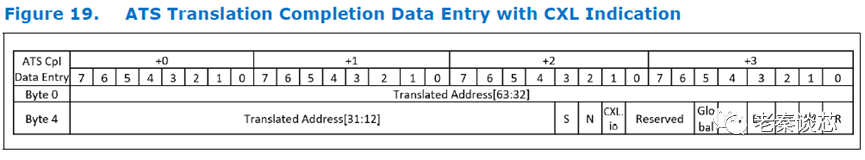

3.1.6 ATS上的存儲器類型指示

對某些內存區域的請求只能在CXL.io上發出,而不能在CXL.cache上發出。由主機決定這些內存區域是什么。例如,在x86系統上,主機可以選擇僅通過CXL.io限制對不可緩存(Uncacheable)類型內存的訪問。主機通過ATS完成(ATS Completion)向設備來指示這些區域。

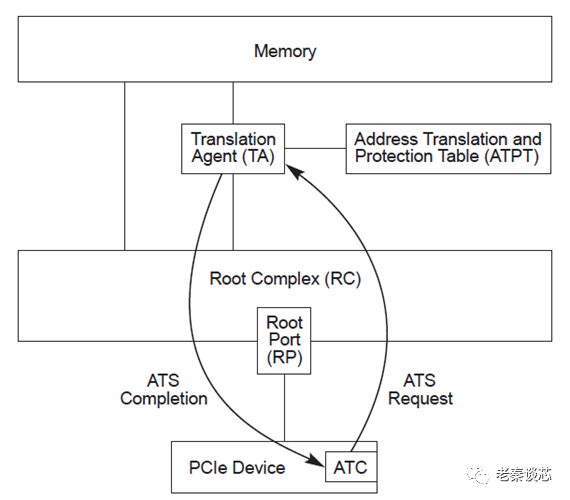

插播一句,ATS是Address Translation Services的縮寫。PCIe協議里面有一整章講ATS。為節省CPU資源,I/O Function常采用DMA方式訪問內存。一般I/O Function看到的物理地址空間與CPU一樣。但有時候,I/O Function看到的地址空間不是真實的物理地址,需要RC將DMA請求進行處理,通過一次地址轉換才能將訪問到真實的物理地址。這種地址轉換機制有利于訪問權限檢查。

一般PCIe設備在本地實現一個地址緩存(Address Translation Cache,ATC),類似CPU中的TLB。Function發送存儲器讀寫請求前,先在本地的ATC中查找是否有該地址的條目。如果在ATC中查找成功,直接采用轉換后地址進行訪問。如果在ATC中沒有找到該地址的條碼,則給TA(TranslationAgent)發送該地址的地址轉換請求。在ARM體系中,TA的功能由SMMU(System Memory Management Unit)承擔,此外SMMU還要顯式的負責同步TLB和與它相連的分布ATC中的數據一致性。關于SMMU,之前的文章介紹過。

3.1.7 可延遲寫

CXL規范中定義的可延遲寫入僅在CXL1.1模式下運行時適用。在CXL 2.0模式下操作時,請參閱PCIe規范以了解此功能。

審核編輯:湯梓紅

-

電源管理

+關注

關注

117文章

6414瀏覽量

145898 -

接口

+關注

關注

33文章

8968瀏覽量

153361 -

PCIe

+關注

關注

16文章

1329瀏覽量

84836

原文標題:技術分享 | CXL學習(三)

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

詳解Spring事務管理

CXL事務層的結構是由哪些部分組成的

CXL事務層學習相關資料推薦

CXL內存協議介紹

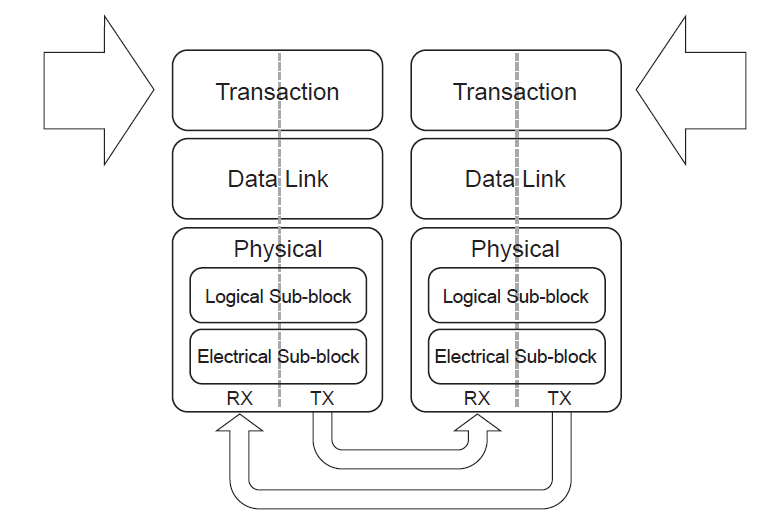

一個簡單地的例子來回顧PCIe總線的結構、事務層、數據鏈路層和物理層

PCIe 6.0入門之事務層

揭開CXL的神秘面紗:概述

關于CXL的功能與特性詳解

CXL事務層詳解

CXL事務層詳解

評論