0 引言

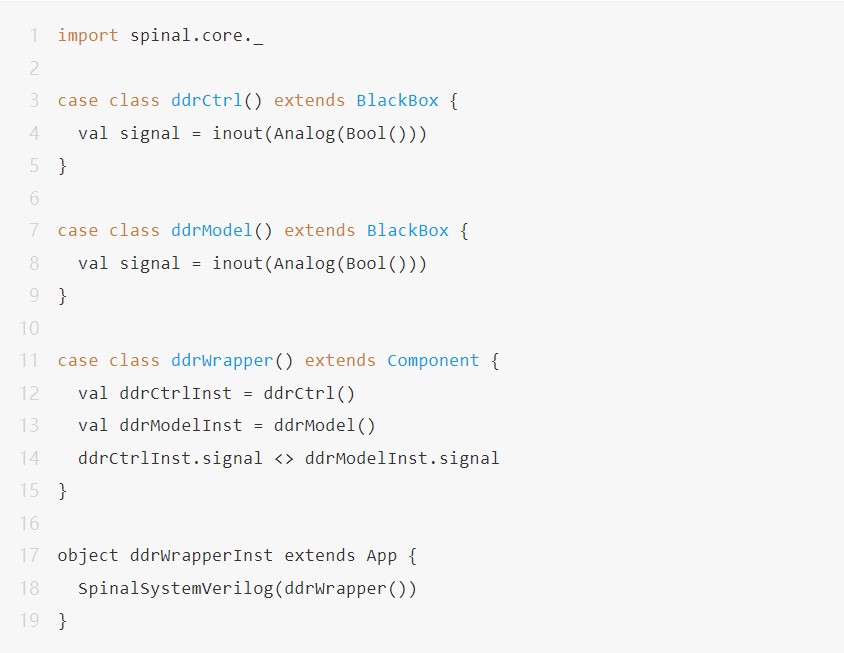

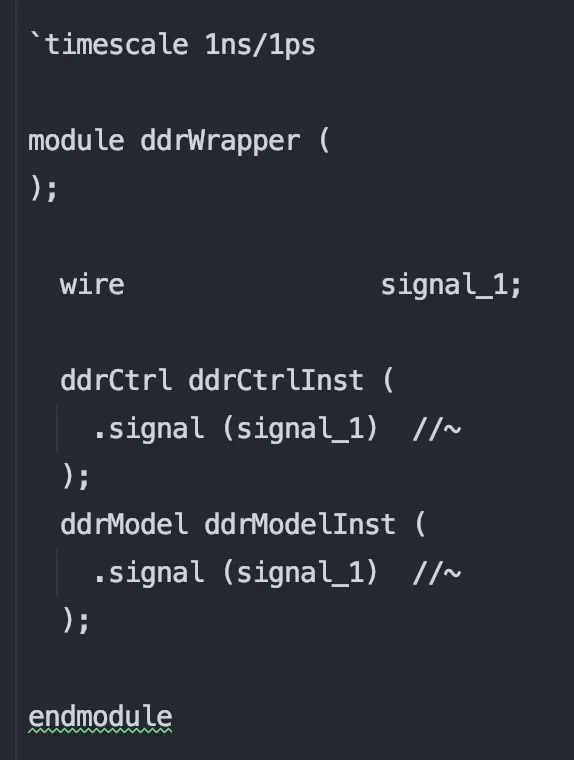

在SpinalHDL 1.7.0版本里,在仿真方面開始支持了VCS,這解決了在FPGA設(shè)計(jì)里采用Verilator時(shí)無法仿真廠商IP的問題。故此,前段時(shí)間嘗試了把集成FPGA廠商DDR IP的測(cè)試。不曾想?yún)s遇到了一個(gè)從未遇到的錯(cuò)誤。在DDR仿真里一般由控制器IP以及廠商的Memory Model組成,我將其各自封裝成了一個(gè)Blackbox,而在集成的時(shí)候確過不去了。為簡(jiǎn)單起見,這里采用下面的代碼示例:

?

?

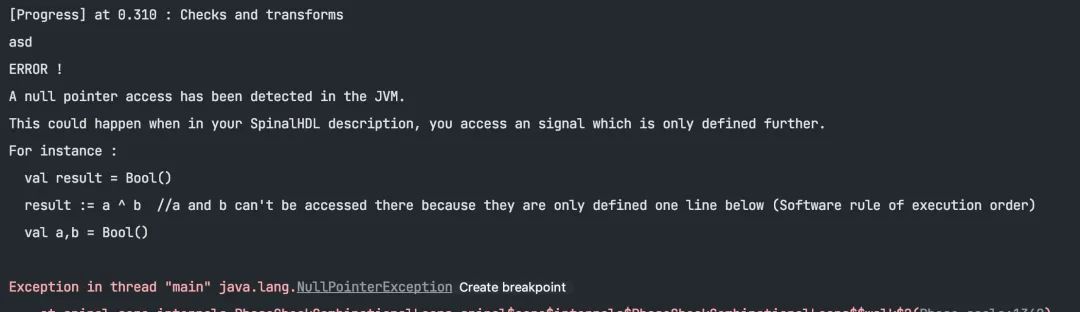

看起來似乎沒啥毛病對(duì)吧,而且在之前寫Verilog時(shí)候inout端口也是這么連接的。然而在運(yùn)行的時(shí)候卻報(bào)了下面的錯(cuò)誤:

這錯(cuò)誤類型我熟,但貌似明顯我并沒有犯這個(gè)錯(cuò)誤啊…… 》解決之道

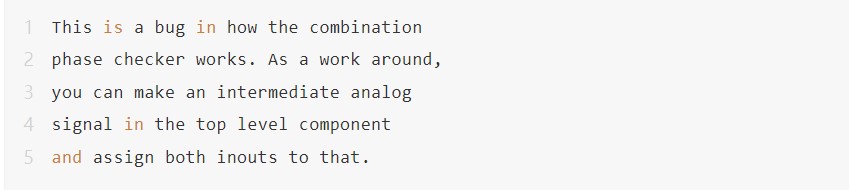

首先需要說明的是,這種使用場(chǎng)景也僅在仿真的時(shí)候會(huì)使用到,而真實(shí)的設(shè)計(jì)場(chǎng)景是不會(huì)有這么用的。但上面這個(gè)場(chǎng)景確實(shí)存在。在git上大神給出了下面的答復(fù):

??

??

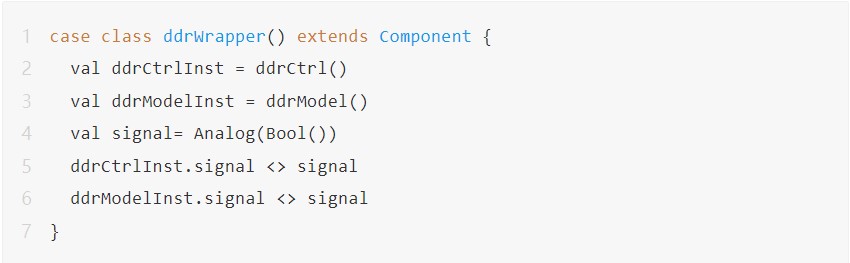

針對(duì)這種場(chǎng)景,這里給出一個(gè)解決方案,ddrWrapper重寫如下:

修改后即可達(dá)成我們想要的效果:

審核編輯:劉清

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

27174 -

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66448 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9858

原文標(biāo)題:踩坑系列——inout連接不上

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Verilog inout 雙向口使用和仿真

Verilog inout 雙向口使用和仿真-轉(zhuǎn)載

inout testbench寫法總結(jié)

是否可以將一個(gè)inout端口直接連接到另一個(gè)inout端口?

為什么CC2540建立連接不上呢?

INOUT信號(hào)問題

VS-RK3399安卓主板adb 鏈接不上問題如何解決?

Inout雙向端口信號(hào)處理方法

簡(jiǎn)談FPGA/Verilog中inout端口使用方法

pppoe什么意思_pppoe連接不上怎么辦

wifi有信號(hào)卻連接不上是為什么

為什么Xshell連接不上服務(wù)器?

inout連接不上如何解決呢

inout連接不上如何解決呢

評(píng)論