Verilog語言是一種硬件描述語言(HDL),用于描述數(shù)字邏輯電路和系統(tǒng)。它是一種非常強(qiáng)大且廣泛使用的語言,在數(shù)字電路設(shè)計(jì)中扮演著重要的角色。其中,inout是Verilog中的一種信號(hào)類型,本文將詳細(xì)討論inout的用法和仿真。

首先,我們來了解一下inout的含義。inout是一種雙向信號(hào)類型,即可以作為輸入信號(hào)也可以作為輸出信號(hào)。它類似于雙向數(shù)據(jù)線,可以實(shí)現(xiàn)數(shù)據(jù)的雙向傳輸。在硬件設(shè)計(jì)中,inout可以用于與外部設(shè)備進(jìn)行通信,如鍵盤、鼠標(biāo)、顯示屏等。

在Verilog中,使用inout類型定義信號(hào)時(shí),需要在信號(hào)聲明時(shí)添加關(guān)鍵字inout,例如:

module myModule (

inout [7:0] data

);

上述代碼定義了一個(gè)名為data的8位雙向信號(hào)。接下來,我們將討論inout的用法和一些注意事項(xiàng)。

首先,需要注意的是,inout信號(hào)必須通過tri型的物理連接來與外部設(shè)備進(jìn)行連接。這是因?yàn)?code>inout信號(hào)既可以作為輸入也可以作為輸出,需要與外部設(shè)備進(jìn)行雙向通信。一個(gè)常見的應(yīng)用是使用三態(tài)緩沖器將inout信號(hào)與外部設(shè)備連接起來。三態(tài)緩沖器允許在特定情況下將信號(hào)的輸出變?yōu)楦咦钁B(tài),以避免信號(hào)沖突。

其次,inout信號(hào)在模塊的端口列表中聲明,并且可以在模塊的內(nèi)部和外部進(jìn)行操作。在模塊內(nèi)部,可以像普通信號(hào)一樣使用inout信號(hào),進(jìn)行賦值、邏輯運(yùn)算等操作。在模塊外部,可以通過賦值操作來改變inout信號(hào)的值。需要注意的是,在模塊的內(nèi)部對(duì)inout信號(hào)進(jìn)行的任何操作都會(huì)在模塊外部可見。因此,在設(shè)計(jì)中需要注意處理inout信號(hào)的時(shí)序和沖突問題。

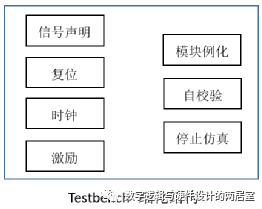

此外,inout信號(hào)可以像其他信號(hào)類型一樣在仿真中使用。在Verilog仿真環(huán)境中,可以通過對(duì)inout信號(hào)的賦值操作來模擬外部設(shè)備對(duì)信號(hào)的輸入。仿真時(shí),可以將inout信號(hào)連接到仿真模型的輸入端口,并使用時(shí)鐘周期來模擬輸入輸出的變化。需要注意的是,由于inout信號(hào)是雙向的,必須正確模擬和處理輸入和輸出的時(shí)序關(guān)系。

為了更好地理解inout信號(hào)的用法和仿真,下面舉一個(gè)簡單的示例。假設(shè)我們需要設(shè)計(jì)一個(gè)模塊,該模塊具有一個(gè)8位的inout信號(hào),用于從外部設(shè)備讀取數(shù)據(jù)并將其傳遞給內(nèi)部邏輯電路。同時(shí),該模塊還具有一個(gè)控制信號(hào)en,用于控制inout信號(hào)的輸入和輸出。

module inout_module (

input [7:0] data_in,

input en,

inout [7:0] data_io

);

assign data_io = (en) ? data_in : 8'bZ;

endmodule

在上述示例中,data_in是輸入的數(shù)據(jù)信號(hào),en是控制信號(hào),data_io是雙向信號(hào)。通過assign語句,根據(jù)en的狀態(tài)來控制data_io輸入或輸出數(shù)據(jù)。當(dāng)en為1時(shí),data_in的值被賦值給data_io;當(dāng)en為0時(shí),將data_io的值設(shè)置為高阻態(tài),即不對(duì)外輸出數(shù)據(jù)。這種寫法模擬了三態(tài)緩沖器的操作。

仿真時(shí),可以使用Verilog仿真工具,如ModelSim或VCS,來執(zhí)行仿真。在仿真測試中,可以通過對(duì)data_in和en輸入信號(hào)的賦值操作,來模擬外部設(shè)備對(duì)信號(hào)的輸入。同時(shí),可以觀察data_io輸出信號(hào)的變化,以驗(yàn)證模塊內(nèi)部的邏輯是否正確。

綜上所述,本文詳細(xì)討論了Verilog中inout信號(hào)的用法和仿真。通過inout信號(hào),可以實(shí)現(xiàn)雙向數(shù)據(jù)傳輸,與外部設(shè)備進(jìn)行通信。同時(shí),需要正確處理inout信號(hào)的時(shí)序和沖突問題,并通過仿真測試驗(yàn)證設(shè)計(jì)的正確性。這種信號(hào)類型在硬件設(shè)計(jì)中扮演著重要的角色,對(duì)于深入理解Verilog語言和數(shù)字電路設(shè)計(jì)有著重要意義。

-

硬件

+關(guān)注

關(guān)注

11文章

3464瀏覽量

67257 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111923 -

數(shù)字邏輯電路

+關(guān)注

關(guān)注

0文章

106瀏覽量

16052 -

Inout

+關(guān)注

關(guān)注

0文章

4瀏覽量

6234

發(fā)布評(píng)論請(qǐng)先 登錄

Verilog inout 雙向口使用和仿真

Verilog inout 雙向口使用和仿真-轉(zhuǎn)載

inout testbench寫法總結(jié)

verilog inout的 用法

【verilog每日一練】“inout” 雙向端口類型的使用

簡談FPGA/Verilog中inout端口使用方法

如何使用Icarus Verilog+GTKWave來進(jìn)行verilog文件的編譯和仿真

Verilog系統(tǒng)函數(shù)和邊沿檢測

verilog仿真工具編譯

Verilog仿真激勵(lì)舉例

verilog inout用法與仿真

verilog inout用法與仿真

評(píng)論