在學(xué)習(xí) “跨時鐘域的亞穩(wěn)態(tài)的應(yīng)對措施” 時,常會看到有三種解決方案:

單bit信號,用:打兩拍

多bit信號,用:異步FIFO

多bit信號,用:格雷碼

多bit信號,用:握手

記是記住了,但我有好幾個疑惑一直沒理解,網(wǎng)上沖浪卻搜不到答案、還是非常困惑…

以下是我的疑惑:

為什么用“打兩拍”來應(yīng)對跨時鐘域的亞穩(wěn)態(tài),“打一拍” 不行嗎?

為什么說,用“打兩拍”只是降低了亞穩(wěn)態(tài)的概率,但也有可能導(dǎo)致亞穩(wěn)態(tài)的傳遞呢?

若后接了個FF,隨著posedge clk的出現(xiàn),觸發(fā)器不應(yīng)該直接就采到0或1了嗎,為啥亞穩(wěn)態(tài)還有一定概率傳遞呢?

假設(shè)是DFF(D觸發(fā)器),其亞穩(wěn)態(tài)穩(wěn)定后的值,會恢復(fù)為正確的預(yù)期輸出值嗎?還是就算穩(wěn)定了也是無效輸出?

即使 “打兩拍”能阻止“亞穩(wěn)態(tài)的傳遞”,但亞穩(wěn)態(tài)導(dǎo)致后續(xù)FF sample到的值依然不一定是符合預(yù)期的值,那 “錯誤的值” 難道不依然會向后傳遞,從而造成錯誤的后果嗎?

多bit的跨時鐘域情況用 異步FIFO處理,好理解;格雷碼有啥用嘞?

格雷碼可以讓相鄰二進(jìn)制數(shù)變化只改變1位,但在多bit的data傳輸過程中,data value不都是隨機(jī)變化么,格雷碼有啥用嘞?

主要是前面關(guān)于打兩拍的疑惑,網(wǎng)上沖浪找不到解答的帖子。

網(wǎng)上只有兩個核心的回答,但對我這樣的數(shù)電小白,完全是沒有回答到我個人解惑的點子上,但解惑后再看,會有新的收獲:

打兩拍的目的:第一拍是異步信號轉(zhuǎn)同步,第二拍是防止亞穩(wěn)態(tài)的傳遞。

我聽了還是很迷。( ̄▽ ̄)"

打一拍和打兩拍和打三拍的區(qū)別:用觸發(fā)器進(jìn)入亞穩(wěn)態(tài)的平均故障時間間隔MTBF進(jìn)行計算,證明打拍數(shù)增加,產(chǎn)生亞穩(wěn)態(tài)的可能性遞減:打一拍直接用,很可能出現(xiàn)亞穩(wěn)態(tài)輸出;打兩拍再直接用,出現(xiàn)亞穩(wěn)態(tài)的概率是109年出現(xiàn)一次(具體計算參數(shù)見reference);打三拍再直接俄用,出現(xiàn)的概率更低,但是除非超高頻率不然沒必要。

可見reference:跨時鐘域同步,為什么兩級寄存器結(jié)構(gòu)能夠降低亞穩(wěn)態(tài)?—— 知乎 龔黎明(https://www.zhihu.com/question/43571892)

那我個人疑惑呢,最后在外網(wǎng) stack exchange 上解答了——這個老哥居然和我的疑問一毛一樣!實在是欣慰,久旱逢甘霖…( ̄▽ ̄)"

Stack Exchange上的回答:How does 2-ff synchronizer ensure proper synchonization?

(不知為什么用firefox不顯示問題圖片,用chrome才顯示圖片…)

于是,我打算用自己的話,記錄一下它的問題與回答,也回答我個人的疑惑~

概念補(bǔ)充

什么是亞穩(wěn)態(tài) metastable state?

首先要闡述一下亞穩(wěn)態(tài)的概念。

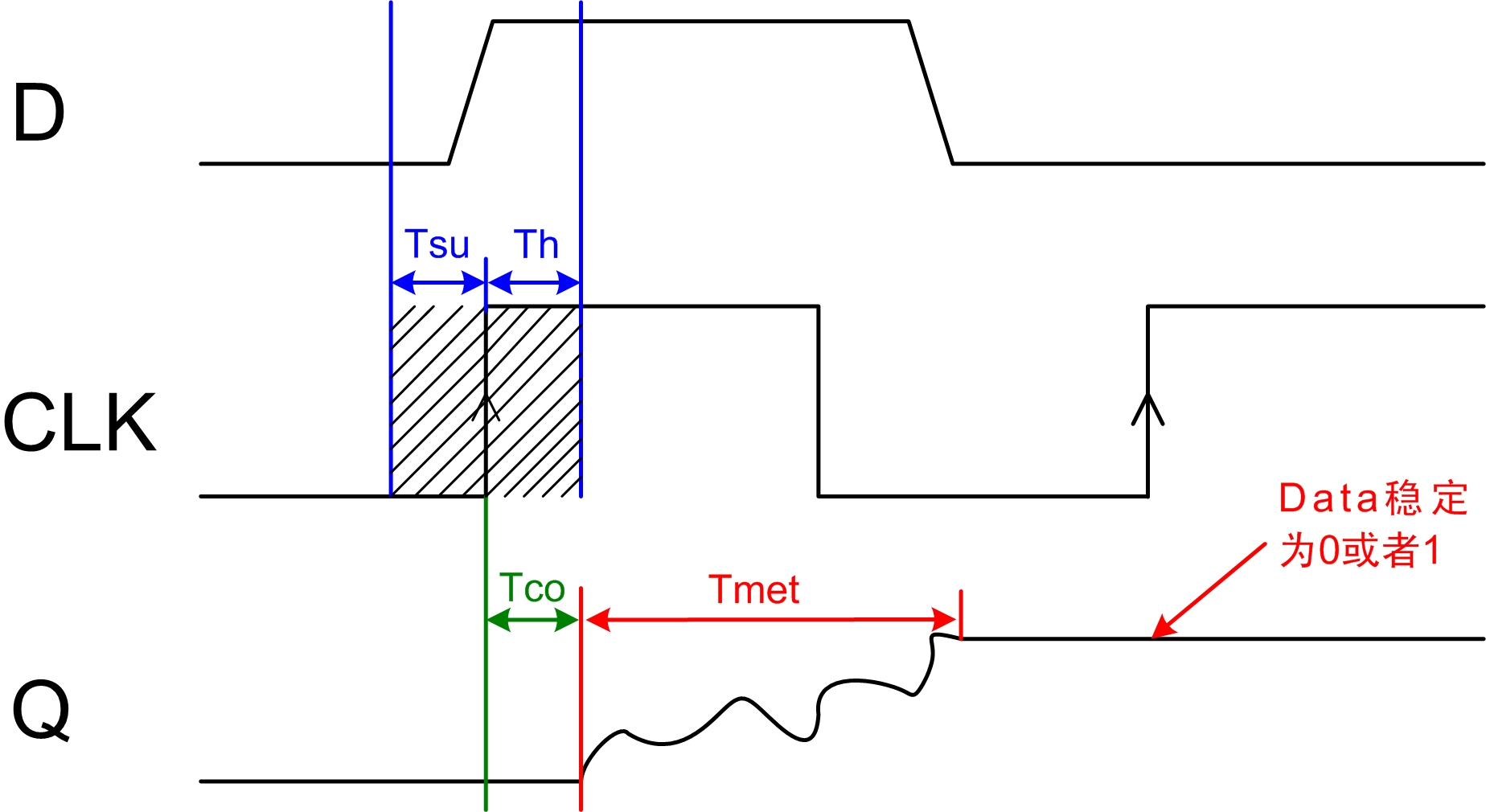

元器件在現(xiàn)實運(yùn)行時,觸發(fā)器輸出的邏輯0/1需要時間跳變,而不是瞬發(fā)的。因此,若未滿足此cell的建立時間、保持時間,其輸出值則為中間態(tài),那在logic上可能算成0也可能算成1很難講(波形顯示上可能是毛刺、振蕩、固定值等),這就是亞穩(wěn)態(tài)。

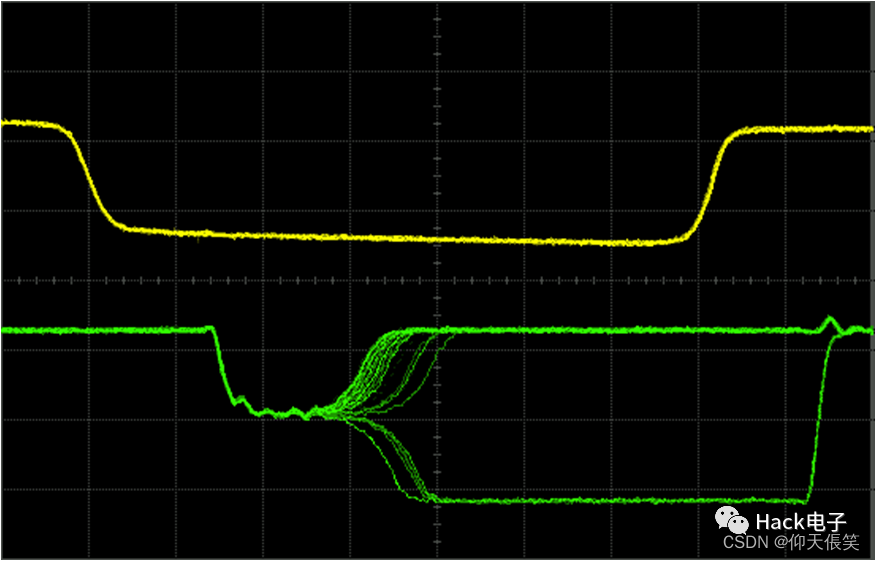

一般波形圖像上,1是高電平,0是低電平;但微觀的亞穩(wěn)態(tài)波形如下:

如圖所示:亞穩(wěn)態(tài)的輸出波形會卡在中間,過一段時間后,可能穩(wěn)定成1,也可能穩(wěn)定成0,但都和原預(yù)期值沒啥關(guān)系了,是無效的!

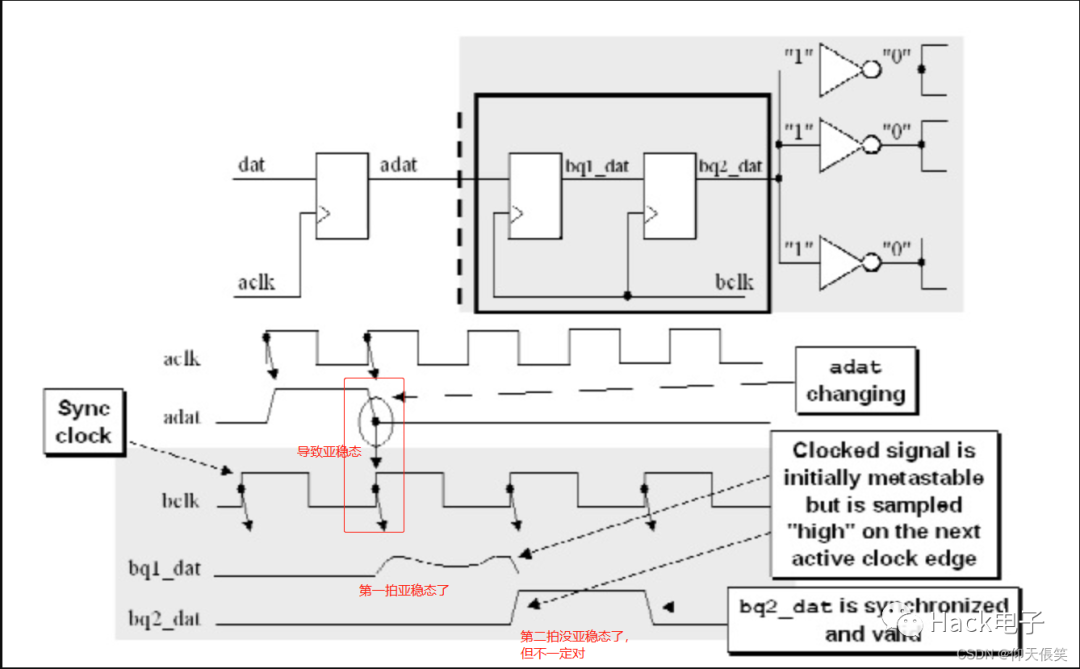

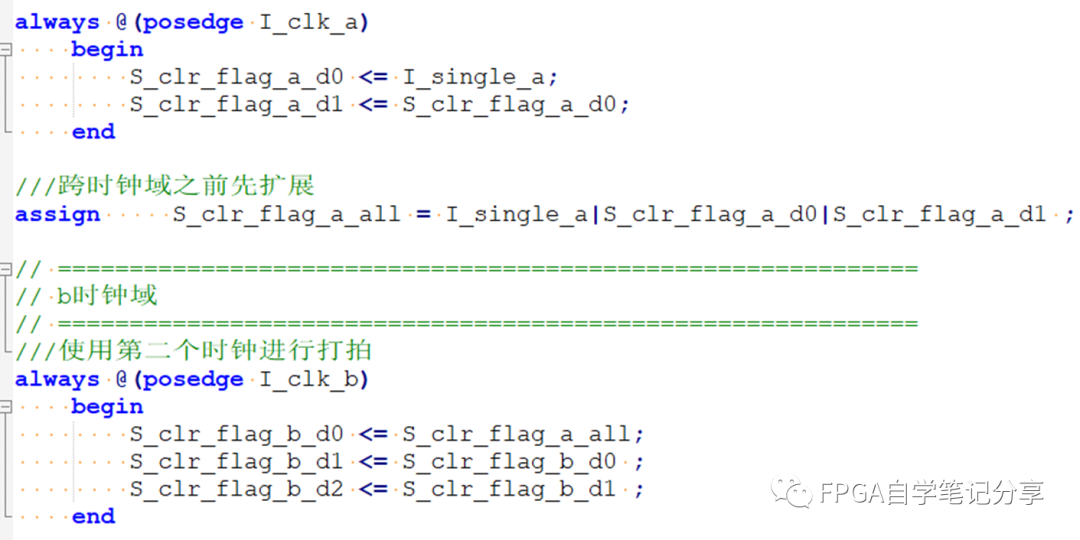

單bit信號,應(yīng)用“打兩拍”的電路結(jié)構(gòu)圖

這張圖,給出了兩個點:

“打兩拍”后可以直接接組合邏輯電路。

我之前以為后面必接時序電路,相當(dāng)于后面的電路也是觸發(fā)器,于是產(chǎn)生了:“把打兩拍改成打一拍,算上后面的時序電路,不也是相當(dāng)于打兩拍嗎” 這樣的愚蠢困惑…( ̄▽ ̄)"

下方的波形給了“打兩拍能大概率防止亞穩(wěn)態(tài)傳遞”的圖示:

由于異步data變的太突然,第一拍sample后出現(xiàn)亞穩(wěn)態(tài),第三拍sample后把亞穩(wěn)態(tài)堵住了,得到正常電平(但值不一定和原預(yù)期相同)。

解惑環(huán)節(jié)

綜上,可以解答我之前的3個疑惑了:

為什么用“打兩拍”來應(yīng)對跨時鐘域的亞穩(wěn)態(tài),“打一拍” 不行嗎?

如打兩拍的電路結(jié)構(gòu)圖所示:打一拍的話,若第一拍sample到亞穩(wěn)態(tài),則后續(xù)組合邏輯電路的輸入直接就是亞穩(wěn)態(tài)波形,肯定會把亞穩(wěn)態(tài)傳遞下去,就完犢子了。

為什么說,用“打兩拍”只是降低了亞穩(wěn)態(tài)的概率,但也有可能導(dǎo)致亞穩(wěn)態(tài)的傳遞呢?

如前面的兩張亞穩(wěn)態(tài)的波形所示,亞穩(wěn)態(tài)如果在1T內(nèi)穩(wěn)定成高電平或低電平了(概率80%),那第2拍就sample到正常的0或1;若亞穩(wěn)態(tài)1T最后還是中間態(tài),那第2拍還是可能出現(xiàn)亞穩(wěn)態(tài)的,但概率低。

亞穩(wěn)態(tài)穩(wěn)定需要多久,具體時間由工藝決定。

假設(shè)是DFF(D觸發(fā)器),其亞穩(wěn)態(tài)穩(wěn)定后的值,會恢復(fù)為正確的預(yù)期輸出值嗎?還是就算穩(wěn)定了也是無效輸出?

如前面的亞穩(wěn)態(tài)微觀波形所說:即使亞穩(wěn)態(tài)穩(wěn)定了,值也無效。

剩下倆疑惑,大頭講。見下文。

打兩拍的sample到錯誤數(shù)據(jù)怎么辦

sample亞穩(wěn)態(tài),結(jié)果可能多樣

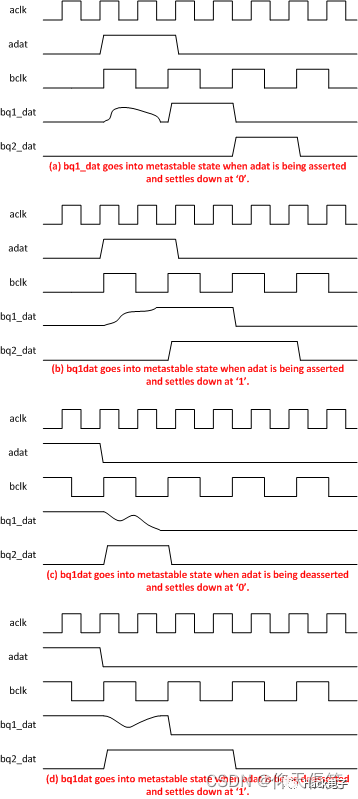

sample亞穩(wěn)態(tài),得到的結(jié)果可能取決于亞穩(wěn)態(tài)最后穩(wěn)定于什么狀態(tài),如下圖表示出各種sample的可能:

如圖所示,adat是實際的異步data、bq1_dat是兩級觸發(fā)器中的第一個寄存器sample的數(shù)據(jù)、bq2_dat是第二個寄存器sanple到的數(shù)據(jù),bclk是同步時鐘。

則:

a)中,異步data持續(xù)2T;FF1 sample到亞穩(wěn)態(tài)時,F(xiàn)F2在下一cycle 對亞穩(wěn)態(tài)的sample是0;但最終sample到了正確的data值。

b)中,異步data持續(xù)2T;FF1 sample到亞穩(wěn)態(tài)時,F(xiàn)F2在下一cycle 對亞穩(wěn)態(tài)的sample是1;但最終sample到了正確的data值。

c)中,異步data馬上結(jié)束,等價于只持續(xù)1T(相當(dāng)于沒sample到就錯過了);FF1 sample到亞穩(wěn)態(tài)時,F(xiàn)F2在下一cycle 對亞穩(wěn)態(tài)的sample是1;運(yùn)氣好,最終sample到了正確的data值。

d)中,異步data馬上結(jié)束,等價于只持續(xù)1T;FF1 sample到亞穩(wěn)態(tài)時,F(xiàn)F2在下一cycle 對亞穩(wěn)態(tài)的sample是0;相當(dāng)于最終錯過了data值,沒sample到…

那咋辦,豈不是說明“打兩拍”的方法不行???

答案:

因為 “打兩拍” 的目的,是為了在單bit傳輸時,盡可能的防止亞穩(wěn)態(tài)的傳遞,至于這個sample的正確性,本來就不是重點。這種“sample的正確性如何保證”得根據(jù)信號的具體類型、目的、應(yīng)用場景,來進(jìn)行具體的討論。

Trigger Signals:一個脈沖信號,用來開機(jī)、啟動什么的。它沒什么數(shù)據(jù)信息量,早一個clk、晚一個clk都o(jì)k,反正能起作用就行。那上面這個問題就無所謂了。唯一要保證的是,原始異步脈沖信號至少保持2T!(保證打兩拍后,能sample到有效信號)

Control Buses:因為有多bit數(shù)據(jù)需要進(jìn)行同步,關(guān)系比較復(fù)雜。那就不能用 “打兩拍” 的方法,得用 “握手機(jī)制“。

Data Buses:這種情況,非常在乎上面提到的正確性問題。所以就 更不應(yīng)該用 ”打兩拍“方法,得用 異步FIFO的好吧… 在異步FIFO中的指針使用格雷碼,可以降低指針在跳變時出現(xiàn)的亞穩(wěn)態(tài)風(fēng)險、冒險現(xiàn)象。也就說,格雷碼和異步FIFO是結(jié)合使用的… ( ̄▽ ̄)"

總結(jié)

當(dāng)你在乎跨時鐘域 “用打兩拍解決亞穩(wěn)態(tài),導(dǎo)致后續(xù)sample可能未sample到正確結(jié)果” 的case,那就不該用 “打兩拍” 的方案,可以考慮異步FIFO和握手機(jī)制!而格雷碼,和異步FIFO是聯(lián)合使用的。

“打兩拍”的方法,若應(yīng)用于“從快速時鐘域同步到慢速時鐘域”,數(shù)據(jù)得多保持幾T,不然會漏采數(shù)據(jù)。

-

元器件

+關(guān)注

關(guān)注

113文章

4811瀏覽量

94465 -

亞穩(wěn)態(tài)

+關(guān)注

關(guān)注

0文章

47瀏覽量

13483 -

時鐘域

+關(guān)注

關(guān)注

0文章

53瀏覽量

9735

發(fā)布評論請先 登錄

FPGA中復(fù)位電路的亞穩(wěn)態(tài)技術(shù)詳解

跨時鐘域的解決方案

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

FPGA的亞穩(wěn)態(tài)現(xiàn)象是什么?

在FPGA復(fù)位電路中產(chǎn)生亞穩(wěn)態(tài)的原因

FPGA--中復(fù)位電路產(chǎn)生亞穩(wěn)態(tài)的原因

今日說“法”:讓FPGA設(shè)計中的亞穩(wěn)態(tài)“無處可逃”

如何利用FPGA設(shè)計一個跨時鐘域的同步策略?

如何解決異步FIFO跨時鐘域亞穩(wěn)態(tài)問題?

時序問題常見的跨時鐘域亞穩(wěn)態(tài)問題

跨時鐘域的亞穩(wěn)態(tài)的應(yīng)對措施三種解決方案

FPGA設(shè)計中的亞穩(wěn)態(tài)解析

如何處理跨時鐘域這些基礎(chǔ)問題

跨時鐘域的亞穩(wěn)態(tài)的應(yīng)對措施

跨時鐘域的亞穩(wěn)態(tài)的應(yīng)對措施

評論