編者注:本文內容看似簡單,但是簡單結果的背后卻隱藏著很多深層次的問題,歡迎大家給出你們的答案。此類問題在多個行業產品當中常常會出現。

隨著信號速率的提升,以及小型化產品的發展趨勢,如何減小串擾變得越來越棘手。眾所周知,串擾與很多因素有關系,比如傳輸線之間的間距,傳輸線耦合的長度,攻擊信號的上升時間,阻抗不連續等等。因為串擾問題比較復雜,要是解決不好,還有可能會影響到其它信號完整性的問題。

今天給大家分享一個串擾引發損耗變大的問題。這類問題經常出現在小型化的產品、連接器、線纜等產品中。

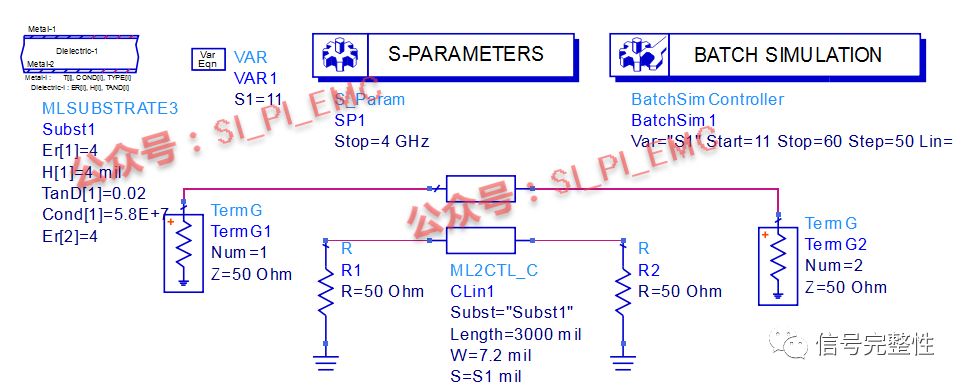

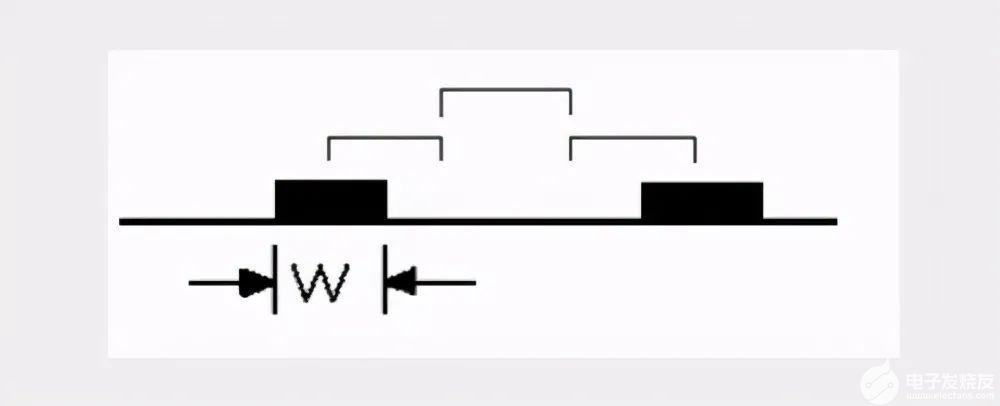

首先在ADS原理圖中搭建一個仿真電路,掃描仿真間距為11mil和60mil兩種情況。

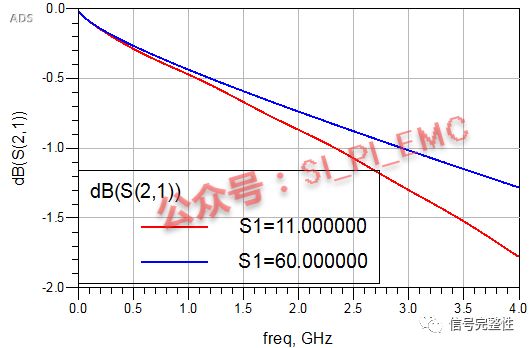

運行仿真之后查看插入損耗的結果:

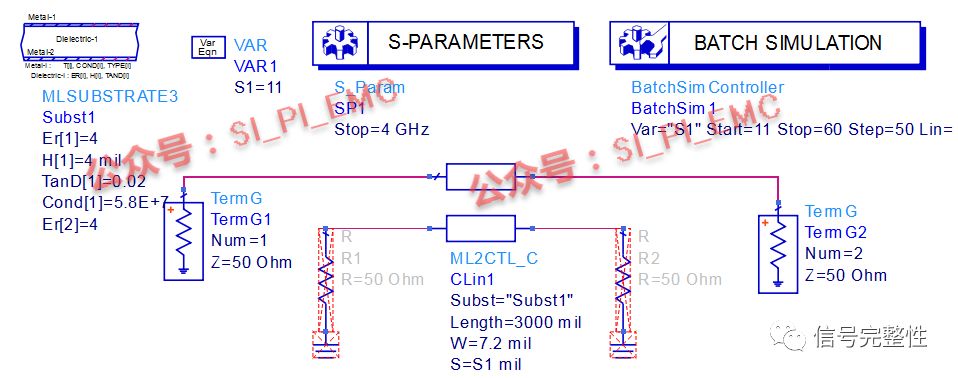

Disable電路圖上的R1和R2:

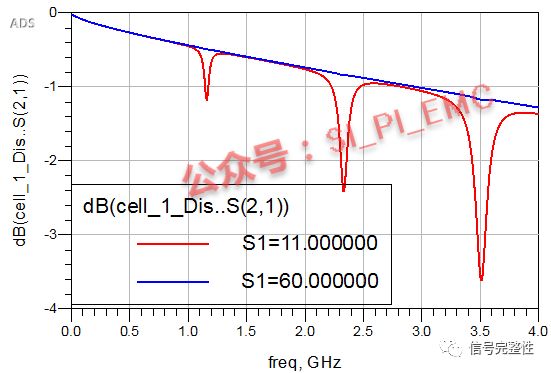

仿真如下圖所示:

從結果上分析來看,去掉電阻后,距離為60mil時,結果幾乎沒有變化,但是間距為11mil時,結果卻完全不一致,產生了三個非常大的諧振點。這就足以導致產品不滿足設計的要求。

從上面仿真結果中,我們可以看到解決這個問題有兩個非常便捷常用的方式,要么拉大距離、要么做好端接。大家可以相互討論下有沒有其它的解決方案呢?答案肯定是有的,大家可以多多討論下。

審核編輯:湯梓紅

-

高速電路

+關注

關注

8文章

163瀏覽量

24547 -

串擾

+關注

關注

4文章

189瀏覽量

27366 -

仿真電路

+關注

關注

5文章

82瀏覽量

33704

原文標題:【干貨】高速電路中串擾引發的損耗問題

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高速互連信號串擾的分析及優化

高速PCB設計中的串擾分析與控制

高速PCB中微帶線的串擾分析

高速電路中串擾引發的損耗問題

高速電路中串擾引發的損耗問題

評論