隨著半導體制程節點的持續演進,短溝道效應以及量子隧穿效應帶來的發熱、漏電等問題愈發嚴重,追求經濟效能的摩爾定律日趨放緩。

在此背景下,產業開始轉向以先進封裝為代表的新賽道,伴隨著先進封裝而出現的第一個新概念就是Chiplet:

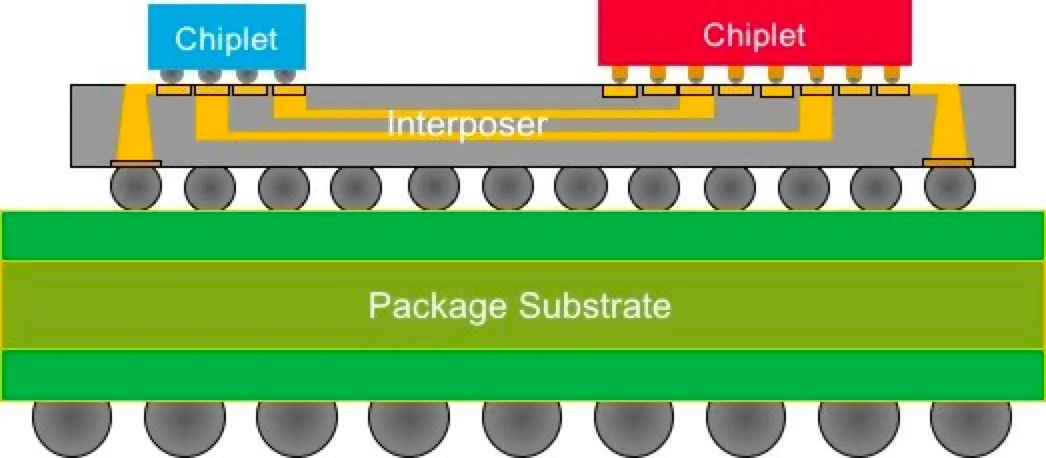

這些類似樂高積木一樣的功能模塊通過中介層(interposer)連接在一起,然后附著在封裝基底上。

英特爾的Foveros封裝技術就是采用這種思路,通過2.5D堆疊而實現不同chiplets的累加堆疊的集成。

Foveros將會在傳統無源中介層之上擴展裸片堆疊模式,可以在CPU、圖像處理器和AI加速器等高性能邏輯器件之上疊加存儲器。

這種技術可以將系統級芯片產品細分為許多不同的chiplets,其中I/O、SRAM和電源電路都可以在一個基礎裸片上制造,然后在其上疊加高性能chiplets。

與傳統SoC相比,Chiplet的思想是將不同的小芯粒通過先進封裝形成系統芯片;這也意味著,更為專業的設計工具對Chiplet未來生態的發展至關重要:

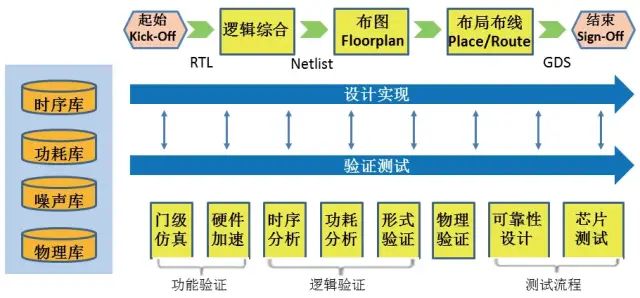

EDA設計流程圖

Chiplet因為需要更多異構芯片和各類總線的加入,將會使得整個芯片的設計過程變得更加復雜:

相關半導體行業從業者就指出:在一個封裝只有幾百個I/O的時代,封裝設計者還有可能用試算表(Spreadsheet)來規劃I/O,但在動輒數千甚至上萬個I/O互連的先進封裝設計中,這種方法不僅太耗時,而且出錯的機率很高。

基于資料庫的互連設計,還有設計規則檢查(DRC),都將成為先進封裝設計的標準工具。

此外,以往封裝業界習慣使用的Gerber檔格式,在先進封裝時代或許將改成GDSII檔格式;整體來說,封裝業界所使用的工具,都會變得越來越像Fab跟IC設計者所使用的工具。

特別是,在芯片的整體設計之前:為了把SoC拆解成Chiplet,相關的EDA工具需要芯片設計人員更多協同。

不僅是RDL Netlist、線路布局(Place & Route)的工具需要更新,設計人員還需要更多設計模擬工具來解決多晶片所衍生的電源一致性(PI)、訊號一致性(SI)、電磁相容(EMC)、散熱(Thermal)等問題。

首先EDA工具需要在芯片互聯接口的標準化方面進行改進;其次是可擴展性,Chiplet下芯片設計工程師需要同時對多個chiplets進行布局和驗證。

由于其需要采用堆疊方式進行設計,那么將十分考驗散熱能力;對于EDA工具的要求就在于,如何保障不同chiplets間堆疊后產生的熱度不會損壞芯片。

相比之下,頭部EDA公司可能會略早發現這些挑戰,不過由于行業都還在對此探索,因此不會有太大差距。

從當下Chiplet的角度來看:在相關標準還沒完全確定,相關廠商提出的基礎能力和標準各不相同的前提下;相關頭部EDA公司在Chiplet領域是與國內和海外公司共同推進生態、制定標準的發展進程,因此對于中國廠商來說是一個機會。

就如作為全球排名第一的EDA解決方案供應商,新思科技也在致力于與國內的眾多芯片設計公司一同探索相關Chiplet解決方案:

新思科技中國區副總經理朱勇強調:要使Chiplet做到通用化,不僅需要類似于UCIe等協議的定義,還需要國內外更多設計廠商的一同探索與發展;

新思科技對其保持一個歡迎的態度,如果將來標準能夠普及開來,對國內的廠商更快地推出自己的Chiplet產品也是有益的。

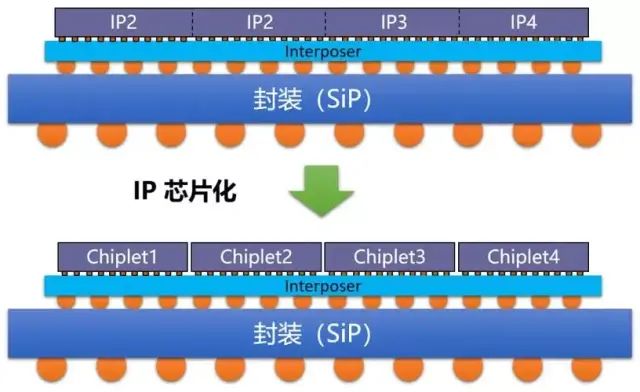

當然,相較于設計工具,Chiplet的IP新理念也至關重要。

一些半導體IP核以硅片的形式提供,IP即是chiplets,旨在以芯粒形式實現IP的“即插即用”和“重復利用”。

以解決原有先進制程工藝芯片面臨的性能與成本的矛盾,并降低較大規模芯片的設計時間和風險,實現從傳統SoC封裝的IP到先進封裝中以獨立的chiplets形式呈現的IP。

Chiplet的IP新理念

Chiplet的IP新理念在為芯片降低成本及加速產品迭代上至關重要:

如果在芯片設計階段,就將大規模的SoC按照不同的功能模塊分解為一個個的chiplets,那么部分chiplets則可以做到類似模塊化的設計,而且可以重復運用在不同的芯片產品當中。

這樣可以極大降低芯片設計的難度和設計成本,同時也有利于后續產品的迭代,加速產品的上市周期。

Chiplet的IP新理念在為降低芯片設計難度及提升靈活性上至關重要:

對于很多SoC廠商來說,原來設計一款大型的SoC芯片時,需要將大量第三方IP與自己的IP整合到一起,形成一個統一的SoC,然后采用同一個制程工藝進行制造:

而如果采用Chiplet模式,芯片設計廠商可以直接選擇第三方的基于適合的工藝制程的以chiplets形式提供的IP,然后再通過先進封裝技術將chiplets封裝在一起即可;這樣可以極大的降低芯片設計難度,提升靈活性和效率。

審核編輯:劉清

-

存儲器

+關注

關注

38文章

7639瀏覽量

166619 -

SoC芯片

+關注

關注

1文章

638瀏覽量

35706 -

DRC

+關注

關注

2文章

154瀏覽量

36971

原文標題:從SoC走向Chiplet,設計工具及IP支持至關重要

文章出處:【微信號:奇普樂芯片技術,微信公眾號:奇普樂芯片技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智多晶FPGA設計工具HqFpga接入DeepSeek大模型

安森美WebDesigner+設計工具使用心得

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet:芯片良率與可靠性的新保障!

VirtualLab Fusion應用:使用1D-1D EPE的光波導布局設計工具

VirtualLab Fusion應用:光導布局設計工具

解鎖Chiplet潛力:封裝技術是關鍵

安森美系統設計工具介紹

IMEC組建汽車Chiplet聯盟

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

如何為電量計工具Multi-updater編輯PCFG文件

Chiplet的IP新理念與設計工具

Chiplet的IP新理念與設計工具

評論