unpacked union中各個成員的大小可以是不同的。

舉一個例子

typedef Union {

logic [5:0] a;

logic [3:0] b;

logic c;

} myUnionType

myUnionType myUnion;

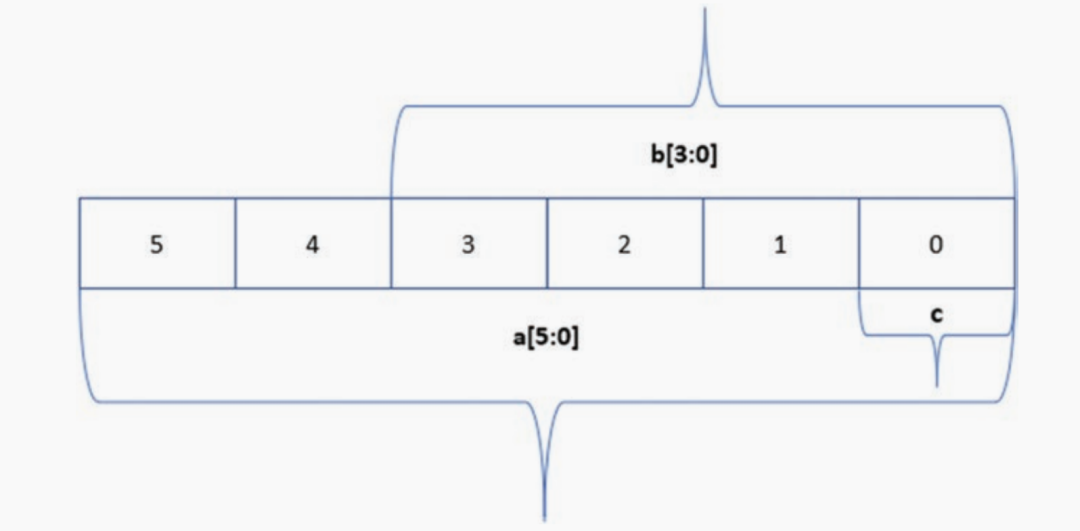

上面的union成員大小都是不同的,這個union整體的大小取決于其中size最大的成員,如下圖示例:

logic [5:0] a

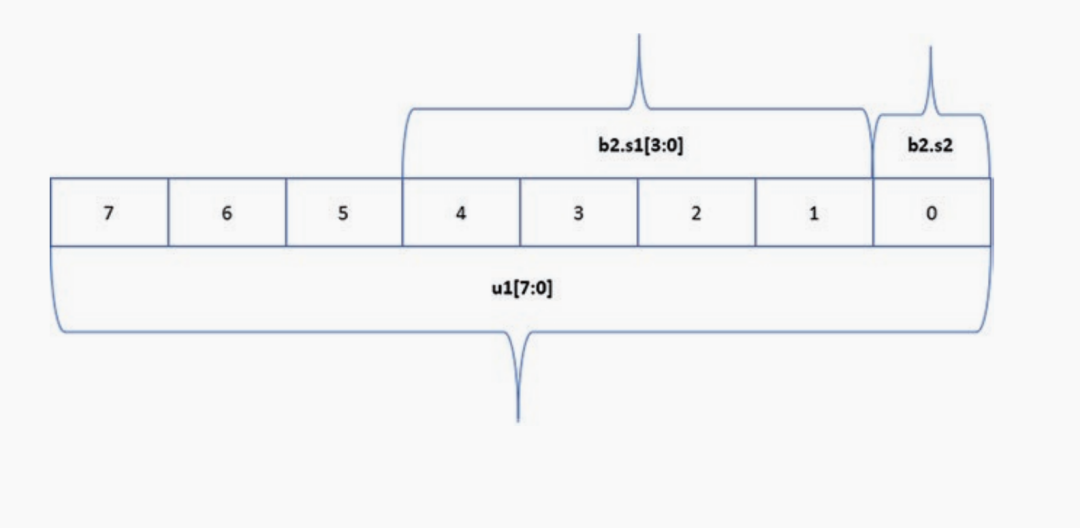

再看一下unpacked union中存在struct成員內存分配的示例:

typedef struct packed {

bit [3:0] s1;

bit s2;

} myStruct;

typedef union {

logic [7:0] u1;

myStruct b2;

} mUnionT;

mUnionT Union1;

對于這個union,最大 size的成員是“logic [7:0]

b1.”所以,這個union整體的大小是

對于一個union,如果你寫入成員1,再讀取成員2,實際上你讀取的就是剛剛寫入的成員1,這恰恰也說明了union的本質,即同一個物理存儲實體。

module union_example;

logic [31:0] x;

typedef union {

int a;

byte b;

bit [15:0] c;

} data;

data d1;

initial begin

d1.a = 32'h ffff_ffff; //write to d1.a

x = d1.b; //read from d1.b

$display("x = %h",x);

d1.b = 8'h 01; //write to d1.b

x = d1.a; //read from d1.a

$display("x = %h",x);

d1.c = 16'h 1010; //write to d1.c

x = d1.a; //read from d1.a

$display("x = %h",x);

end

endmodule

仿真log:

x = ffffffff x = 00000001 x = 00001010 V C S S i m u l a t i o n R e p o r t

上面的例子聲明了一個unpacked union “data.”,然后例化了一個data 類型的數據"d1"

在initial語句塊中,我們首先寫入union中的成員“int a”:

d1.a = 32'h ffff_ffff; //write to d1.a

注意,此時我們沒有向“d1.b”寫入任何內容。但既然union只有一個物理存儲實體,所以這些成員具有相同的值。所以,當我們從" d1 "讀取數據b

x = d1.b; //read from d1.b

仿真log會打印

x = ffffffff

反之亦然,當我們向b寫入數據,數據也會反映到a上。

d1.b = 8'h 01; //write to d1.b

此時a會打印:

x = 00000001

成員c的寫入同樣也會反映到成員a,如打印log所示。

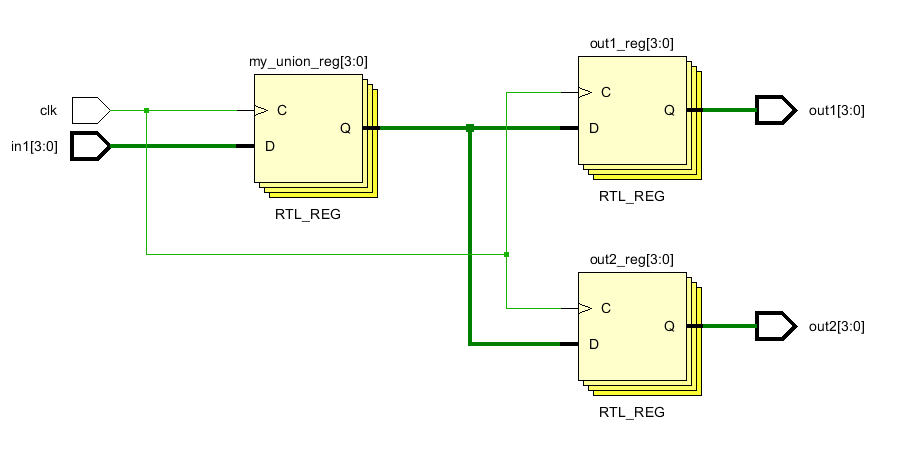

這再次表明union中的所有成員共享一個物理存儲空間,對于RTL的可綜合性,要求這些成員的大小相同。

審核編輯:湯梓紅

-

Verilog

+關注

關注

29文章

1366瀏覽量

111996 -

System

+關注

關注

0文章

166瀏覽量

37641 -

union

+關注

關注

0文章

10瀏覽量

4416

原文標題:SystemVerilog中的Unpacked Unions

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

SystemVerilog中的“const”類屬性

SystemVerilog的斷言手冊

SystemVerilog中$cast的應用

unpacked數組和packed數組的主要區別

SystemVerilog中的tagged Unions是什么

SystemVerilog中的Packed Union

SystemVerilog中的Semaphores

Systemverilog中的Driving Strength講解

SystemVerilog中的Unpacked Unions

SystemVerilog中的Unpacked Unions

評論