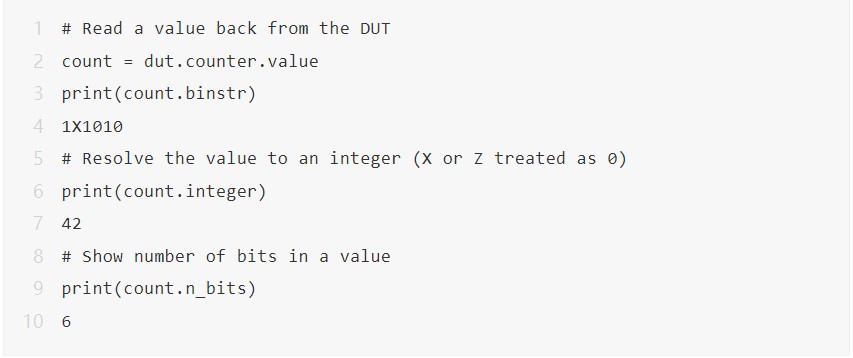

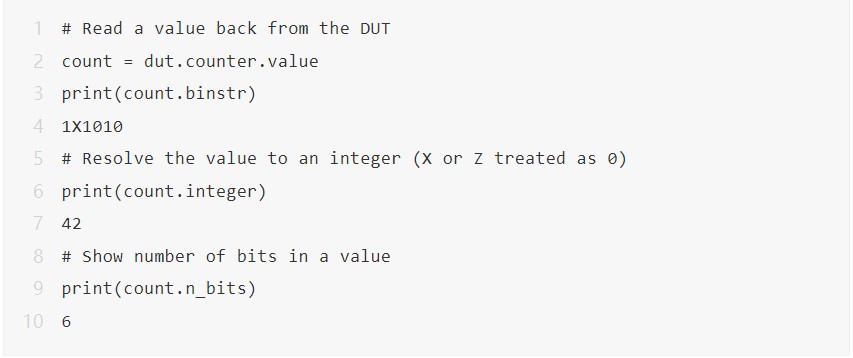

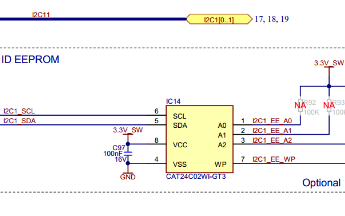

對于信號的讀取,我們在SystemVerilog中,可以直接讀取信號值,而在cocotb中,其為接口變量提供了value方法屬性用于獲取信號值。

2022-07-21 09:07:29 3136

3136

在systemverilog中,如果一個類沒有顯式地聲明構造函數(new()),那么編譯仿真工具會自動提供一個隱式的new()函數。這個new函數會默認地將所有屬性變量。

2022-11-16 09:58:24 2700

2700 SystemVerilog中多態能夠工作的前提是父類中的方法被聲明為virtual的。

2022-11-28 11:12:42 466

466 protected類屬性或方法具有local成員的所有特征,除此之外的是,protected類屬性或方法對擴展類是可見的。

2022-11-30 09:09:30 662

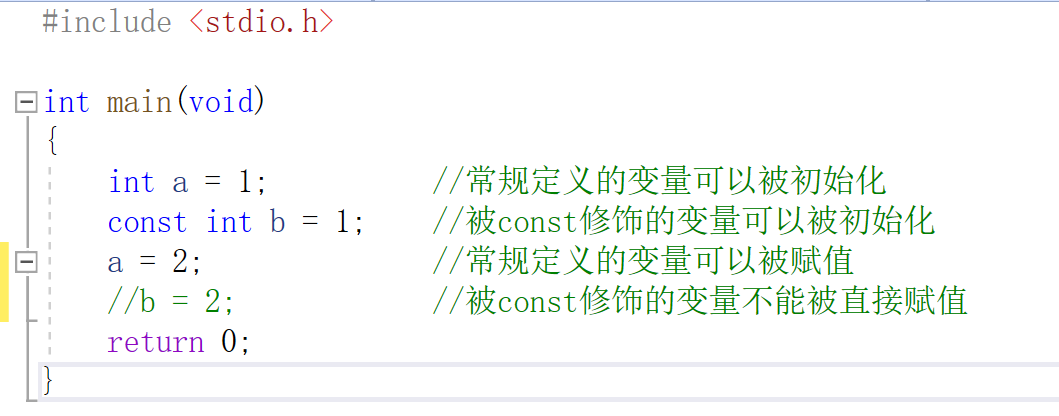

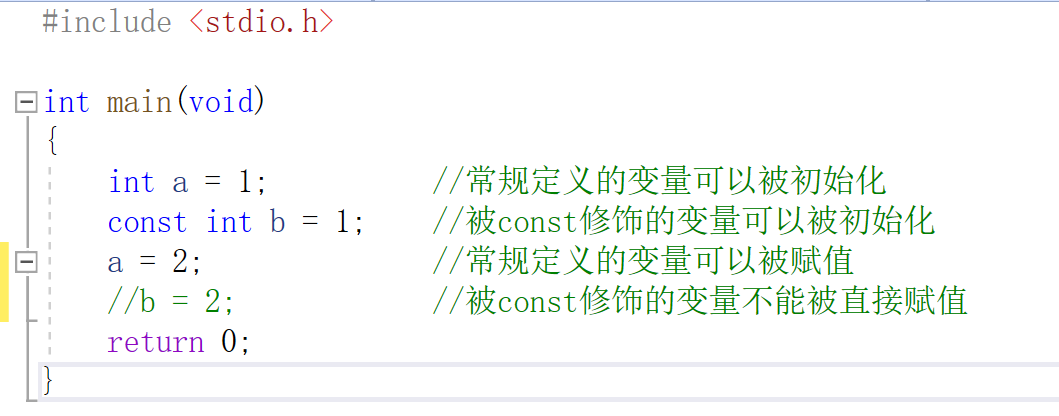

662 本期來講解一個C語言的關鍵字——const。

2023-06-21 11:05:36 927

927

const是constant的簡寫,用來定義常量,如果一個變量被const修飾,那么它的值就不能再被改變。

2023-06-29 09:51:01 326

326 在 SystemVerilog 中,聯合只是信號,可通過不同名稱和縱橫比來加以引用。

2023-10-08 15:45:14 593

593

SystemVerilog 的VMM 驗證方法學教程教材包含大量經典的VMM源代碼,可以實際操作練習的例子,更是ic從業人員的絕佳學習資料。SystemVerilog 的VMM 驗證方法學教程教材[hide][/hide]

2012-01-11 11:21:38

本帖最后由 鼻子抽筋 于 2012-2-21 15:41 編輯

SystemVerilog給予Verilog、VHDL和C/C++優點為一身的硬件描述語言,很值得學一學。1、8-bit up

2012-02-21 15:39:27

SystemVerilog有哪些標準?

2021-06-21 08:09:41

const與#pragma data:code const有什么區別啊?還有為什么程序中添加#pragma data:code就報錯啊?求解啊,各位大神!!!

2013-03-29 19:59:20

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發展的朋友。QQ群374590107歡迎有志于FPGA開發,IC設計的朋友加入一起交流。一起為中國的IC加油!!!

2014-06-02 09:47:23

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本語法以及和verilog語言之間的區別。

2015-04-01 14:24:14

const int x = 1;int* p1 = const_cast(&x);將x轉換為引用類型,其目標了類型是int指針類型,剔除x的只讀屬性這句話我這樣理解可以嗎

2020-03-20 04:35:54

常數表達式中使用一個符號名(也就是說必須在編譯時確定其值的話),C幾乎限定你只能使用預處理器的#define來進行。在C中const是外連接的,不能將其定義放在頭文件中。如果用const int

2016-11-11 10:00:26

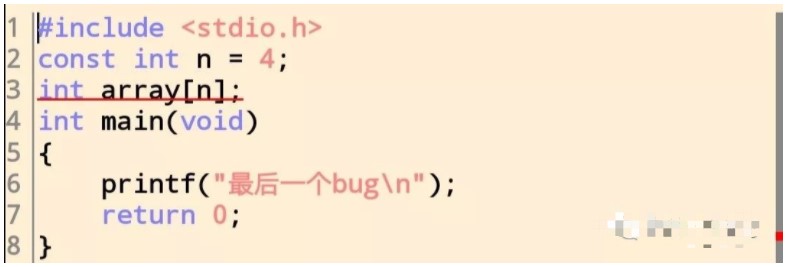

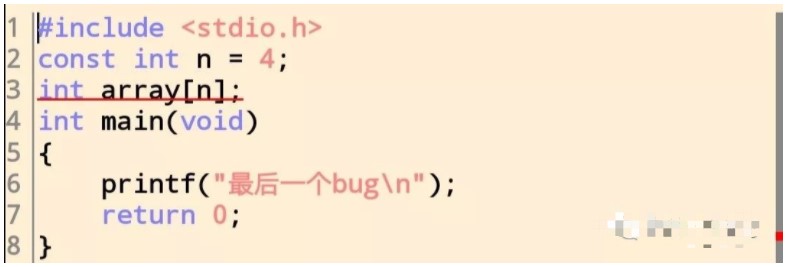

這個值由編譯器限定不允許被修改。C語言關鍵字const就是用來限定一個變量不允許被改變的修飾符(Qualifier)。上述代碼中變量n被修飾為只讀變量,可惜再怎么修飾也不是常量。而ANSI C規定

2017-04-23 11:58:33

,只不過這個值由編譯器限定不允許被修改。C語言關鍵字const就是用來限定一個變量不允許被改變的修飾符(Qualifier)。上述代碼中變量n被修飾為只讀變量,可惜再怎么修飾也不是常量。而ANSI C規定

2008-10-07 11:20:57

請問一下,如何實現類屬性、方法的級聯調用?類似于控件的屬性、方法列表?如下圖所示系統自帶的屬性節點出現的級聯菜單:訪問自定義類的屬性的時候不出現級聯菜單,該如何實現呢?

2018-11-22 09:52:34

Labview 父類屬性找不到子VI,打開工程項目,右擊父類的屬性MitsubishiPLCCommunication.ctl —> 查找 —> 子VI會提示“未找到任何項”如圖所示,類似這樣的問題,請問要怎么解決呢?急。。。。

2019-03-25 11:08:15

MDK中Const和volatile的使用volatile的使用區分C程序員和嵌入式系統程序員的最基本的問題。搞嵌入式的程序員經常同硬件、中斷、RTOS等等打交道,所有這些都要求用到volatile

2008-08-02 10:17:59

Python中實例屬性和實例方法Python中類屬性和類方法Python中調用類方法

2020-11-05 06:25:06

設計驗證相關的公開課!SystemVerilog作為IEEE-1800,將VLSI設計、驗證和斷言屬性集中在一起,是數字超大規模集成電路設計和驗證領域最流行的語言。從2006年至今

2013-06-10 09:25:55

const byte tt[20] = {0,1,2,3,4,5,6,7,8,9};const byte mm[20] ={3,4,5,6,7,0,8,6,6,4,1};const byte *ss[2] = {tt,mm};為什么tt和mm 編譯后放到 flash 中 而 ss卻放到RAM中

2018-06-07 11:53:17

labview中利用屬性節點來調用控件的信息,這種屬性節點的調用方式是傳值還是傳引用呢?比如利用屬性節點傳遞控件的值的時候,有沒有另開辟內存空間啊?

2012-02-07 13:19:14

labview里的布爾類屬性done是什么?怎么用?謝謝了

2014-10-27 10:02:48

在msp430中定義了一個數組,constunsignedchar disp[];為什么不可以在程序中對這個數組進行賦值???進行賦值時會報錯Error[Pe137]: expression must be a modifiable lvalue 如果去掉const編輯后不會報錯。這是為什么??

2014-08-22 09:55:28

大家好,我對一個 round robin 的 systemverilog 代碼有疑惑。https://www.edaplayground.com/x/2TzD代碼第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

__I、 __O 、__IO是什么意思?這是ST庫里面的宏定義,定義如下:#define__I volatile const/*!< defines 'read only

2014-06-23 23:20:54

值類屬性返回有關數組類型、塊和常用數據類型的特定值,值類屬性還用于返回數組的長度或者類型的最低邊界,值類屬性分成 3 個子類。1.值類型屬性:返回類型的邊界值類型屬性用來返回類型的邊界,有 4 種

2018-09-14 09:12:07

函數類屬性為設計者返回類型、數組和信號信息。用函數類屬性時,函數調用由輸入變元的值返回一個值,返回值為可枚舉值的位置號碼、在一個△時間內信號是否改變的指示或者一個數組的邊界。函數類屬性可細分為 3

2018-09-14 09:15:33

信號是不能在子程序內部使用的,返回的信息和由某種函數屬性所提供的功能非常類似,區別是這類專用信號用于正常信號能用的任何場合,包括在敏感表中。有如下的 4 類屬性:? S'DELAYED[(time

2018-09-17 09:52:30

義屬性數據范圍類屬性返回數組類型的范圍值,并由所選的輸入參數返回指定的指數范圍,這種屬性標記如下:a'RANGE[(n)];a'REVERSE_RANGE[(n)]。屬性 RANGE 將返回由參數 n 值

2018-09-17 10:04:10

現在.c文件中編譯器會提示出錯。我們知道定義一個數組必須指定其元素的個數,這也從側面證實在C語言中const修飾的Max仍然是變量,只不過是只讀屬性罷了。還有值得注意的是,定義變量的同時,必須初始化

2021-06-15 11:00:48

int const i=5,同樣正確。此外,const修飾變量還起到了節約空間的目的,通常編譯器并不給普通const只讀變量分配空間,而是將它們保存到符號表中,無需讀寫內存操作,程序執行效率也會提高

2021-03-29 10:53:10

FPGA中接口的連接方式。 ??也許很多FPGA工程師對SystemVerilog并不是很了解,因為以前的FPGA開發工具是不支持SystemVerilog的,導致大家都是用VHDL或者Verilog來

2021-01-08 17:23:22

在某大型科技公司的招聘網站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語言,感覺SystemVerilog語言是用于ASIC驗證的,那么做FPGA工程師有沒有必要掌握SystemVerilog語言呢?

2017-08-02 20:30:21

是你如果改變數組里面的值會報錯。const表示內容不被修改,相當于常數。在51C語言中,const聲明的一般被編譯器存在ROM中

2021-07-15 08:52:52

我們將展示如何在SystemVerilog中為狀態機的命令序列的生成建模,并且我們將看到它是如何實現更高效的建模,以及實現更好的測試生成。?

2021-01-01 06:05:05

玩了好久labview,這個問題一直沒弄懂。有時候在右鍵創建時,會顯示“嚴格”類屬性。如下圖請問這個“嚴格”是指什么?可否取消掉?

2017-03-03 22:09:06

類成員函數中const的使用,有什么注意事項?

2021-04-26 06:42:30

導入SystemVerilog程序包意味著什么?

2020-12-11 06:53:29

2打兩拍systemverilog與VHDL編碼1 本章目錄1)FPGA簡介2)SystemVerilog簡介3)VHDL簡介4)打兩拍verilog編碼5)打兩拍VHDL編碼6)結束語2 FPGA

2021-07-26 06:19:28

SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 本文利用形式化的方法對SystemVerilog的指稱語義進行研究,采用EBES(extendedbundle event structure)作為抽象模型,以便更好的描述SystemVerilog真并發的特點。我們的主要工作是:首先,

2009-12-22 14:01:07 12

12 如何采用SystemVerilog 來改善基于FPGA 的ASIC 原型關鍵詞:FPGA, ASIC, SystemVerilog摘要:ASIC 在解決高性能復雜設計概念方面提供了一種解決方案,但是ASIC 也是高投資風險的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 就 SystemC 和 SystemVerilog 這兩種語言而言, SystemC 是C++在硬件支持方面的擴展,而 SystemVerilog 則繼承了 Verilog,并對 Verilog 在面向對象和驗證能力方面進行了擴展。這兩種語言均支持

2010-08-16 10:52:48 5140

5140 SystemVerilog 是過去10年來多方面技術發展和實際試驗的結晶,包括硬件描述語言(HDL)、硬件驗證語言(HVL)、SystemC、Superlog和屬性規范語言。它們都從技術和市場的成敗中得到了豐富的經

2010-09-07 09:55:16 1118

1118 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學以及驗證庫開發出先進驗證環境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復雜S

2011-05-09 15:22:02 52

52 針對類屬型數據聚類中對象間距離函數定義的困難問題,提出一種基于貝葉斯概率估計的類屬數據聚類算法。首先,提出一種屬性加權的概率模型,在這個模型中每個類屬屬性被賦予一個反映其重要性的權重;其次,經過

2017-12-04 16:42:24 0

0 在多標記學習中,由于不同的標記可能會帶有自身的一些特性,所以目前已經出現了基于標記類屬屬性的多標記學習算法LIFT。然而,類屬屬性的構建可能會增加屬性向量的維度,致使屬性空間存在冗余信息。為此,借助

2017-12-29 14:46:15 0

0 相傳在C的世界里出現了一件極品裝備(鐵布衫)const、它的出現,讓天下的所有刺客和黑客都聞風喪膽,在它的保護下,所有的變量都可以保存的完好無損const是constant的縮寫,表示海枯石爛、恒定不變、一旦相伴、永不變心。

2018-06-11 16:26:15 2361

2361 Const也是應該廣泛的關鍵字,表示后面定義有可能是一個不變的常量,但是跟各種數據類型定義組合,能演變出復雜含義。常類型是指使用類型修飾符const說明的類型,常類型的變量或對象的值是不能被更新

2018-09-20 09:37:00 2792

2792 另外const 的一些強大的功能在于它在函數聲明中的應用。在一個函數聲明中,const 可以修飾函數的返回值,或某個參數;對于成員函數,還可以修飾是整個函數。有如下幾種情況,以下會逐漸的說明用法:

2019-05-06 16:34:29 460

460

在Keil 51中,code修飾的變量放在ROM(Flash)中,而const修飾的變量為只讀(不可修改),放在RAM中!可以用“code const”修飾變量,表示變量存儲在ROM中,且為只讀

2019-09-04 17:27:00 0

0 由上面的內容可以看出,Java封裝就是把現實世界同類事物的共同特征和行為抽取出來,放到一個新建的類中,并設置類屬性(特征)和行為的訪問權限,同時提供外部訪問類屬性和行為的方法。

2019-10-15 09:53:31 1581

1581 以前只是用const與readonly聲明常量,今天在網上看了它們的一些其它屬性,覺得有必要弄清楚它們的用法與異同,所以動手找了找,也寫了幾行代碼以呈現,還望大家給予指點。

2019-11-07 15:54:19 10

10 C++與C中的const關鍵字有何差別?

2020-02-03 14:51:09 1576

1576 今天給大家分享一下這段時間學習c++的總結學習:c++里面的const關鍵字和引用。

2020-12-24 15:35:05 596

596 手冊的這一部分探討了使用SystemVerilog進行驗證,然后查看了使用SystemVerilog的優點和缺點。

2021-03-29 10:32:46 23

23 ? ?STM32的const全局變量地址 程序如下: const int globalConstDat = 12; int globalDat = 11; int main(void) { int

2021-07-23 10:50:19 4414

4414 ASP.NET--IsPostBack類屬性總結(力普拉斯電源技術有限公司招聘)-文檔為ASP.NET--IsPostBack類屬性總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,

2021-09-17 15:26:23 3

3 const 作用 修飾變量,說明該變量不可以被改變; 修飾指針,分為指向常量的指針(pointer to const)和自身是常量的指針(常量指針,const pointer); 修飾引用,指向常量

2021-09-23 11:39:48 1719

1719 作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一種硬件描述和驗證語言

2021-10-11 10:35:38 2042

2042 __attribute__所指定的編譯屬性,這里著重講解一下在KEIL 環境下__attribute__中的section的使用方法。一、起因我們先來看一個宏#define INIT_EXPORT(fn, level) \ RT_USED const init_fn_t __rt_

2021-11-16 18:21:01 47

47 被const修飾的全局變量不能以地址的形式進行修改,由于它在內存中位于常量區,他的地址空間是只讀的。在C語言中被const的變量是直接被分配內存的。

2022-04-24 16:08:54 1144

1144 我們會發現兩者的區別const一個注釋的全局變量一個注釋的局部變量,我們編譯都能通過,不過使用全部變量的程序運行會報段錯誤,而局部變量的能夠過得正確結果。對于通過指針修改const的值是一種與編譯器

2022-08-12 09:13:42 1128

1128

event是SystemVerilog語言中的一個強大特性,可以支持多個并發進程之間的同步。

2022-10-17 10:21:33 1024

1024 SystemVerilog casting意味著將一種數據類型轉換為另一種數據類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個變量具有相同的數據類型。

2022-10-17 14:35:40 1960

1960 學習Systemverilog必備的手冊,很全且介紹詳細

2022-10-19 16:04:06 2

2 SystemVerilog提供了幾個內置方法來支持數組搜索、排序等功能。

2022-10-31 10:10:37 1760

1760 SystemVerilog packages提供了對于許多不同數據類型的封裝,包括變量、task、function、assertion等等,以至于可以在多個module中共享。

2022-11-07 09:44:45 862

862 SystemVerilog“struct”表示相同或不同數據類型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog中的句柄賦值和對象復制的概念是有區別的。

2022-11-21 10:32:59 523

523 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了 C語言 數據類型、結構、壓縮

2022-12-08 10:35:05 1262

1262 SystemVerilog中Semaphore(旗語)是一個多個進程之間同步的機制之一,這里需要同步的原因是這多個進程共享某些資源。

2022-12-12 09:50:58 2344

2344 C語言標準庫中很多函數的參數都被 const 限制了,但我們在以前的編碼過程中并沒有注意這個問題,經常將非 const 類型的數據傳遞給 const 類型的形參,這樣做從未引發任何副作用,原因就是上面講到的,將非 const 類型轉換為 const 類型是允許的。

2023-01-05 10:03:42 396

396 上一篇文章介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-01-21 17:03:00 1519

1519 const我平時沒咋用過,最近在一份代碼中配置外設寄存器值的數組定義上看到用了這個,因此進行一下簡單的入門學習。在本文最后1點給出const在配置外設初始默認寄存器的用法。

2023-04-15 15:47:11 418

418 最近看別人的項目, 發現const使用比較多, 通過使用const來保護變量, 這篇推文就來簡單回顧一下相關知識!

2023-05-25 15:11:49 329

329 C++中的const關鍵字的用法非常靈活,而使用const將大大改善程序的健壯性

2023-05-26 09:06:25 341

341 在systemverilog中,net用于對電路中連線進行建模,driving strength(驅動強度)可以讓net變量值的建模更加精確。

2023-06-14 15:50:16 751

751

有時候我們希望定義這樣一種變量,它的值不能被改變,在整個作用域中都保持固定。例如,用一個變量來表示班級的最大人數,或者表示緩沖區的大小。為了滿足這一要求,可以使用const關鍵字對變量加以限定

2023-06-22 10:43:00 286

286 本文講一下SystemVerilog的time slot里的regions以及events的調度。SystemVerilog語言是根據離散事件執行模型定義的,由events驅動。

2023-07-12 11:20:32 775

775

上一篇文章《暗藏玄機的SV隨機化》介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-09-24 12:15:30 396

396 談到SystemVerilog,很多工程師都認為SystemVerilog僅僅是一門驗證語言,事實上不只如此。傳統的Verilog和VHDL被稱為HDL(Hardware Description

2023-10-19 11:19:19 342

342

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

電子發燒友App

電子發燒友App

評論