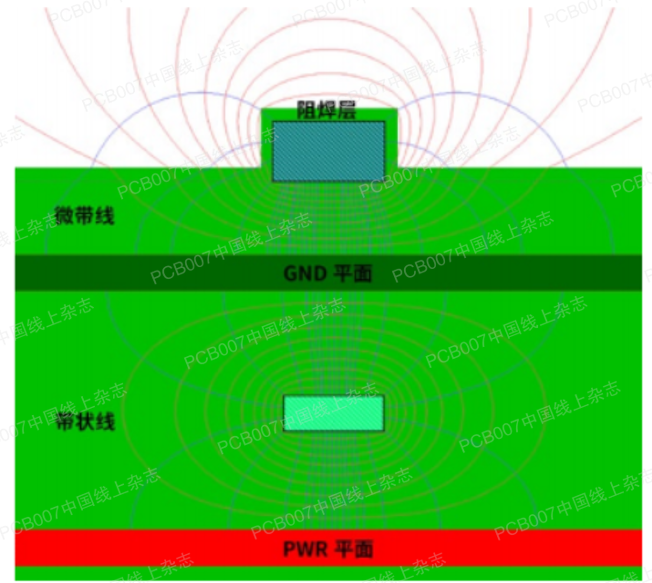

對(duì)于內(nèi)部帶狀線層(圖1),通過由平面之間的信號(hào)走線引導(dǎo)的多層PCB介質(zhì)材料進(jìn)行電磁(EM)能量傳播,但它在外部微帶層上的行為略有不同。微帶層通常在一側(cè)有完整接地平面,且允許輻射從無邊無際的表面進(jìn)入空氣中。經(jīng)過深思熟慮的布線策略可以避免高達(dá)10 dB的基板輻射。在平面之間嵌入信號(hào)可以降低對(duì)輻射的敏感性,并可提供靜電放電保護(hù)。因此,不僅可以防止噪聲輻射,還可以降低受到外部信號(hào)源影響的可能性。

圖1:微帶電磁場(頂部)和帶狀線電磁場(底部)

Hewlett-Packard進(jìn)行的研究發(fā)現(xiàn),與位于外層PCB中心的走線相比,位于PCB邊緣走線的輻射要高20 dB。

然而,對(duì)埋嵌走線進(jìn)行的相同測試表明,走線靠近PCB邊緣時(shí),輻射沒有變化。這意味著在外部微帶層布線時(shí),最好遠(yuǎn)離PCB邊緣。阻抗隨著走線下方參考面面積的減小而變化。

在多層PCB上,為了減少輻射,關(guān)鍵信號(hào)應(yīng)該布線在與實(shí)心參考面相鄰的帶狀線層上。信號(hào)走線和返回平面之間的間距應(yīng)盡可能小,以增加耦合并減少回路面積。

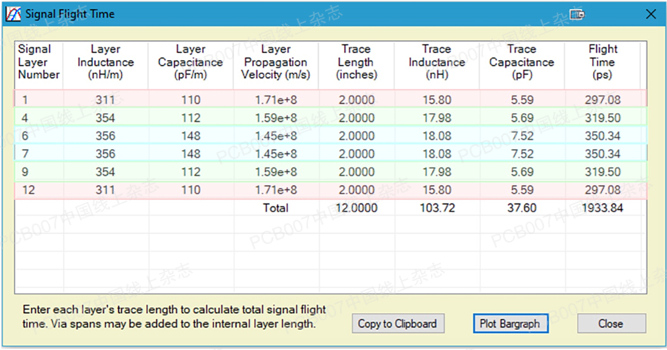

圖2:微帶線和帶狀線的相對(duì)信號(hào)傳播(在iCD Design Integrity中模擬)

要牢記3個(gè)約束條件:

保持波形的信號(hào)與空號(hào)脈沖之比相等,因?yàn)檫@樣可以消除所有偶數(shù)諧波。

在平面之間布線高速信號(hào),在靠近下降到內(nèi)層的驅(qū)動(dòng)端(200mil)扇出,然后用短扇出再次布線回到負(fù)載端。

對(duì)返回信號(hào)使用相同的參考面(如果可能,使用GND),這樣可減少回路面積,從而減少輻射。

微帶線周圍的電場一部分存在于介質(zhì)材料中,一部分存在于周圍空氣中。由于空氣的介電常數(shù)(Dk)為1,與帶狀線相比,它將加快信號(hào)傳播速度。即使調(diào)整每層上的走線寬度,以便阻抗相同,微帶線的傳播速度總是會(huì)比帶狀線快13%~17%。數(shù)字信號(hào)的傳播速度與走線幾何形狀及阻抗無關(guān)。

如果了解這個(gè)問題,為了補(bǔ)償變化的走線延遲,就可以匹配飛行時(shí)間(如圖2所示),以便在標(biāo)稱溫度下,微帶或帶狀線上運(yùn)行的所有信號(hào)可同時(shí)到達(dá)接收端。或者,目前許多布線器都有匹配延遲布線功能,使設(shè)計(jì)師能夠考慮微帶線和帶狀線結(jié)構(gòu)之間的飛行時(shí)間變化。注意,匹配延遲與不考慮飛行時(shí)間的匹配長度布線有很大不同。

例如,對(duì)于DDR3/4 Fly-by拓?fù)浣Y(jié)構(gòu),最好在兩個(gè)對(duì)稱的成對(duì)層上布線所有關(guān)鍵走線。在本文的案例中,成對(duì)層是第1層和第12層、第4層和第9層,再加上第6層和第7層。第4層和第9層是最好的成對(duì)層,因?yàn)樗鼈兦度氩⒖拷?2層PCB的平面對(duì)和有源器件。從微帶層到這些層(未顯示)有200 mil扇出。這兩層具有相同的延遲319.50 ps,并且在平面之間嵌入的堆疊對(duì)稱。

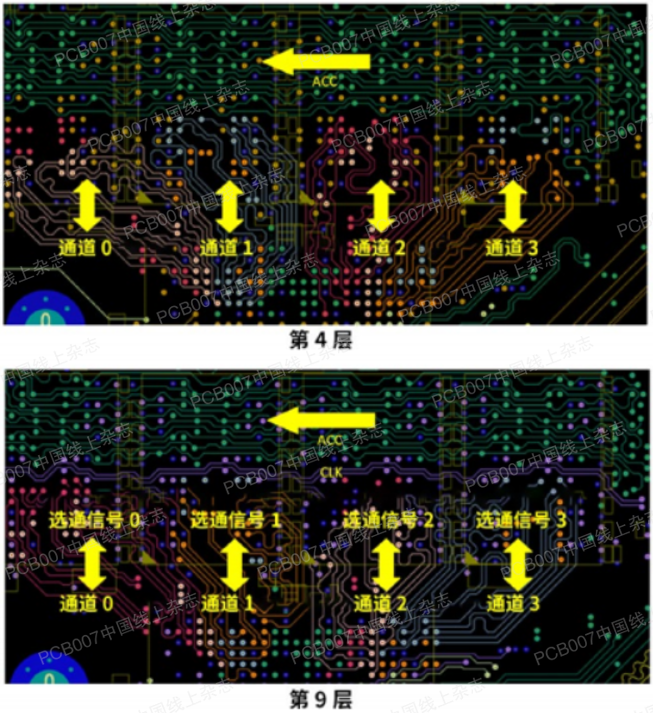

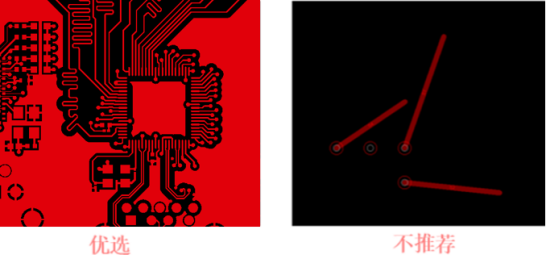

圖3顯示了數(shù)據(jù)通道(0—3)的布線方向與相關(guān)的差分選通信號(hào)相結(jié)合以及與差分時(shí)鐘相結(jié)合的地址、控制和命令(address, control and command,簡稱ACC)信號(hào)。不需要擔(dān)心層引起的飛行時(shí)間偏差,因?yàn)榈?層和第9層是相同的。

圖3:DDR3 Fly-by拓?fù)浣Y(jié)構(gòu)的布線策略

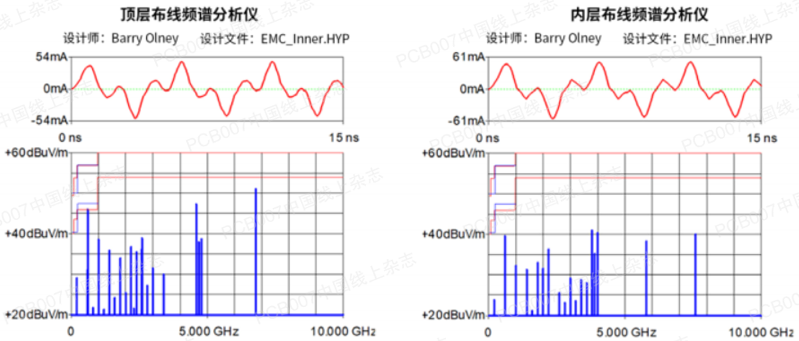

圖4顯示了外層和內(nèi)層之間的相對(duì)輻射。在該案例中,在第4層內(nèi)層布線的走線比在頂層布線的走線噪聲低4~10 dB。注意,頂層布線上存在40 dB以上的輻射諧波。此外,高頻元件更容易輻射,因?yàn)樗鼈兊牟ㄩL較短,與用作天線的走線長度相當(dāng)。因此,盡管諧波頻率分量的振幅減小,但隨著頻率的增加,輻射頻率會(huì)隨著走線特性而變化。

圖4:頂部微帶層與內(nèi)部帶狀線層布線信號(hào)的輻射對(duì)比

因此,除了較短的200 mil微帶扇出外,這種設(shè)計(jì)的發(fā)射遠(yuǎn)低于FCC/CISPR B級(jí)限制(較低的紅線)。然而,如果在外層布線,在6.76 GHz時(shí)輻射將為49.73 dB,在7.8 GHz時(shí)為52.10dB,可能無法通過測試。如果在開始布局之前規(guī)劃布線策略和堆疊設(shè)計(jì),那么電磁兼容性設(shè)計(jì)只需要很少的額外工作。

要點(diǎn)

在平面之間嵌入信號(hào)可減少這些發(fā)射和輻射敏感性,并可提供靜電放電保護(hù)。

在外部微帶層布線時(shí),最好遠(yuǎn)離PCB邊緣。

在多層PCB上,關(guān)鍵信號(hào)應(yīng)在與實(shí)心參考面相鄰的帶狀線層上布線,以減少輻射。

微帶線的傳播速度總是比帶狀線的傳播速度快13%~17%。

目前,許多布線器都有匹配延遲的布線功能,使設(shè)計(jì)師能夠考慮到飛行時(shí)間的變化。

在第4層內(nèi)層上布線的走線比在頂層布線的走線噪聲小4~10 dB。

審核編輯 :李倩

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4803瀏覽量

90515 -

電磁兼容性

+關(guān)注

關(guān)注

6文章

468瀏覽量

34229 -

電磁場

+關(guān)注

關(guān)注

0文章

800瀏覽量

48187

原文標(biāo)題:PCB設(shè)計(jì):使輻射最小化的布線策略

文章出處:【微信號(hào):actSMTC,微信公眾號(hào):actSMTC】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

符合EMC的PCB設(shè)計(jì)準(zhǔn)則

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

必學(xué)!PCB設(shè)計(jì)布線技巧、電機(jī)控制、電源管理設(shè)計(jì)教程等精華資料

建議收藏,這31條PCB設(shè)計(jì)布線技巧

【PCB】四層電路板的PCB設(shè)計(jì)

電子工程師的PCB設(shè)計(jì)經(jīng)驗(yàn)

PCB設(shè)計(jì)中的孔間距揭秘:最小間距究竟是多少?

為什么最小化光纖電纜中的DB損耗很重要

串行接口PCB設(shè)計(jì)指南:優(yōu)化布局與布線策略

AM62 PCB設(shè)計(jì)逃逸布線應(yīng)用說明

AM62x(AMC)PCB設(shè)計(jì)逃逸布線應(yīng)用說明

AM62Px PCB設(shè)計(jì)迂回布線

AM62x SiP PCB設(shè)計(jì)迂回布線

PCB設(shè)計(jì):使輻射最小化的布線策略

PCB設(shè)計(jì):使輻射最小化的布線策略

評(píng)論