本文作者:杜燕燕

Cadence公司 Pegasus Product Engineering Team

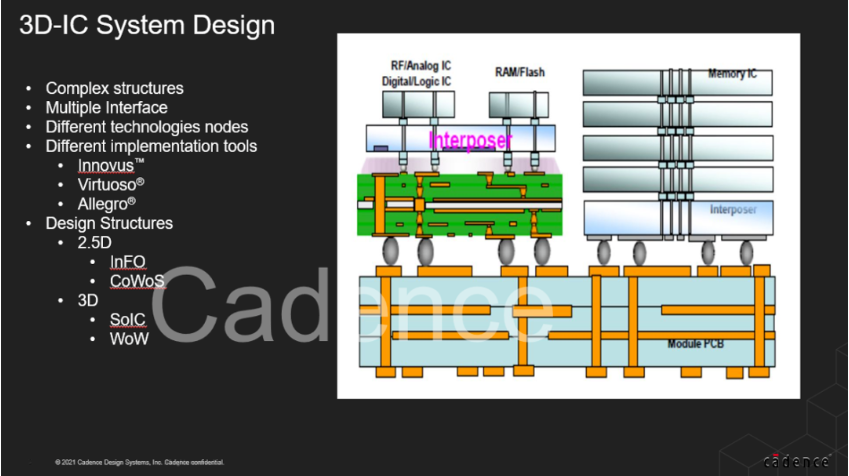

隨著芯片工藝尺寸的縮小趨于飽和或停滯,設計師們現在專注于通過 3D-IC 異構封裝,在芯片所在平面之外的三維空間中構建系統。3D-IC 異構封裝結構可能包括多個芯片,它們被放置在一個通用的中介層上,或者通過芯片內部的高級互連來集成內存單元、處理器和其他功能模塊。

3D-IC 異構封裝中集成了功能不同的芯片,這些芯片可以采用不同的工藝節點,也可以通過不同的 3D 結構來堆疊,而且芯片、中介層、封裝之間會形成多個接觸面,系統級的物理驗證變得很復雜,將面臨很多不同方面的挑戰:

013D-IC 設計中不同模塊的數據來自于不同的設計工具,設計師面臨著合并來自于不同平臺的物理數據然后去完成系統性的物理驗證和分析的挑戰。

02不同的芯片可能來自于不同的 Foundry,采用不同的工藝,有著不同的物理驗證規則,如何統一出一個系統級物理驗證規則?

03不同的 3D 結構中芯片和中介層的堆疊方式不同,設計師需要根據每個客戶的設計去定制不同的 LVS / ERC / DRC 驗證規則。

04每個不同的堆疊層和堆疊層間的接觸面都需要單獨的進行 LVS / ERC / DRC 檢查。

05每個接觸面都需要分別的進行 GDS 合并去做 LVS / ERC / DRC,如何能夠無縫連接的合并不同設計平臺的數據并且在驗證中將數據可視化?

06當芯片個數增加時,驗證的復雜度和工作量都會大大增加。

如何解決這些挑戰,讓我們先來看一下

3D-IC物理驗證的要求

對于 3D-IC 物理驗證,我們并不是指單顆 die 的物理驗證,而是指不同的堆疊層接觸形成電氣連接所需要進行的:

電氣規則檢查(ERC)

設計規則檢查(DRC)

版圖原理圖一致性檢查(LVS)

電氣規則檢查 ERC / 物理規則檢查 DRC

(Electrical Rule Checking / Design Rule Checking)

2.5D IC 采用 Micro Bump 在不同接觸面之間實現電氣連接和應力緩沖,Bump 是一種金屬凸點,常見的形狀有球狀和柱狀,隨著工藝技術發展,Bump 直徑最早可達 200um,目前先進工藝中都是采用 Micro Bump,它以更小的間距和更好的導熱性實現更多的 IO。

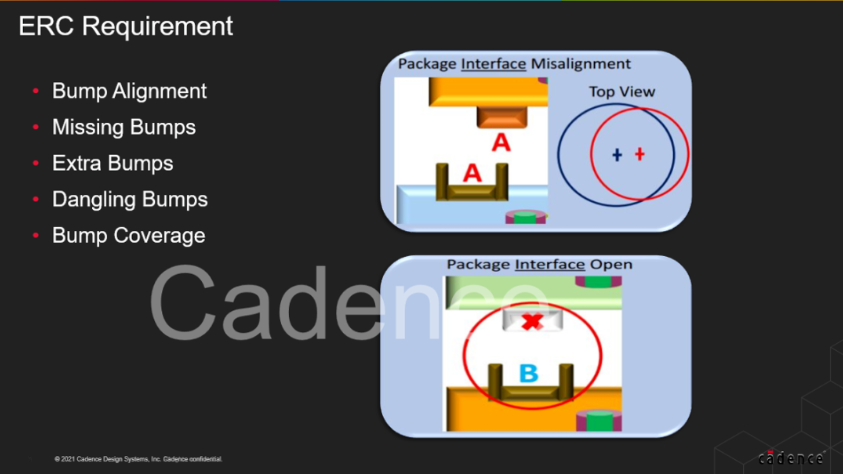

接觸面 ERC 需要檢查的項目主要包括:

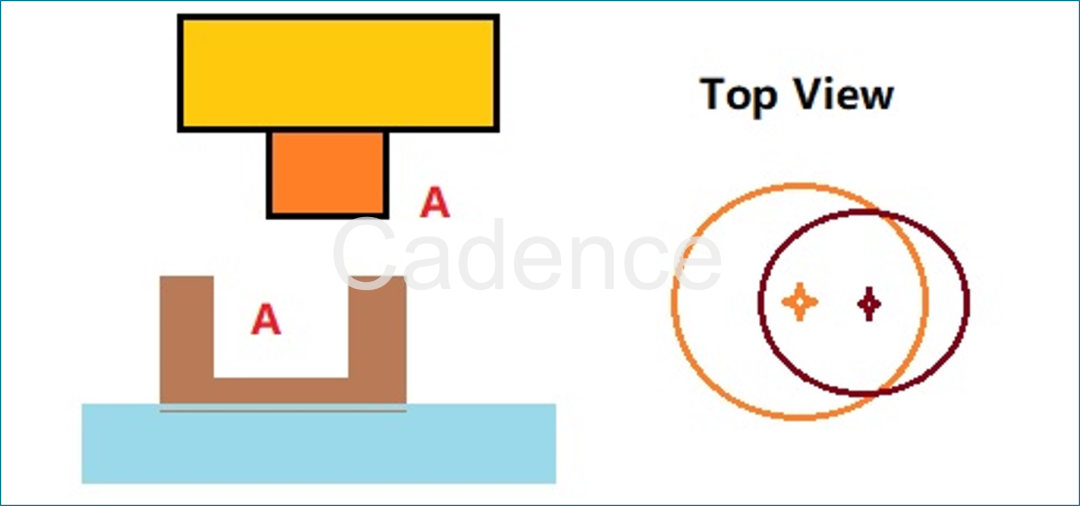

1Bump 對齊

檢查 Bump 有沒有放在正確的位置

2Bump 覆蓋率

有些工藝不要求 Bump 完全對齊,兩個 Bump 的形狀大小也不同,這時可能要求兩個 Bump 重合的區域占比達到一定的數值,80% 或者 90% 等。

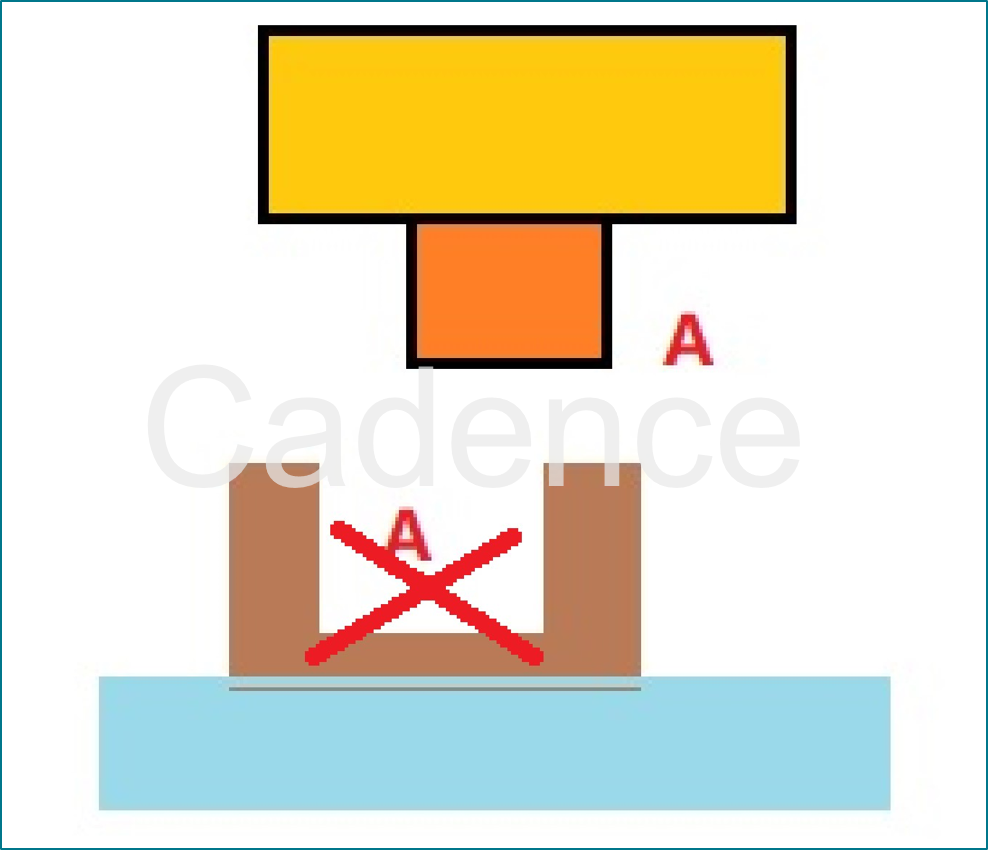

3Bump 丟失 / 多余

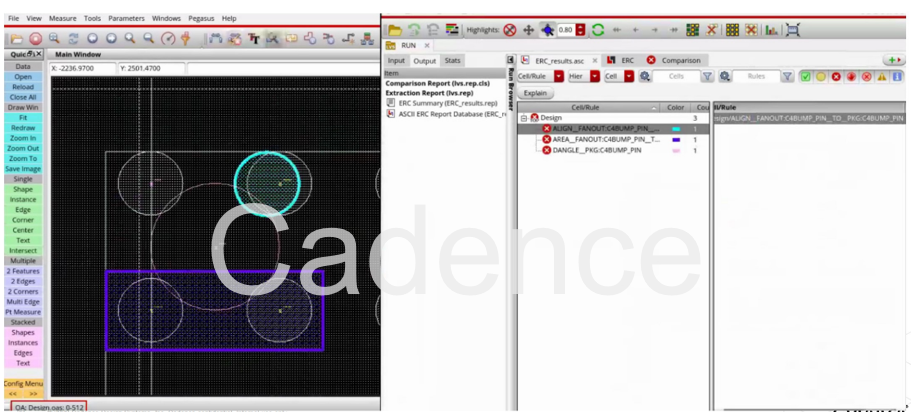

檢查是否有 Dangling 的 Bump。如下圖所示,上面的 Bump 沒有連接到其它任何 Bump 上,那么它就是一個 Dangling Bump,產生的原因有可能是上面的 Bump 多余或者下面丟失對應連接的 Bump。

版圖原理圖一致性檢查 LVS

3D-IC 的 LVS 驗證是多層次、系統性的,需要檢查的項目主要包括:

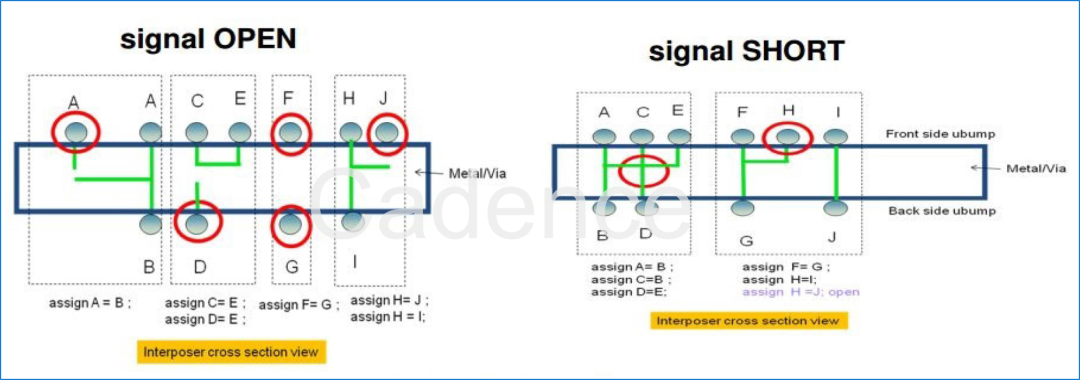

1接觸面的連接性

包括 Bump 開路和 Bump 短路。

2中介層的連接性

2.5D 是將芯片集成在使用 Bump 作為表面連接的中介層上,中介層可以進行重布線和插入 TSV,提高互聯密度。LVS 檢查 Interposer 上表面的 Bump 信號和下表面 Bump 信號連接的正確性與否,包括信號的開路和信號的短路。

3封裝基板的連接性

封裝基板上表面 pin 到封裝下表面 pin 之間的連接性也需要檢查。

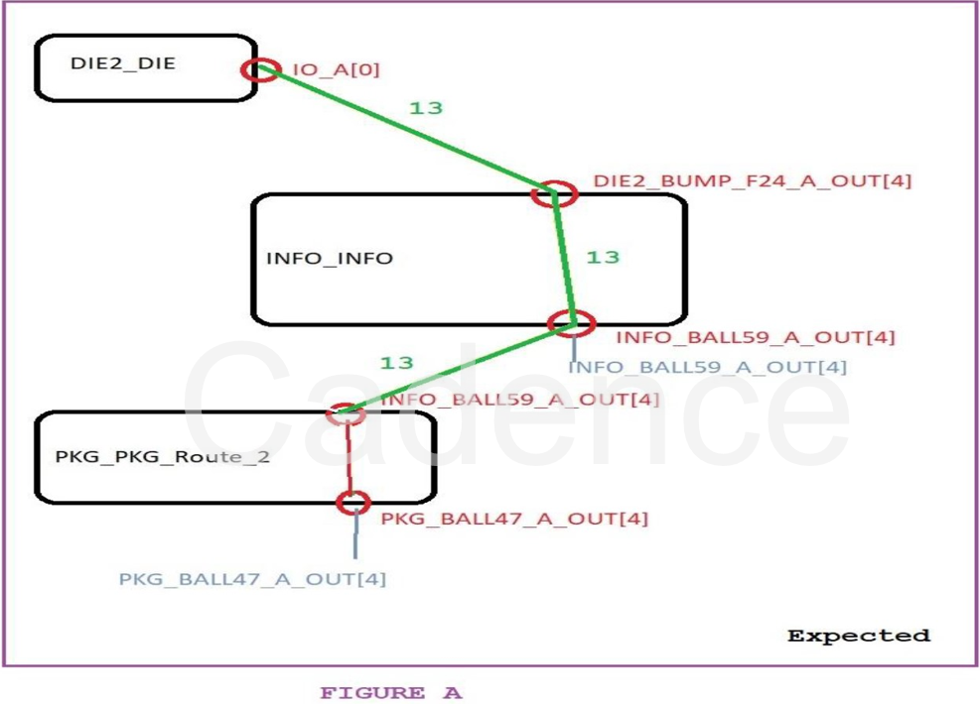

4系統層面的連接性

在系統層面,每個特定功能的芯片的端口的連接不僅要保證邏輯的正確性,并且在物理層面也應該有正確的連接性。

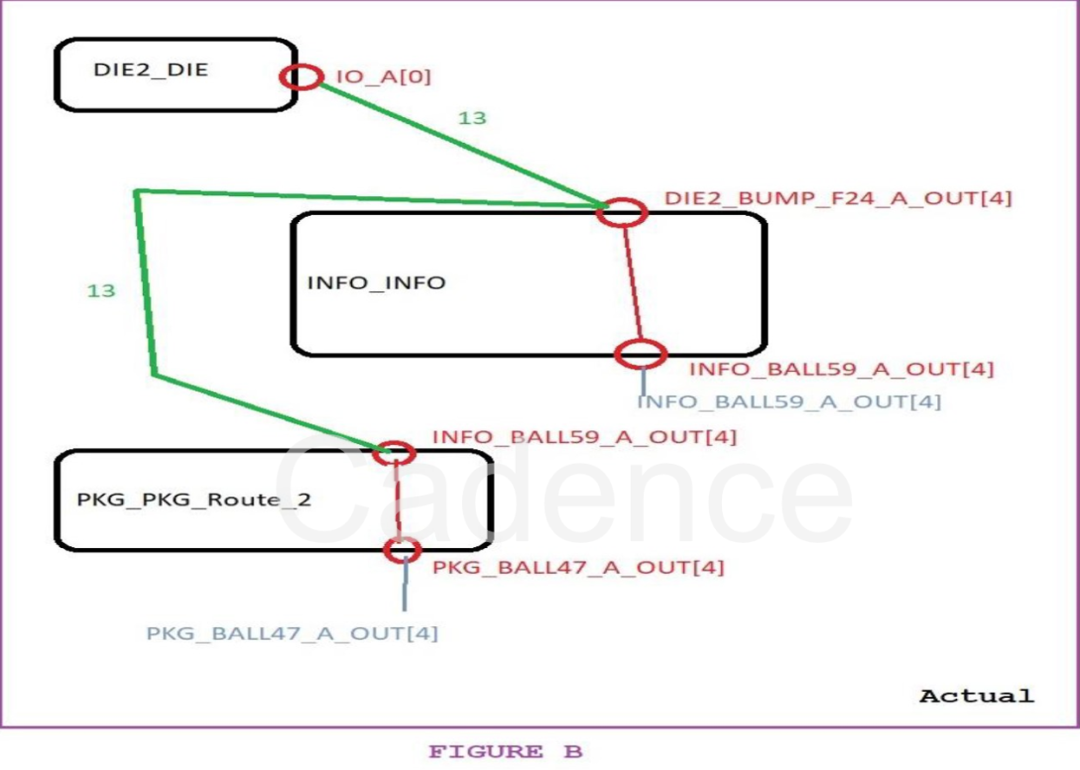

DIE2 的信號端口 IO_A[O] 連接:

IO_A[O] -> DIE2_BUMPF2_F24_A_OUT[4] -> INFO_BALLS9_A_OUT[4](INFO下面端口) -> INFO_BALLS9_A_OUT[4] (封裝上面端口) -> PKG_BALL47_A_OUT[4]

這是正確的物理連接,也是期望的物理連接。

如果發生了這樣的情況:

IO_A[O] -> DIE2_BUMPF2_F24_A_OUT[4] -> INFO_BALLS9_A_OUT[4] (封裝上面端口) -> PKG_BALL47_A_OUT[4]

雖然邏輯上 IO_A[O] 最終連接到了PKG_BALL47_A_OUT[4],但是這并不是期望的物理連接,這種情況下LVS會報告連接性丟失。

了解了物理驗證的這些需求,讓我們來看看 Integrity 3D-IC 平臺 + Pegasus System-LVS 的解決方案如何應對 3D-IC 物理驗證所面臨的這些挑戰:

Integrity 3D-IC 平臺 + Pegasus System-LVS

解決方案

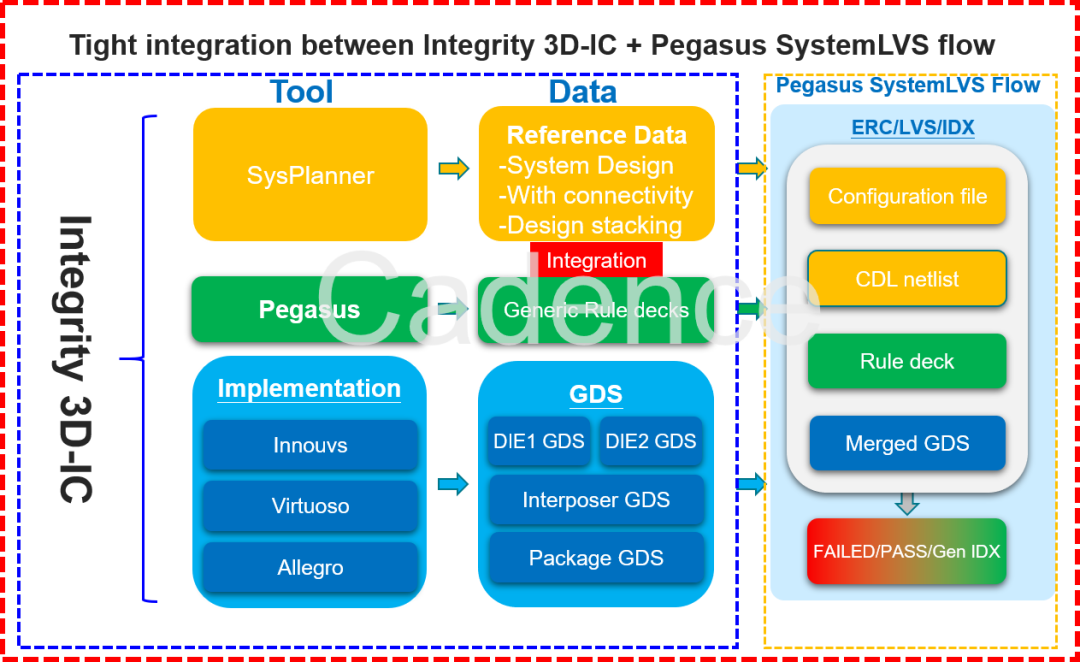

Cadence 的物理驗證工具 Pegasus System-LVS 緊密集成在 Integrity 3D-IC 平臺中:

01可以將不同設計工具的物理數據合并生成一個系統層面的 GDS,進行系統性的 LVS / ERC / DRC 檢查。

02Pegasus System-LVS 不依賴 Foundry 的物理驗證規則,也不需要根據不同 die 的工藝節點,不同的 3D 結構手動定制化物理驗證規則,只要輸入工藝相關的 GDS Layer Map 和 Connection 文件,就可以自動生成物理驗證規則,完成 LVS / ERC / DRC 檢查。

03可以根據用戶的選擇單獨或者同時對某個堆疊層接觸面或者堆疊層進行LVS / ERC / DRC 檢查,也可以生成 IDX(Inter-Die-Xtalk Extraction)數據,可供 RC 抽取使用。

讓我們來看下 Pegasus System-LVS 設計實例:

在 Integrity 3D-IC 平臺中啟動 Pegasus System-LVS 完成物理驗證的操作步驟:

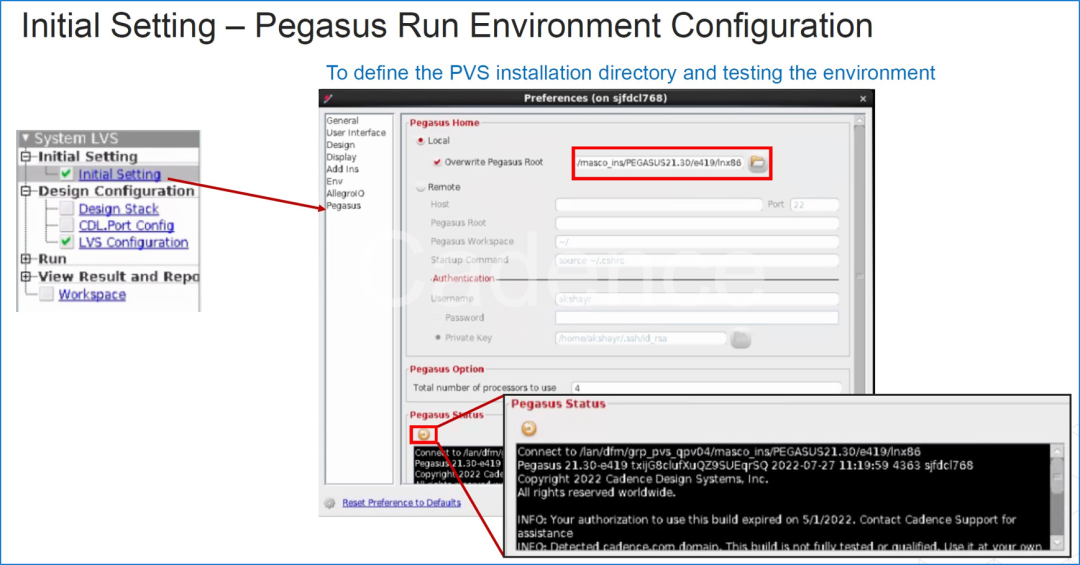

Step1

進行環境初始化時,在 Integrity 3D-IC 平臺可直接啟動 Pegasus 并查看安裝路徑,檢測環境是否正確:

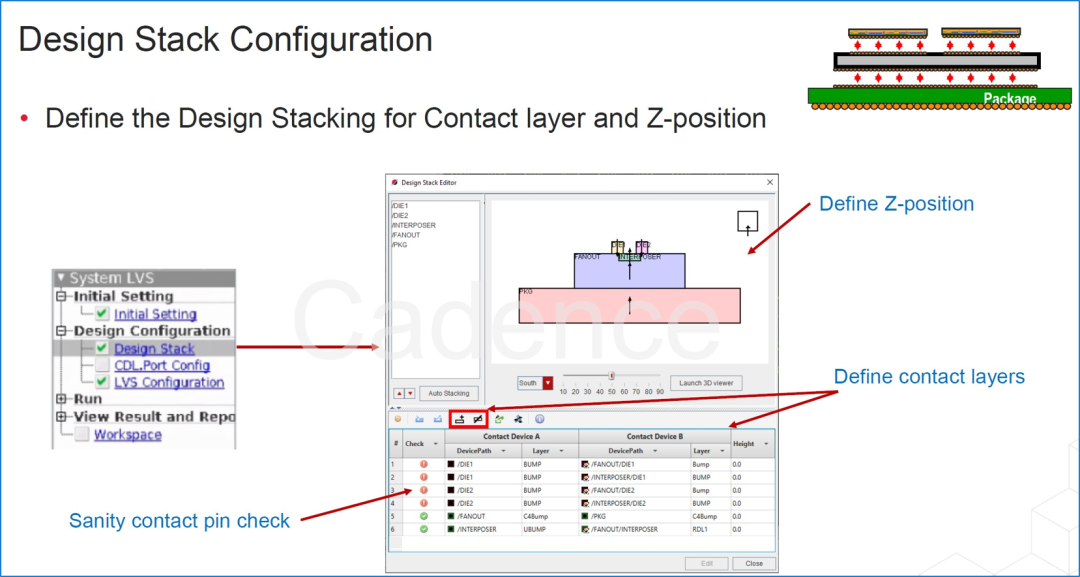

Step2

在 Integrity 3D-IC 平臺中,3D-IC 設計的堆疊結構一目了然。在物理驗證之前,可定義堆疊面的接觸金屬層和堆疊層的位置和朝向:

Step3

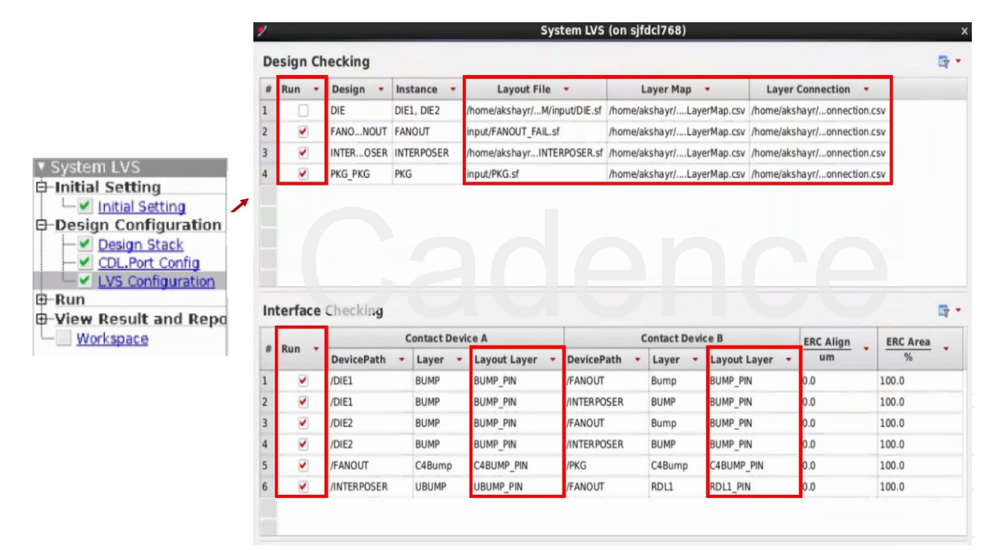

對 Pegasus System-LVS 的配置文件進行設置:

定義 GDS 文件路徑

定義 Layermap / Layerconnect 文件

定義 GDS 的接觸層

選擇其中某個設計模塊或者接觸面進行檢查

Step4

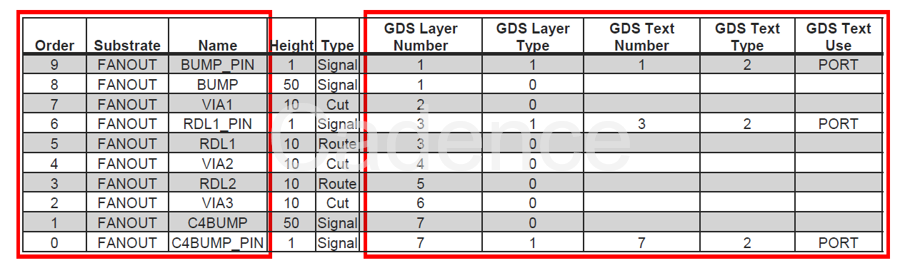

GDS layer 映射文件和連接性文件

Layer 映射文件:

- 定義了設計文件 GDS 中包含的 Layer 名字和 GDS Number 的映射關系。

- 下面紅色圈出的部分需要手工輸入。例如下圖所示:

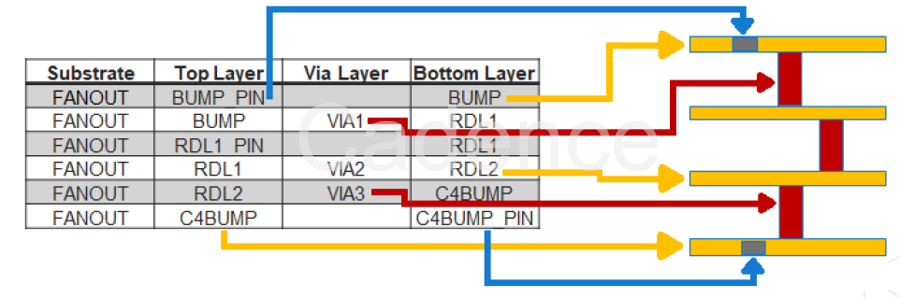

Layer 連接性文件:

- 指定了每個設計中 Layer 之間的連接關系,這些 Layer 需要在 Layer Mapping 文件中有過定義。

- 下圖是一個連接性文件的例子以及實際的物理連接圖:

Step5

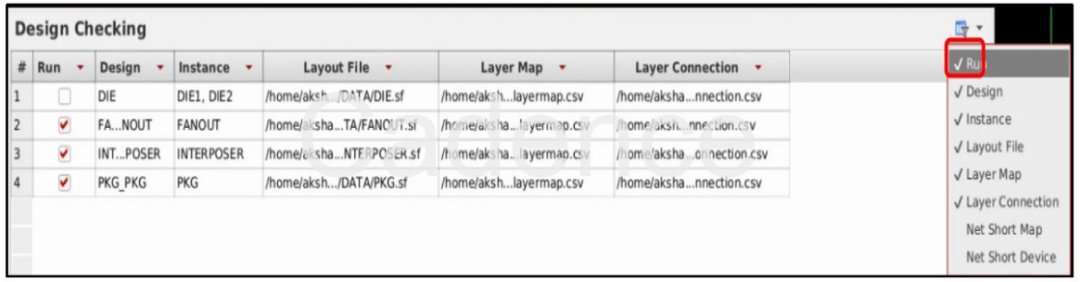

設計檢查和接觸面檢查

設計檢查:

- 在設計檢查部分,用戶可以選擇檢查某個設計模塊或者只檢查 Bump 的連接性。

- 此外,在設計檢查部分除了可以手動輸入例如 Layout File、Layer Map and Layer Connection 之外,還可以通過右上角的過濾按鈕加入其他的輸入文件,比如 Net Short Map 文件等。

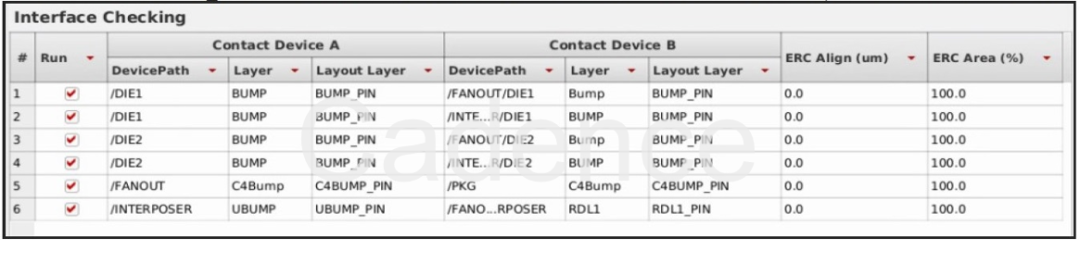

接觸面檢查:

- 在接觸面檢查部分,用戶可以根據設計需要選擇性地檢查某個或者多個接觸面。

- 此外用戶可以控制 ERC 檢查

ERC Align

1. 用戶設置ERC Align的值, 正數表示需要對準的Bump中心間距的最大值。

2. ERC Align的值為負數表示不啟動ERC Align 檢查。

3. 誤差值的單位是微米。

ERC Area

1. 用戶設置ERC Area的值,表示需要對準的Bump面積重合的最小比值。

2. ERC Align的值為0或者大于100表示不啟動ERC Area檢查。

3. 誤差值是面積的比值。

(注意:接觸面檢查部分也有過濾按鈕可以加入或者過濾某些選項。)

Step6

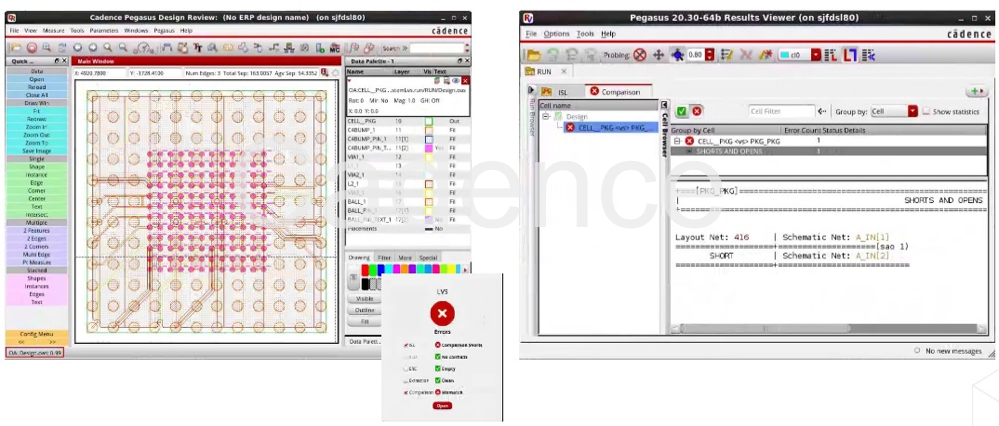

Results Viewer(RV)

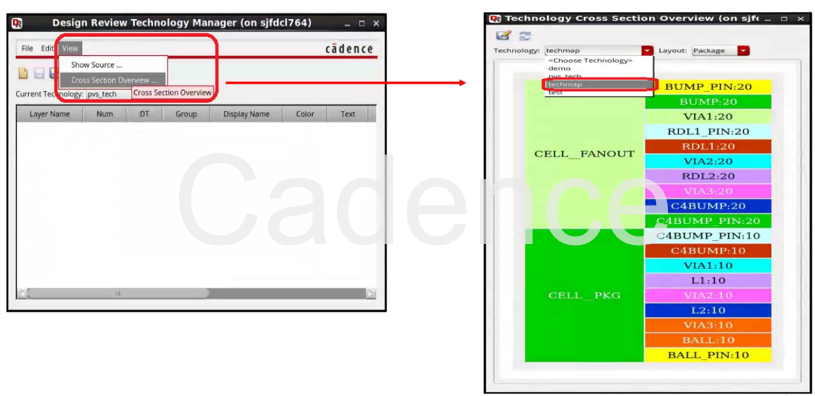

System-LVS 運行完之后 Sysplanner 會自動啟動 Design Review 和 Results Viewer,用戶可以很方便的進行 Probe 和 Debug。

下面左圖是 Design Review,右圖是 LVS Results Viewer:

ERC / DRC Results

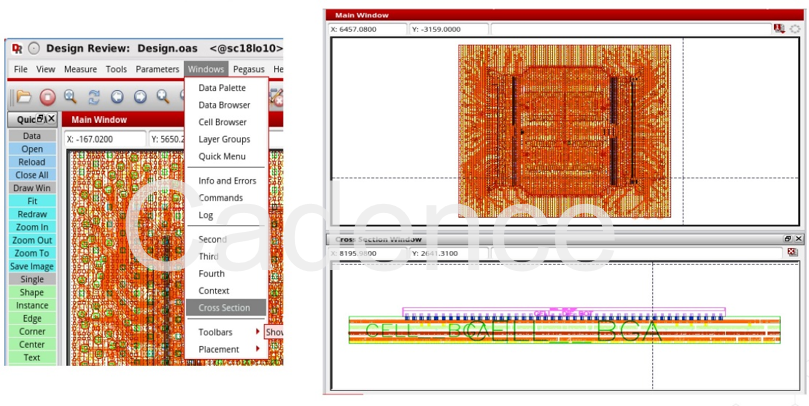

Cross-Section view

System-Stacking view

最后,讓我們總結下 Pegasus System-LVS flow 的優勢:

Pegasus System-LVS 緊密集成在 Integrity 3D-IC 平臺中,用戶可以很方便的對不同設計平臺的數據進行合并和物理驗證。

Pegasus System-LVS 是獨立于 Foundry 的、自動化的系統級物理驗證工具。它不依賴Foundry 的物理驗證規則,也不需要根據不同 die 的工藝定制化物理驗證規則,只需要輸入相應的 GDS Layer Map 和 GDS Connection File 就可以自動生成物理驗證規則完成 LVS / ERC / DRC 驗證。

Pegasus System-LVS 可以生成 IDX 數據供 RC 抽取使用。

用戶可以對多個堆疊層接觸面或者堆疊層同時進行 LVS / ERC / DRC 驗證。

用戶也可以根據不同設計階段的需要,選擇性的檢查某些項目,比如只檢查某兩個堆疊層接觸面的 Pin 連接性,或者整個設計的 LVS / ERC / DRC。

Pegasus System-LVS 也支持輸入晶圓廠的物理驗證規則進行 LVS / ERC / DRC 驗證。

希望 Integrity 3D-IC 平臺能夠方便越來越多工程師的系統設計,加速優秀的芯片產品落地,推動后摩爾時代的發展。

注冊成功且通過 Cadence 審核的用戶可獲得完整版 PPT 資料。審核通過后 Cadence 會將 PPT 發送至您的郵箱,提供您的公司郵箱地址通過審核的幾率更大哦!

Integrity 3D-IC 資料包:

- Cadence Integrity3D-IC 平臺 產品手冊

- Cadence Pegasus 3D-IC LVS / ERC / DRC PPT 介紹

Integrity 3D-IC 介紹:

Cadence Integrity 3D-IC 平臺提供了一個高效的解決方案,用于部署 3D 設計和分析流程,以實現強大的硅堆疊設計。該平臺是 Cadence 數字和簽核產品組合的一部分,支持 Cadence 公司的智能系統設計戰略(Intelligent System Design),旨在實現系統驅動的卓越 SoC 芯片設計。

關于 Cadence

Cadence 在計算軟件領域擁有超過 30 年的專業經驗,是電子系統設計產業的關鍵領導者。基于公司的智能系統設計戰略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計從概念成為現實。Cadence 的客戶遍布全球,皆為最具創新能力的企業,他們向超大規模計算、5G 通訊、汽車、移動設備、航空、消費電子、工業和醫療等最具活力的應用市場交付從芯片、電路板到完整系統的卓越電子產品。Cadence 已連續八年名列美國財富雜志評選的 100 家最適合工作的公司。

審核編輯:湯梓紅

-

原理圖

+關注

關注

1323文章

6414瀏覽量

239524 -

IC

+關注

關注

36文章

6103瀏覽量

178636 -

3D

+關注

關注

9文章

2954瀏覽量

110115 -

IC設計

+關注

關注

38文章

1352瀏覽量

105366 -

Cadence

+關注

關注

67文章

966瀏覽量

143959

原文標題:3D-IC 設計之系統級版圖原理圖一致性檢查

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

對申請CCC認證的產品進行一致性檢查時檢查什么?

MIPI一致性測試

Cadence 憑借突破性的 Integrity 3D-IC 平臺加速系統創新

模擬版圖設計流程相關資料分享

順序一致性和TSO一致性分別是什么?SC和TSO到底哪個好?

一致性規劃研究

汽車產品認證中的一致性檢查

RFID協議一致性測試系統設計(二)

RFID協議一致性測試系統設計(三)

加速器一致性接口

DSA系統的全局一致性需求分析

哈希圖一致性算法已被驗證為異步拜占庭容錯

自主駕駛系統將使用緩存一致性互連IP和非一致性互連IP

RTL與網表的一致性檢查

深入理解數據備份的關鍵原則:應用一致性與崩潰一致性的區別

3D-IC設計之系統級版圖原理圖一致性檢查

3D-IC設計之系統級版圖原理圖一致性檢查

評論