Mailboxes是進程間通信的另一種方式,但是比semaphores更強大,因為Mailboxes可以在兩個進程之間交換消息。

數(shù)據(jù)可以由一個進程發(fā)送,由另一個進程獲取,顧名思義就像是郵箱一樣。

獲取郵箱中信件的方式有兩種:

1、一直等待信件的到來(blocking)

2、如果沒有信件就先去干其他事情,過一會兒再來看是否信件到了。(non-blocking)

從Mailboxes中可以存放信件規(guī)模的角度,Mailboxes可以大致分為bounded Mailboxes和unbounded Mailboxes。

bounded Mailboxes就是指Mailboxes中能夠容納有限數(shù)量的信件,如果在Mailboxes滿時寫入會阻塞住,直到不滿。unbounded Mailboxes可以容納無限數(shù)量的信件。

Mailboxes也可以聲明為只能存放某一類的信件。默認情況下,Mailboxes是無類型的,這意味著Mailboxes可以發(fā)送和接收任何不同類型的信件。

郵箱聲明的語法是:

mailbox mbox;

Mailbox是一個SystemVerilog內置類,自然也提供了許多內置的方法:

1、new ()

創(chuàng)建一個mailbox,函數(shù)原型是:

functionnew()(intbound=0);

會返回一個mailbox句柄,默認bound是0,表示unbounded mailbox。

2、num ()

返回mailbox中信件的個數(shù),函數(shù)原型是:

functionintnum();

3、put ()

blocking put(按照FIFO順序),如果mailbox滿了會阻塞進程,函數(shù)原型是:

task put (singular message)

4、try_put ( )

non-blocking put(按照FIFO順序),如果mailbox滿了不會阻塞進程,會返回值0。函數(shù)原型是:

functiontry_put(singularmessage);

5、get ()

blocking get(按照FIFO順序),如果mailbox是空的,會一直blocking進程。函數(shù)原型是:

taskget(refsingularmessage);

6、try_get ( )

non-blocking get(按照FIFO順序),如果mailbox是空的,不會阻塞進程,會返回值0。函數(shù)原型是:

function int try_get( ) (ref singular expression)

7、peek ( )

peek()不同于get(),peek會復制mailbox中的信件,而不會將信件從mailbox中刪除。函數(shù)原型是:

taskpeek(refsingularmessage);

如果mailbox是空的,會一直block進程。

8、try_peek (),不過多言說,non-block peek。函數(shù)原型是:

function int try_peek ( ref singular expression)

示例:

module mB; bit [7:0] mem [0:3]; int i, j, data; mailbox mbox; //declare a mailbox initial begin mbox = new (4); //create a bounded mailbox fork DMA_write; CPU_read; join end task DMA_write; $display($stime,,, "DMA puts Mem Data into mbox"); for (i=0; i < 4; i++) begin mem[i] = $urandom; $display($stime,,, "DMA WRITE[%0d] = %0d",i,mem[i]); mbox.put(mem[i]); //put data into the mailbox end endtask task CPU_read; $display($stime,,, "CPU retrieves Mem Data from mbox"); for (j=0; j < 4; j++) begin mbox.get(data); //retrieve data from the mailbox $display($stime,,, "CPU READ[%0d] = %0d",i,data); end endtask endmodule

仿真log:

0 DMA puts Mem Data into mbox 0 DMA WRITE[0] = 36 0 DMA WRITE[1] = 129 0 DMA WRITE[2] = 9 0 DMA WRITE[3] = 99 0 CPU retrieves Mem Data from mbox 0 CPU READ[0] = 36 0 CPU READ[1] = 129 0 CPU READ[2] = 9 0 CPU READ[3] = 99 V C S S i m u l a t i o n R e p o r t

上面這個例子首先聲明了一個mailbox “mbox”,然后例化深度為4。

后面兩個并行的進程“DMA_write”和“CPU_read” 。從打印log來看并不存在兩個進程之間的沖突。

參數(shù)化Mailbox

如果希望在mailbox put和get時進行類型檢查,可以顯式地聲明mailbox的類型。

module pMailbox; typedef mailbox #(string) string_mbox; string s; initial begin static string_mbox SMbox = new; s = "hi"; SMbox.put( s ); $display("String 'put' is %s", s); SMbox.get( s ); $display("String 'get' is %s", s); end endmodule

仿真log:

String 'put' is hi String 'get' is hi

審核編輯:湯梓紅

-

Verilog

+關注

關注

29文章

1366瀏覽量

111998 -

System

+關注

關注

0文章

166瀏覽量

37645 -

進程

+關注

關注

0文章

207瀏覽量

14241

原文標題:System Verilog中的Mailboxes

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

Modelsim XE是否支持System Verilog

System Verilog常見問題及語言參考手冊規(guī)范

System Verilog問題和語言參考手冊規(guī)范

Verilog Digital System Design

VHDL,Verilog,System verilog比較

基于System Verilog的可重用驗證平臺設計及驗證結果分析

FPGA CPLD中的Verilog設計小技巧

System Verilog與verilog的對比

學會這些System Verilog方法,芯片驗證入門沒問題

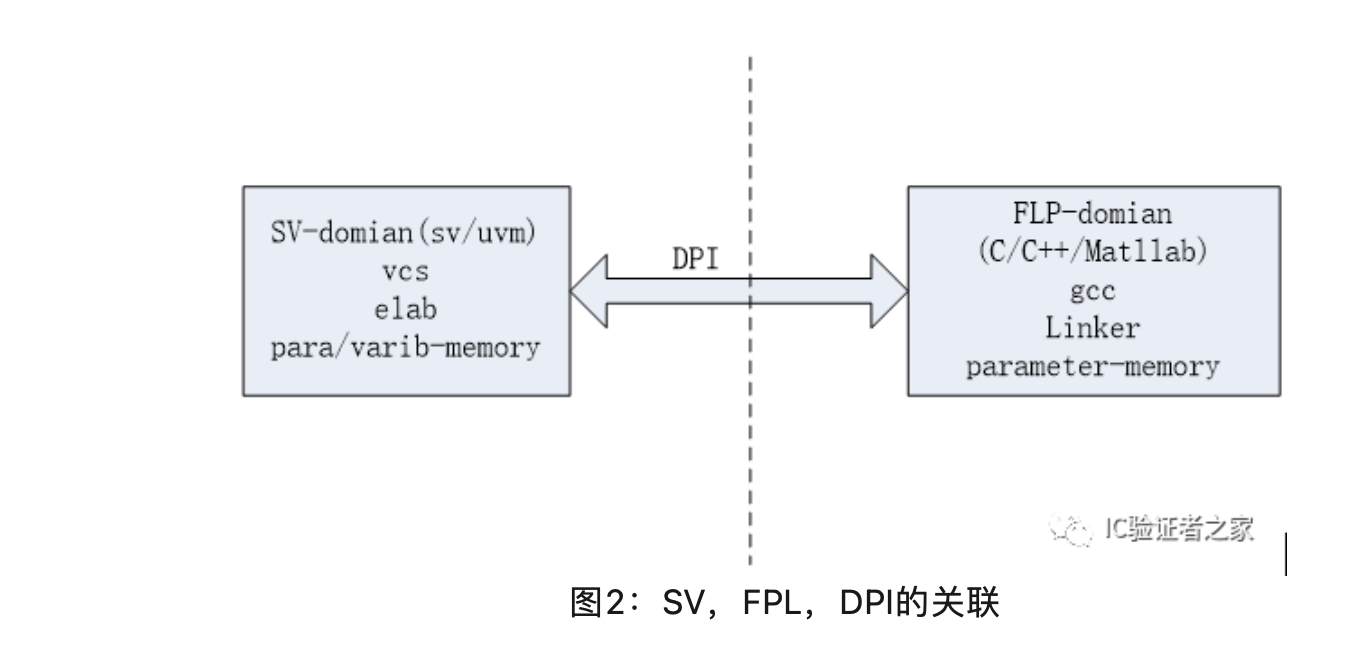

淺談System Verilog的DPI機制

談談Verilog/System Verilog和C的幾種交互模式

System Verilog中的Mailboxes

System Verilog中的Mailboxes

評論