本應用筆記介紹了如何利用 FPGA 系列的專用 I/O 功能,將具有高速并行低壓差分信號 (LVDS) 輸入的 LTC2000、16 位、2.5GSPS 數模轉換器 (DAC) 連接至 ALTERA STRATIX IV FPGA。

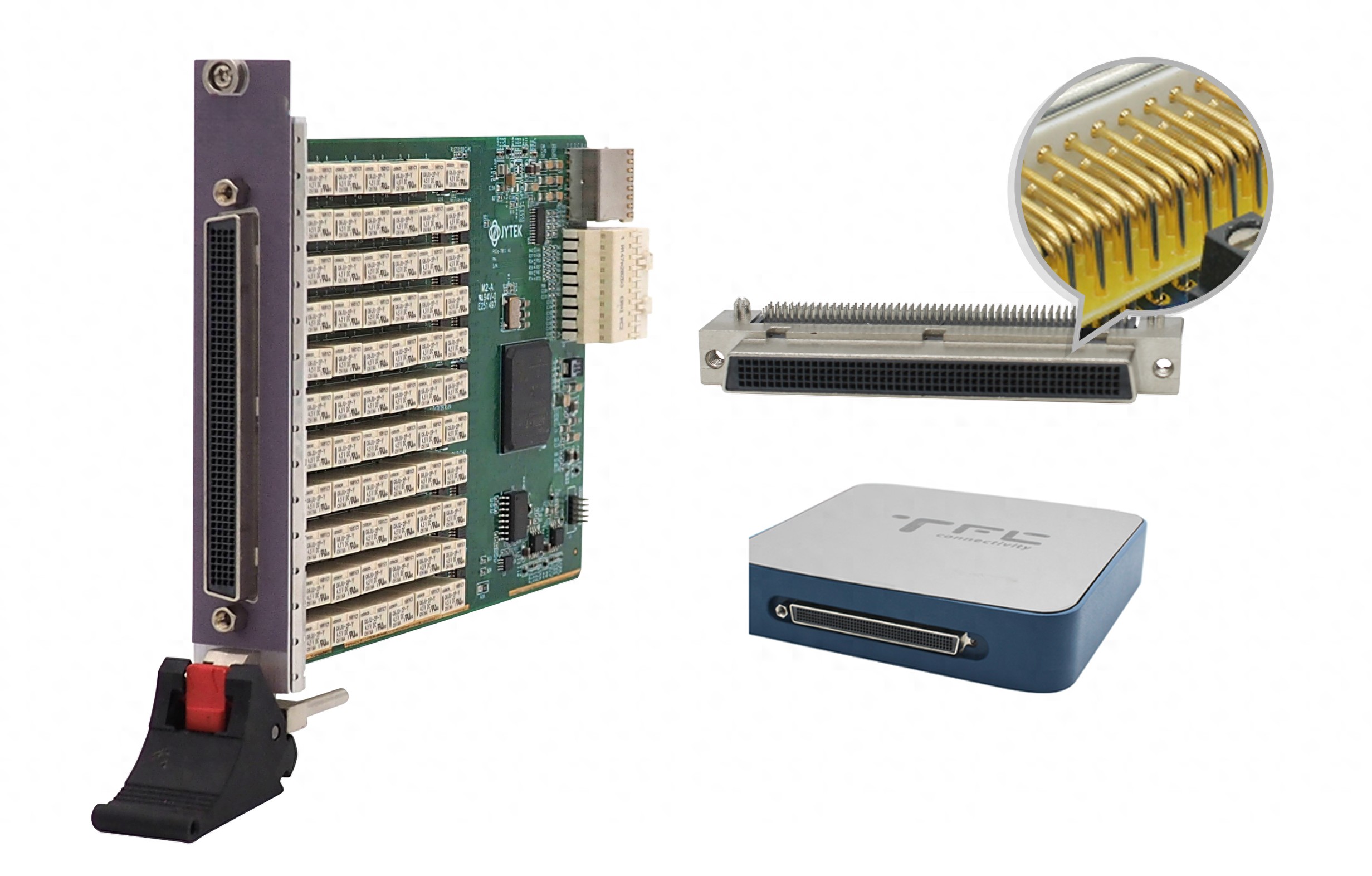

系統硬件包括一個DC2085A LTC2000評估板和一個DK-DEV-4SGX230NSTRAIX IV GX開發板。

來自主機PC的簡單軟件界面用于配置硬件和加載數據模式。DAC數據模式存儲在外部雙倍數據速率III型同步動態隨機存取存儲器(DDR3)中,最大模式深度為256兆采樣,便于評估非常復雜的模擬波形。

LTDACgen 是一個圖形程序,可生成正弦和擴頻模式,以便使用此參考設計評估 LTC2000。LinearLabTools 允許從 Matlab 或 Python 直接控制此參考設計,允許客戶使用自己的數據模式進行測試,并將其他儀器納入評估過程。

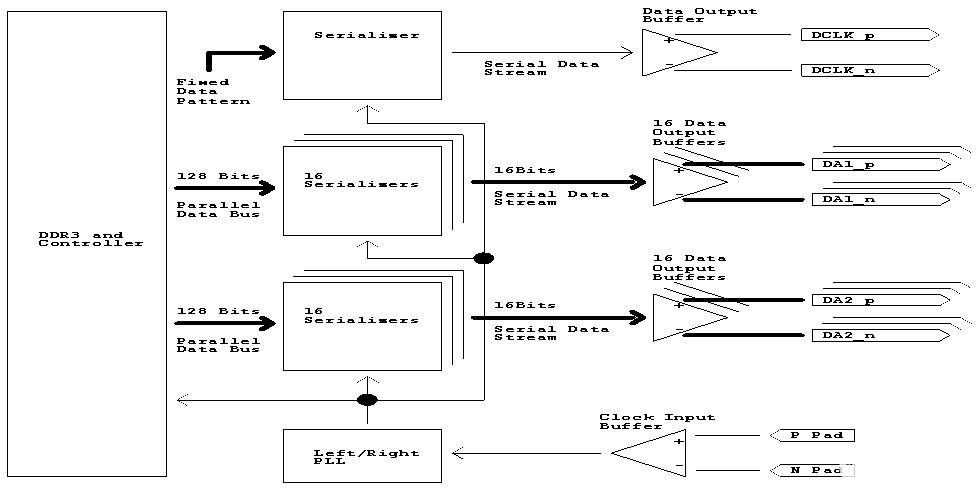

LTC2000 的數字接口由兩個 16 位 LVDS 數據流組成,每個數據流支持高達 1250 MSPS 的數據速率和 625 MHz DDR 時鐘。

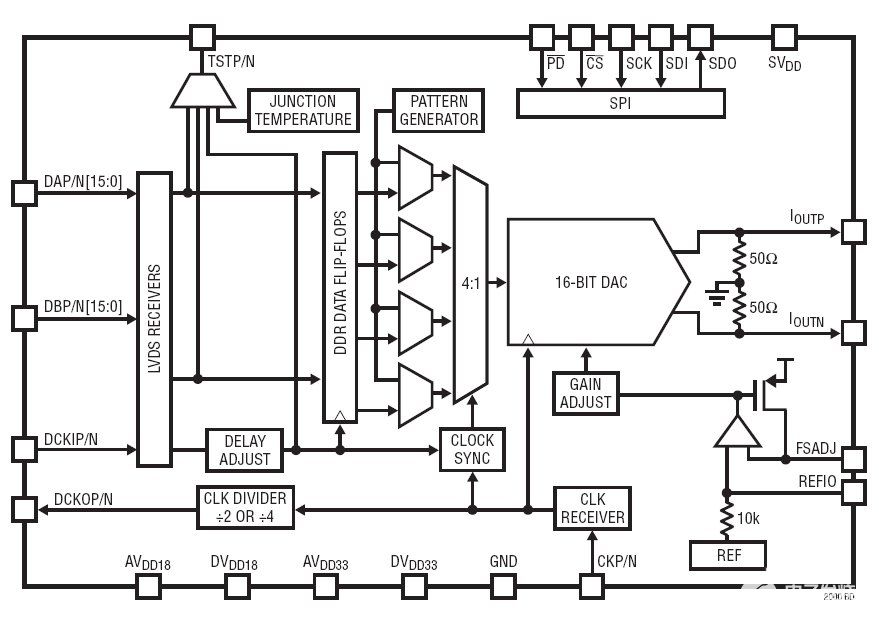

圖 1:LTC2000 框圖

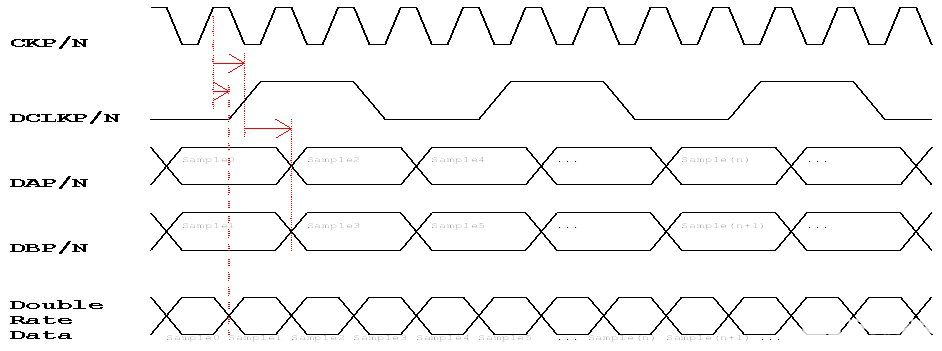

CK是直接控制DAC輸出更新的轉換時鐘。LTC2000 包含一個可編程時鐘分頻器和 LVDS 發送器,后者提供了一個分頻版本 (f)CK/2或 fCK/4) 的 CK在主機 FPGA 或 ASIC 使用的 DCKO 引腳上。DCKI是DDR數據時鐘輸入。由DCKI計時的兩個16位數據總線由CK時鐘的多路復用器組合成單個16位雙倍速率數據流,然后將其轉換為模擬信號。有關更多詳細信息,請參閱 LTC2000 的產品手冊。

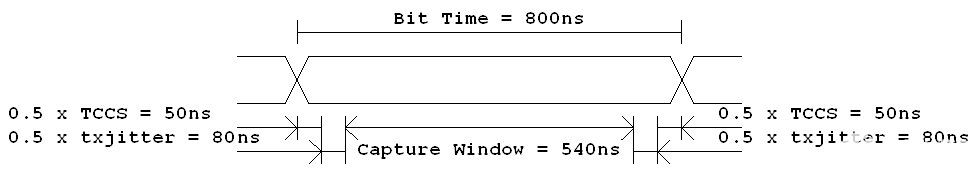

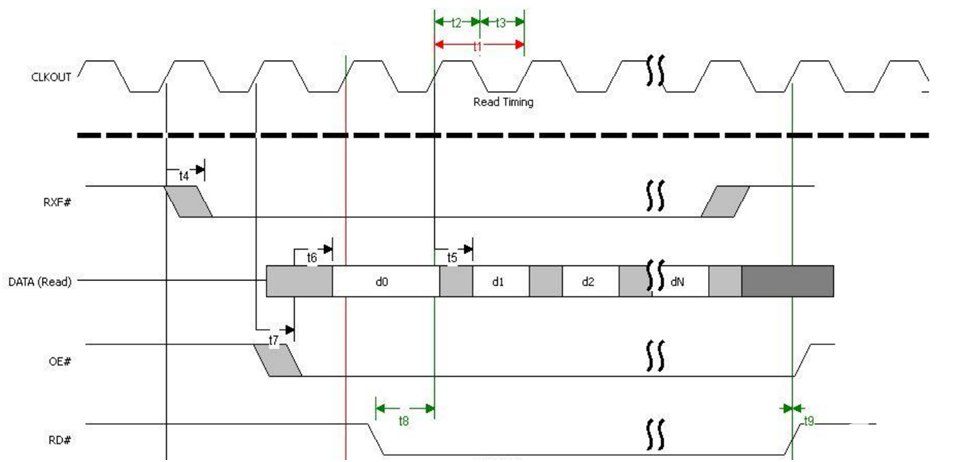

圖 2:LTC2000 接口時序圖

表1總結了時鐘發生器和FPGA的要求。

| 信號名稱 | 速度要求(最大) | 源 |

| CK | 2.5千兆赫 | 外部超低抖動/噪聲時鐘發生器 |

| 德利克 | 625兆赫 | FPGA |

| 大 | 1250兆秒 | FPGA |

| .DB | 1250兆秒 | FPGA |

| 雙倍速率數據流 | 2.5GSPS | 內部 LTC2000 |

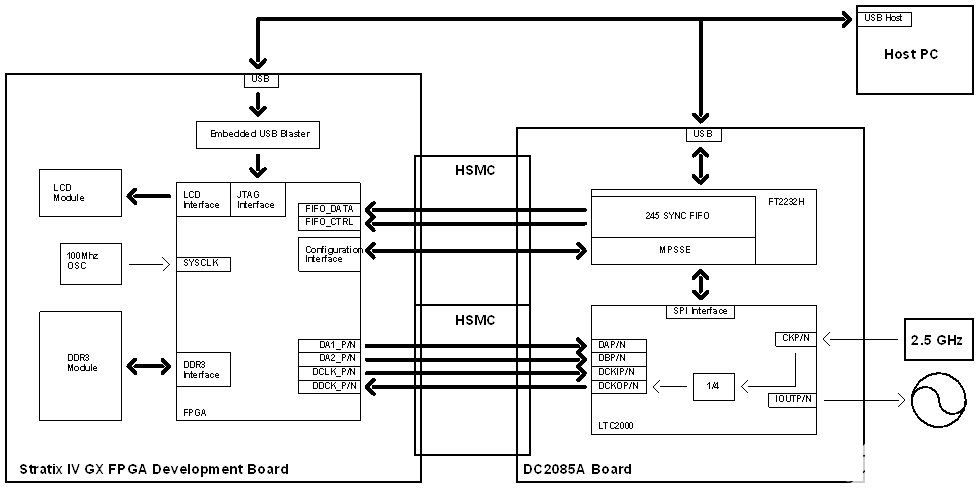

演示系統架構

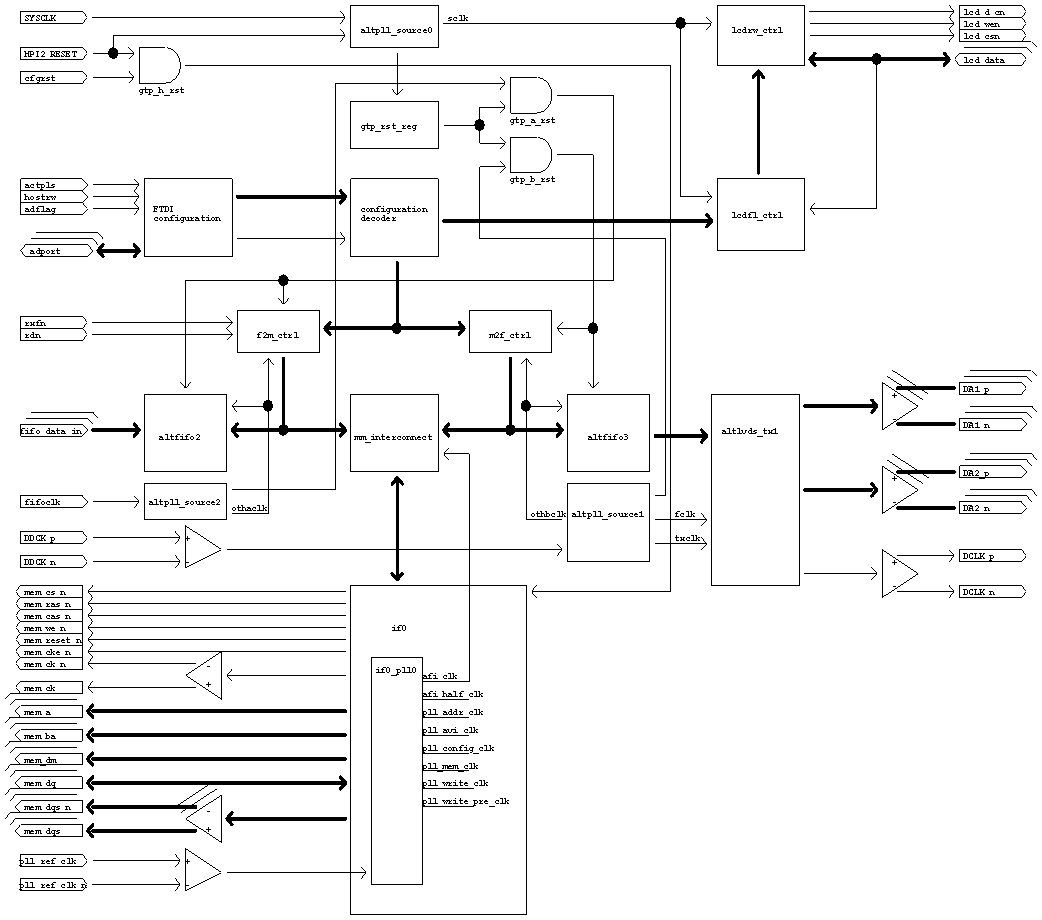

STRATIX IV GX FPGA 開發板為低功耗、高性能和邏輯密集型設計的開發和原型設計提供了一個硬件平臺。該板包含一個STRATIX IV GX FPGA EP4SGX230KF40(BGA 1517引腳),具有64位數據總線的512MBDDR3 SDRAM和具有16位數據總線的128MBDDR3 SDRAM。它還提供了廣泛的外圍設備和接口,以促進開發。由于FPGA設計對于此應用非常簡單,因此器件和電路板使用率非常低。

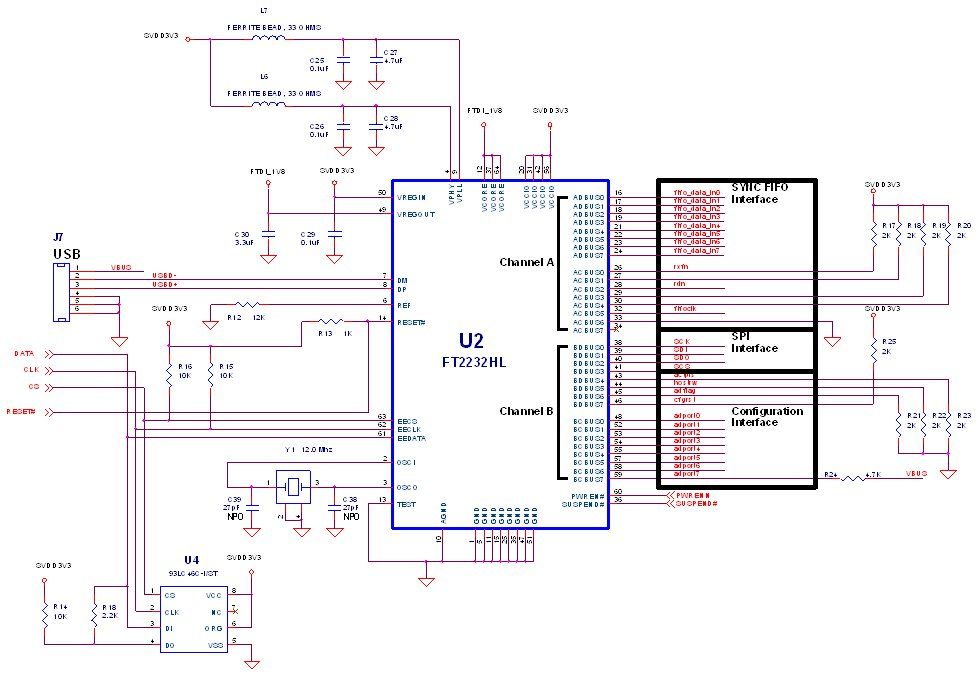

DC2085A 板包含 LTC2000、允許使用單 5V 電源的電源管理電路,以及一個提供用于數據傳輸和控制的 USB 接口的 FT2232H。FT2232是一款USB 2.0高速(480Mbps)控制器,可配置為雙多協議同步串行引擎(MPSSE)模式或單高速同步FIFO模式。在 MPSSE 模式下,FT2232 的通道 B 實施了一個用于配置 LTC2000 的 SPI 接口。

LTC2000 需要施加到 CK 輸入的低抖動 2.5GHz (MAX) 時鐘。DC2085A 板通過兩個高速夾層卡 (HSMC) 連接器與 FPGA 板配接。這些連接器承載來自 LTC2000 的 DCKO、兩個 16 位數據流 (DA、DB) 和由 FPGA 生成的 DCKI 數據捕獲時鐘。DCKO 用作主 FPGA 時鐘,內部分頻器設置為雙端口模式的 4 分頻。所有高速信號都是LVDS,使用HSMC連接器的TX側。多個HSMC RX信號配置為CMOS GPIO,連接到8位FT2232同步FIFO端口,主機通過該端口上傳DAC碼型數據。

FPGA 設計還控制 FPGA 板附帶的 LCD 模塊。它顯示緩沖區大小配置、FPGA 狀態和當前操作模式。LCD電路位于專用時鐘域SYSCLK上,該時鐘域來自100MHz板載振蕩器。

FPGA位文件通過嵌入式“USB沖擊波”JTAG適配器上傳。位文件也可以加載到配置 EEPROM 中,該 EEPROM 在上電時加載 FPGA。

圖 3:演示系統架構

STRATIX IV FPGA 的 I/O 架構

STRATIX 4 GX器件具有內置串行器/解串器(SERDES)電路,支持數據速率高達1.6Gbps的高速LVDS接口。引腳分配對于 STRATIX IV FPGA LVDS 應用非常重要,因為只有部分 I/O 模塊支持完整的 LVDS 功能,只有部分 PLL 支持這些 I/O。STRATIX IV 器件系列支持行和列 I/O 組上的 LVDS。

柱輸出緩沖器(位于頂部和底部)是單端的,需要外部端接方案來支持LVDS。

行輸出緩沖器(位于左側和右側)是真正的LVD,只有位于左側和右側的PLL支持這些IO。

專用的SERDES電路在行I/O組上實現,以進一步增強器件中的LVDS接口性能。對于列 I/O 組,SERDES 在核心邏輯中實現,因為列 I/O 組上沒有專用的 SERDES 電路。只有真正的LVDS緩沖器和SERDES才能用于此應用。SERDES電路中包含以下專用組件:

差分 I/O 緩沖器

發射器串行器

接收器解串器

數據重新對齊

DPA(動態相位對準)

同步器(先進先出緩沖器)

鎖相環 (PLL)(位于器件的左側和右側)

真正的差分 I/O 緩沖區的方向不可配置。特定引腳僅支持單向數據流。

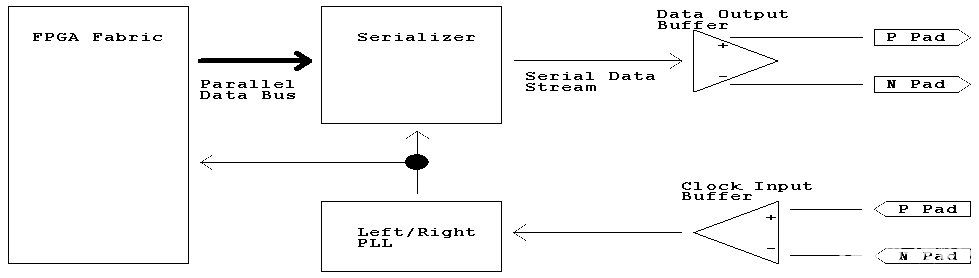

圖 4:STRATIX IV 差分變送器

此應用僅使用差分變送器。其專用電路由差分緩沖器和串行器組成。時鐘源來自左右PLL。差分輸出緩沖器可以驅動LVDS、微型LVDS和RSDS信號電平。串行器從FPGA結構中獲取多達10位寬的并行數據,將其時鐘輸入負載寄存器,并在將數據發送到差分緩沖器之前,使用左右PLL時鐘的移位寄存器對其進行序列化。首先傳輸并行數據的MSB。

Quartus 軟件可以設置 ×3、×4、×6、×7、×8 或×10 的序列化因子以及 SDR 和 DDR 模式。

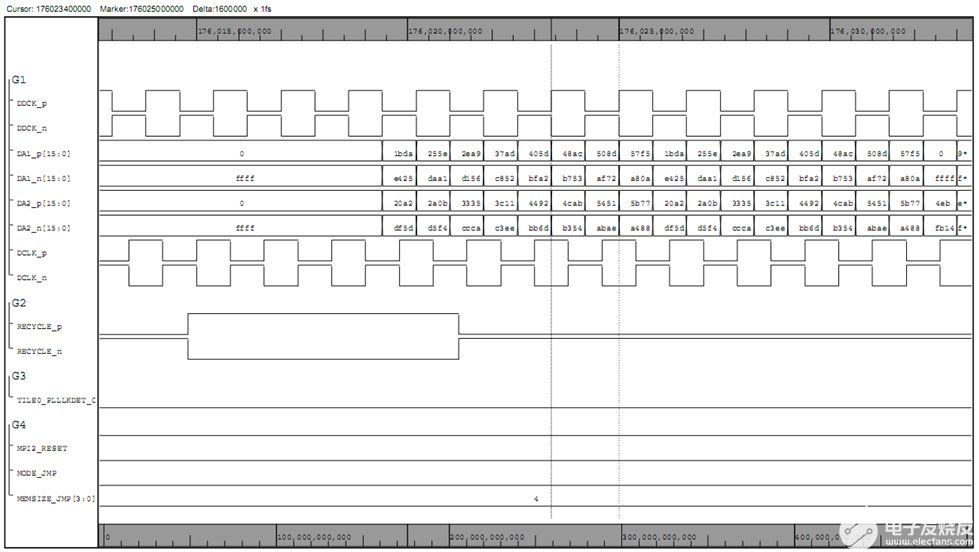

包含 DAC 數據的 DDR3 存儲器驅動慢速、易于約束的 256 位寬數據總線。FIFO處理存儲器和LVDS發送器之間的時鐘域交叉。發射器模塊將并行數據總線串行化為32個超高速數據流,如圖5所示。由于所有串行器都由一個PLL計時,因此會產生一個非常高速的32位并行數據總線。具有恒定并行輸入的附加串行器可生成可調DAC數據輸入時鐘DCKI,并與數據流完美對齊。

圖 5:LTC2000 FPGA 設計中的差分發射器

如表1和圖5所示,如果輸出數據流為1.25Gbps,則來自存儲器的并行總線只需要1.25G/8 = 156.25MHz時鐘。如果使用 64 位寬、533MHz 雙倍數據速率 DDR3 模塊作為 DAC 數據存儲,則輸出總線 256 位 Avalon-MM 總線的工作時鐘可能會將速度降至 266.5MHhz。一個簡單的FIFO電路可以將Avalon-MM總線轉換為連接到差分發射器輸入端口的相同寬度的156.25MHz并行總線。現在,超高速部件僅由FPGA專用SERDES模塊處理。唯一關鍵的時序問題是32位輸出數據流時序偏差。雖然I/O模塊中沒有用于真正的LVDS輸出緩沖器偏斜調整的可編程延遲元件,但STRATIX聲稱通道間偏斜(TCCS)小于100ps:由同一PLL驅動的通道上最快和最慢輸出邊沿之間的時序差,包括時鐘變化和時鐘偏斜。數據速率從600Mbps到1.6Gbps的總抖動(txjitter)小于160ps。因此,如果我們完美地處理PCB走線匹配,1.25Gbps的數據采集窗口應如圖6所示。有關更多詳細信息,請參閱 http://www.altera.com/literature/hb/stratix-iv/stx4_siv54001.pdf。

圖 6:數據流捕獲窗口

STRATIX IV GX FPGA 開發板提供兩個 DDR3 模塊,512 MB DDR3 SDRAM,底部端口(Bank 3)上帶有 64 位數據總線,128 MB DDR3 SDRAM 具有位于頂部端口的 16 位數據總線(Bank 8)。如果在頂部端口上使用 DDR3,則 64 位 Avalon-MM 總線沒有足夠的帶寬來擴展到 256 位/156.26MHz 本地并行總線。因此,512 MB DDR3 模塊是唯一的選擇。

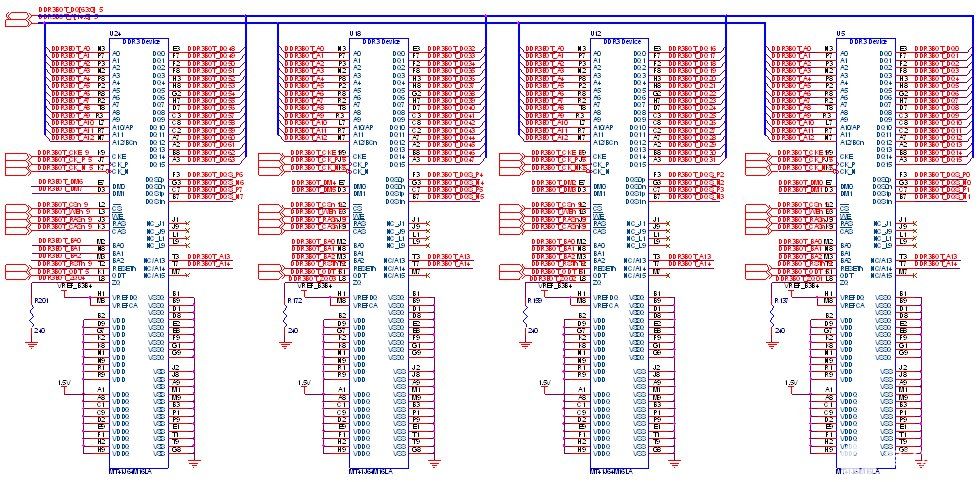

圖 7:512MB DDR3 底部端口組織

DDR3 底部端口由四個 DDR3 設備美光 MT41J64M16LA-15E 組成,提供具有 64 位數據總線的單個 512 MB 接口。有關特定美光 DDR3 SDRAM 的詳細信息,請參閱 http://www.micron.com/products/dram/ddr3-sdram#fullPart&236=0。

該內存接口設計為在 300MHz(DDR3 的最低頻率)和 533MHz 之間運行,最大理論帶寬超過 68.2GBps。FPGA 中的內部總線在全速率或半速率時通常分別為寬度的 2 倍或 4 倍。對于此應用,533MHz 64 位接口將變為 266.5MHz 256 位總線。

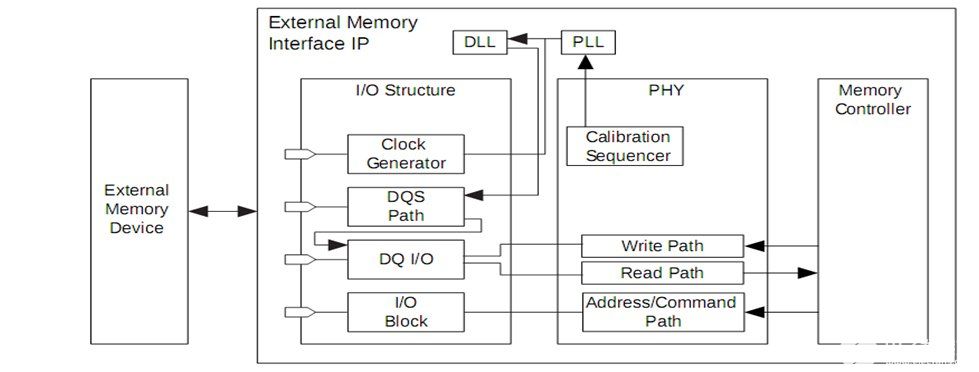

ALTERA FPGA 通過特定的 DDR3 接口 IP 實現最佳的 DDR3 接口性能。該 IP 提供以下組件:

物理層接口 (UniPHY),用于構建數據路徑并管理FPGA和外部DDR3設備之間的定時傳輸。

DDR3 控制器 (HPCII),實現所有 DDR3 命令和協議級要求。

圖 8:ALTERA DDR3 控制器和 UniPHY IP 框圖

FT2232H 雙通道 USB 控制器

DC2085A 板包含一個 FTDI 雙通道 USB 控制器 FT2232,用于從主機上傳 DAC 數據并配置 LTC2000。FT2232設置為同步FIFO模式以上傳數據。傳輸速率高達25MB/秒,通過帶有少量握手信號的8位寬總線。只有通道A可以配置為FT245式同步FIFO接口。設置此模式時,使用的引腳和信號說明如表2所示。在此模式下,通道 B 不可用,因為所有資源都已切換到通道 A。數據在 CLKOUT 的上升沿讀取。

表 2:FT2232 同步 FIFO 接口說明

| 信號名稱 | 方向 | 同步先進先出接口說明 |

| ADBUS[7:0] | 雙向 | D7 到 D0 雙向 FIFO 數據。此總線在此應用程序中配置為輸出 |

| RXF# | 輸出 | 如果為高,則不要從 FIFO 讀取數據。當較低時,FIFO 中有可用的數據,可以通過將 RD# 驅動為低電平來讀取這些數據。在同步模式下,當 RXF# 和 RD# 都處于低電平時,每個時鐘上傳輸數據 |

| 研發# | 輸入 | 允許將當前 FIFO 數據字節驅動到 D0...當 RD# 變為低電平時為 D7。在每個 CLKOUT 周期從接收 FIFO 緩沖區獲取下一個 FIFO 數據字節(如果可用),直到 RD# 變為高電平。 |

| 克利庫特 | 輸出 | 由芯片驅動的60MHz時鐘。所有信號都應同步到此時鐘。 |

圖 9:FT2232H 同步 FIFO 接口時序圖

表 3:FT2232 同步 FIFO 接口信號時序

| 名字 | 最低 | 典型 | 最大 | 單位 | 描述 |

| T1 | 16.67 | 納 | CLKOUT時期 | ||

| T2 | 7.5 | 8.33 | 納 | CLKOUT高期 | |

| T3 | 7.5 | 8.33 | 納 | CLKOUT低谷期 | |

| T4 | 1 | 7.15 | 納 | CLKOUT 到 RXF# | |

| T5 | 1 | 7.15 | 納 | 用于讀取有效數據的 CLKOUT | |

| T6 | 1 | 7.15 | 納 | OE# 讀取數據有效 | |

| T7 | 1 | 7.15 | 納 | CLKOUT 到 OE# | |

| T8 | 11 | 納 | 到 CLKOUT 的 RD# 設置時間(RD# 低后 OE# 低) | ||

| T9 | 0 | 納 | RD# 保持時間 |

為了配置 LTC2000 和 FPGA,FT2232 的通道 B 必須設置為多協議同步串行引擎 (MPSSE) 模式。MPSSE可以獨立配置為許多行業標準串行接口協議,如JTAG,I2C 或 SPI,或者可用于實現專有總線協議。對于此應用程序,它被設置為SPI和GPIO接口和端口。

FPGA 設計

圖 10:FPGA 設計框圖

下表列出了頂級端口說明。

表 4:DDR3 接口

| 信號名稱 | 方向 | 描述 |

| pll_ref_clk | 差分輸入 | DDR3 控制器和 UniFHY 參考時鐘輸入 |

| mem_a | 輸出 | 行地址 |

| mem_ba | 輸出 | 銀行地址 |

| mem_ck | 差分輸出 | 提供給外部 DDR3 的時鐘 |

| mem_cke | 輸出 | 時鐘使能 |

| mem_cs_n | 輸出 | 芯片選擇 |

| mem_ras_n | 輸出 | 行地址可用 |

| mem_cas_n | 輸出 | 列地址可用 |

| mem_we_n | 輸出 | 寫啟用 |

| mem_dm | 輸出 | DDR3 輸入數據掩碼 |

| mem_reset_n | 輸出 | 重置 DDR3 |

| mem_dq | 雙向 | 數據總線 |

| mem_dqs | 差分雙向 | 數據選通 |

| mem_odt | 輸出 | 啟用 DDR3 片上端接 |

| mem_rdp | 輸入 | FPGA 片上端接輸入 |

| mem_rdn | 輸入 | FPGA 片上端接輸入 |

表 5:系統控制界面

| 信號名稱 | 方向 | 描述 |

| 系統CLK | 差分輸入 | 系統時鐘輸入 |

| MPI2_RESET | 輸入 | 按鈕復位輸入 |

| 達普德 | 輸出 | DAC 關斷控制 |

表 6:配置界面

| 信號名稱 | 方向 | 描述 |

| lcd_d_cn | 輸出 | 液晶屏數據或命令選擇 |

| lcd_wen | 輸出 | 液晶屏寫啟用 |

| lcd_csn | 輸出 | 液晶芯片選擇 |

| lcd_data | 雙向 | 液晶數據總線 |

表 7:配置界面

| 信號名稱 | 方向 | 描述 |

| 菲福克 | 輸入 | FT2232 先進先出時鐘輸入。它將通過HSMC連接到表8中的CLKOUT |

| RXFN | 輸入 | 提供先進先出數據。它將通過 HSMC 連接到表 8 中的 RXF# |

| RDN | 輸出 | 讀取啟用。它將通過 HSMC 連接到表 8 中的 RD# |

| fifo_data_in | 輸入 | DAC轉換數據輸入端口。它將通過 HSMC 連接到表 8 中的 ADBUS[7:0] |

| 行動 | 輸入 | FT2232通道B GPIO產生的脈沖。以下所有信號將被上升沿鎖存 |

| 霍斯特魯 | 輸入 | FT2232通道B GPIO生成的讀/寫選擇 |

| 廣告標志 | 輸入 | FT2232通道B GPIO生成的地址/數據選擇 |

| CFGRST | 輸入 | FT2232 通道 B GPIO 生成的配置復位輸入 |

| 廣告端口 | 雙向 | 由FT2232通道B GPIO實現的8位配置數據/地址端口 |

表 8:LTC2000 接口

| 信號名稱 | 方向 | 描述 |

| DDCK | 差分輸入 | LTC2000 參考時鐘輸入 |

| 德利克 | 差分輸出 | 數據采集時鐘 |

| 伊普 | 差分輸入 | 16 位數據流 |

| 大通 | 差分輸入 | 16 位數據流 |

下表列出了設計中的主要時鐘域。

表 9:FPGA 時鐘樹

| 時鐘源 | 頻率 | 鎖 相 環 | 生成的時鐘 | 裝載 | 生成時鐘的頻率 |

| DDCK | 625兆赫 | altpll_source1 | 福克爾克 | altlvds_tx1 | 1.25千兆赫 |

| TXCLK | altlvds_tx1 | 625兆赫 | |||

| 其他 | m2f_ctrl, altfifo3 | 625兆赫 | |||

| 系統CLK | 100兆赫 | altpll_source0 | 渣滓 | lcdrw_ctrl, lcdfl_ctrl | 500kKHz |

| 菲福克 | 60兆赫 | altpll_source2 | 奧塔克爾克 | f2m_ctrl, altfifo2 | 60兆赫 |

| pll_ref_clk | 100兆赫 | altpll_source1If0_pll0 |

afi_clk、 afi_half、 pll_addr_clk、 pll_avi_clk、 pll_config_clk、 pll_mem_clk、 pll_write_clk pll_write_pre_clk |

Mm_intererconnect,if0 | 266.5兆赫 |

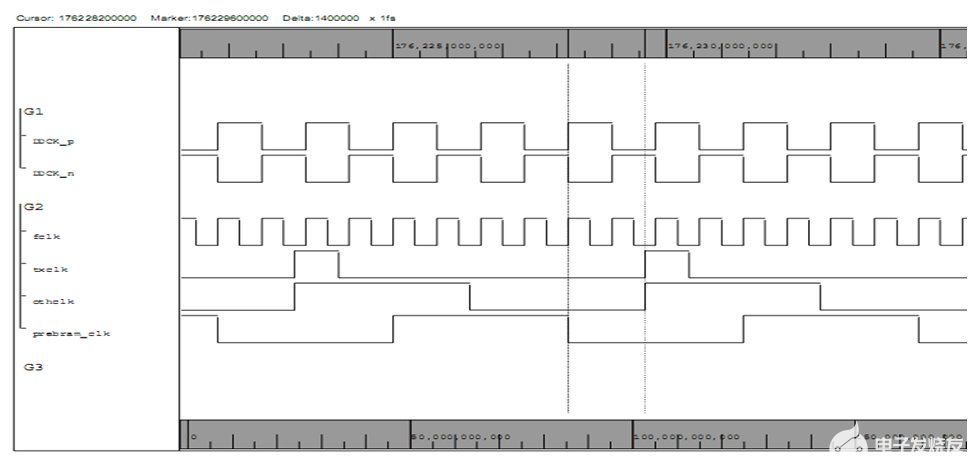

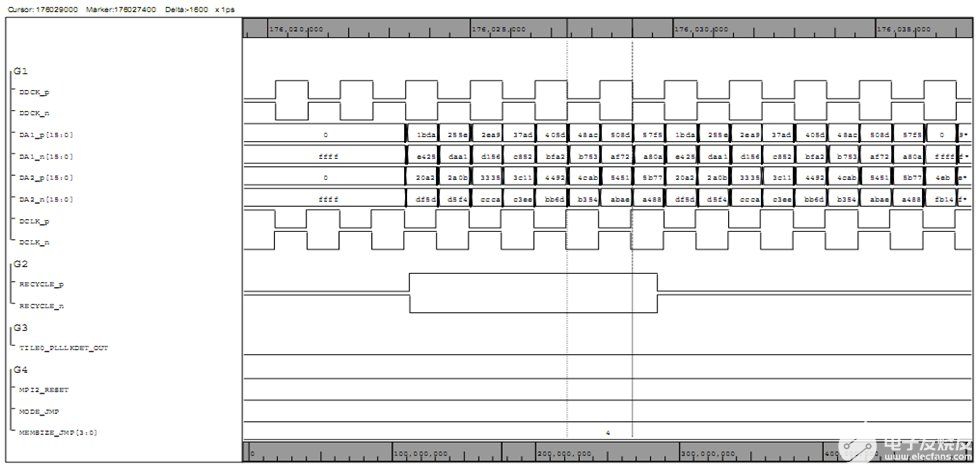

PLL的時鐘altpll_source1時序關系如下圖所示:

圖 11:PLL altpll_source1 時序圖

DCKO從LTC2000 DAC更新時鐘除以4,頻率高達625MHz的頻率被饋入PLL(altpll_source1)作為發送器的參考時鐘。fclk 和 txclk 被傳送到差分發送器 (altlvds_tx1),以生成數據流 DA1、DA2 和 DAC 數據輸入時鐘 DCLK。txclk 占空比和 txclk、其他相位需要根據 FPGA 后放置和布線時序報告進行調整,以滿足時序要求。當前設置為:13%、101.25 度、101.25 度。不同的FPGA器件、實現甚至不同的電路板制造都可能需要重新調整。

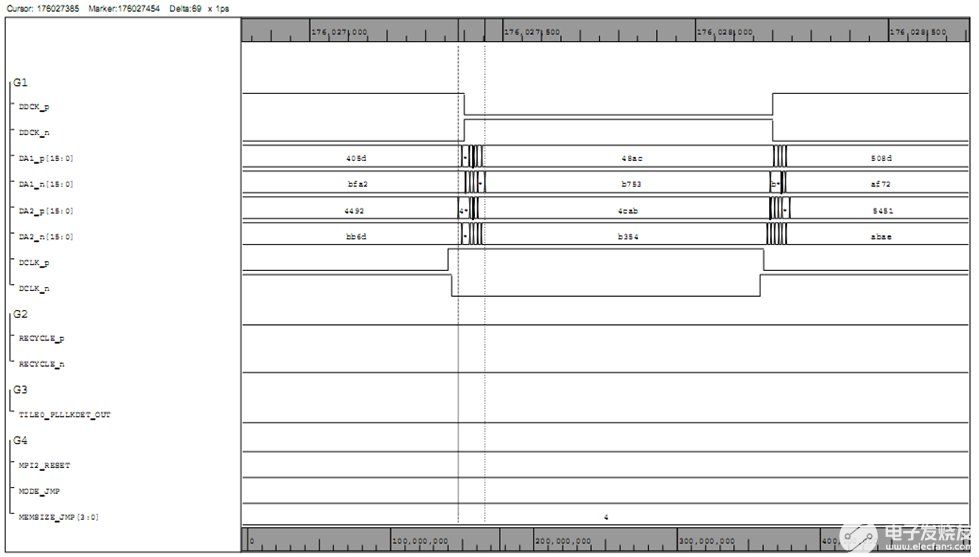

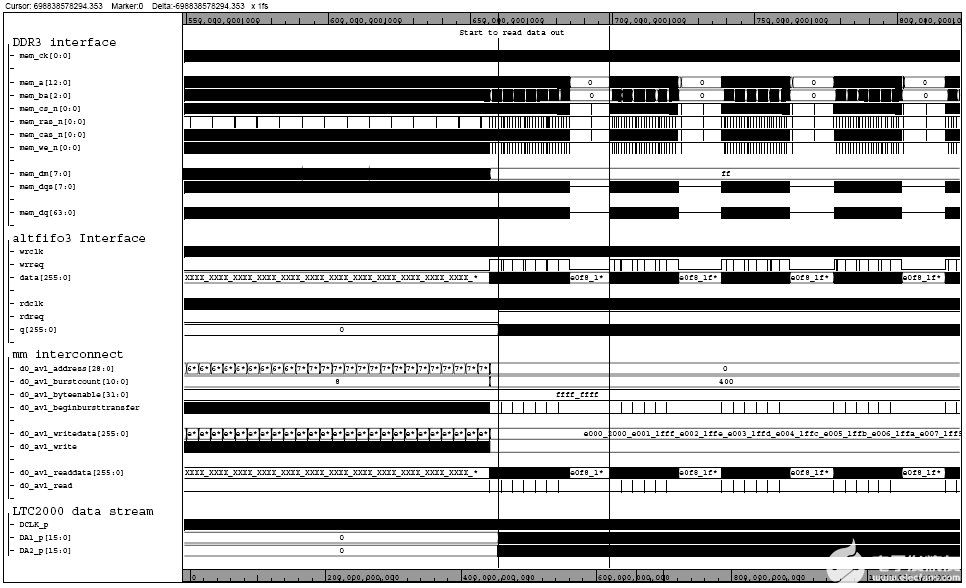

圖 12:2.5Gsps 時的功能仿真

圖 13:2.5Gsps 時的放置和布線仿真

圖 14:2.5Gsps 數據線偏斜時的放置后和布線仿真

DAC數據存儲在STRATIX FPGA板上的外部512MBTE DDR3 SDRAM模塊中。DDR3內存控制器設計基于ALTERA IP,DDR3 SDRAM控制器和UniPHY v13.1。該IP由高性能控制器II(HPCII)和UniPHY組成,UniPHY是外部存儲器接口的物理層。HPC II 提供高內存帶寬、高時鐘速率性能和運行時可編程性。控制器可以通過將讀取和寫入分組在一起來對數據進行重新排序,以減少行沖突和總線周轉時間,從而實現高效的流量模式并減少延遲。該 IP 由 ALTERA 工具“超級向導管理器”生成。必須從 IP 中刪除 ALTERA Avalon-MM 流量處理器。有關帶 UniPHY 的 DDR3 SDRAM 控制器和 IP 生成流程的更多詳細信息,請參閱 http://www.altera.com/literature/lit-external-內存接口.jsp。

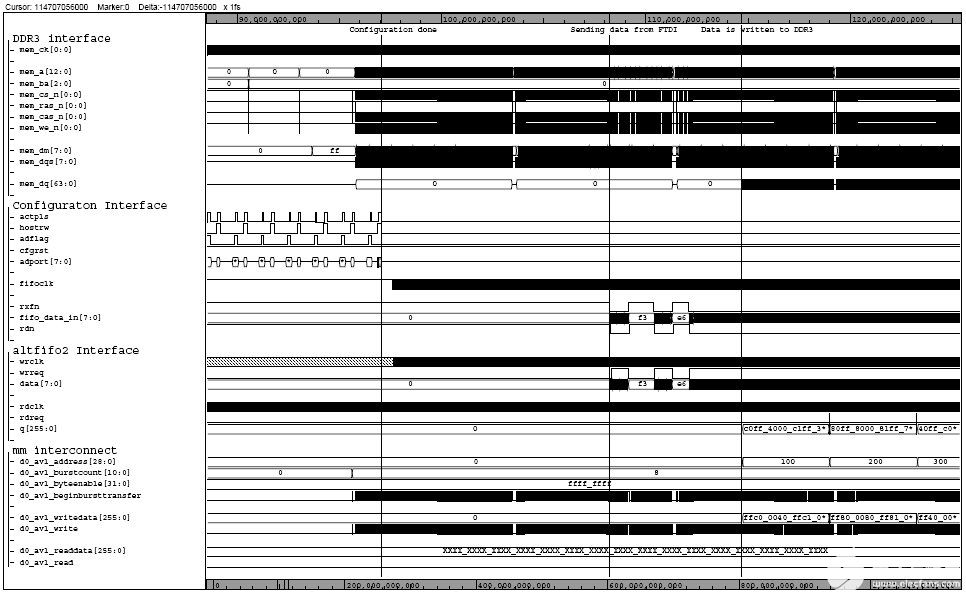

構建了一個特殊的接口,用于通過HSMC連接FT2232,以從主機PC上傳DAC數據。在數據傳輸之前,FT2232必須設置為同步FIFO模式。DC2085A板中FPGA和FT2232之間的引腳連接關系如圖15所示。

圖 15:DC 2085A 板的 FT2232 部分

寫入過程由 rxfn 觸發,并由 FT2232 驅動。當低時,表示DAC數據在FT2232的FIFO中可用。FPGA通過驅動低電平RDN來響應它,以通過8位端口fifo_data_in捕獲從FT2232的內部FIFO到altfifo2(FPGA的8位x 512 FIFO)的數據。此 FIFO 將數據總線擴展至 256 位寬,并寫入 DDR3 控制器模塊mm_interconnect。mm_interconnect發出命令以初始化外部 DDR3 SDRAM,將數據轉換為 128 位格式,并通過 UniPYH if0 將數據發送到外部 DDR3 內存。如圖16所示,寫入流程完全由電路f2m_ctrol控制。當所有數據存儲在存儲器中時,f2m_ctrl向電路m2f_ctrl提交命令以啟用讀取流。數據從DDR3讀取到FHY以及mm_interconnect。構建了一個電路,用于將 Avalon 總線連接到 256 位 x 4096 FIFO altfifo3。FIFO altfifo3將數據從266.5MHz突發傳輸總線緩沖到156.26MHz不間斷傳輸總線,如圖17所示。FIFO輸出端口直接驅動差分變送器altlvds_tx1。差分發送器產生兩個具有 1.6Gsps 帶寬、16 位 LVDS SERDES 電路的數據流,并通過 HSMC 連接器傳輸到 LTC2000,如圖 10 所示。讀取流程完全由電路m2f_ctrol控制。DDR3 控制器的效率會影響 266.5MHz 總線操作。較低的效率會破壞156.26MHz不間斷總線,需要使用更大的FIFO。影響效率的兩個主要因素是內存供應商指定的接口標準以及傳輸數據的方式。

圖 16:altfifo2 捕獲的數據寫入 DDR3

圖 17:圖 17:從 DDR3 讀取的數據通過 altfifo3 和 LVDS SERDES 傳輸到 LTC2000

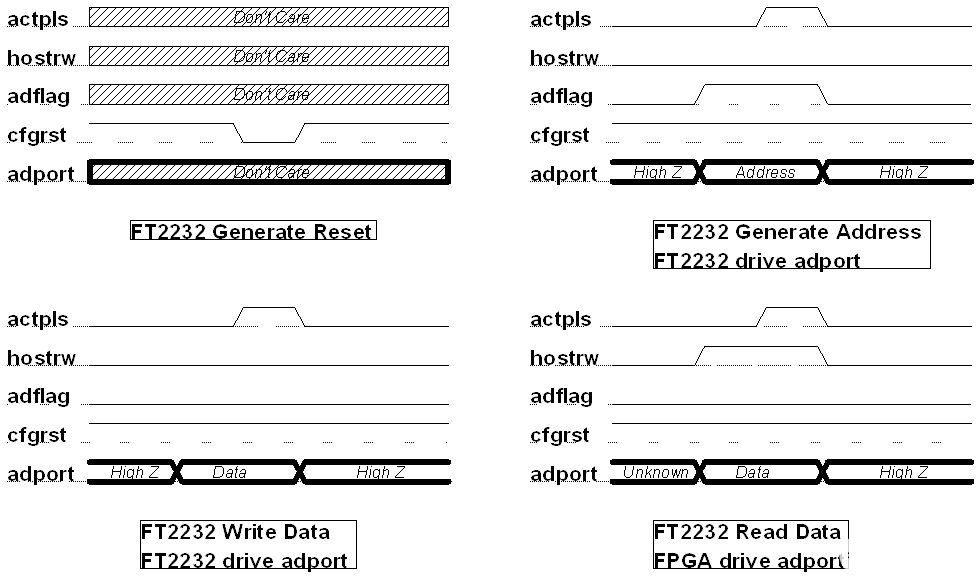

f2m_ctrl和m2f_ctrl由 FTDI 配置配置,FTDI 通道 B 訪問該配置如圖 15 所示。12 位 GPIO 按照以下協議構建寄存器映射訪問總線:

圖 18:FT2232 配置端口協議

下表列出了整個 FPGA 寄存器映射:

表 10:FPGA ID 寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 身份證 | |||||||

| 讀/寫 | 讀/寫 | |||||||

| 初始值 | 0x1a | |||||||

表 11:FPGA 控制寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 記憶大小 | 呼吸道合胞病毒 | 模式 | |||||

| 讀/寫 | 讀/寫 | |||||||

| 初始值 | 0x00 | |||||||

RSV:儲備

模式:1:一幀,只發送緩沖區數據直到緩沖區結束 0:環回,從緩沖區的開始到結束連續發送緩沖區數據,直到時鐘停止

內存大小:緩沖區大小選擇

表 12:緩沖區大小配置

| 記憶大小 | 緩沖區大小 |

| 0 | 16K 樣本 |

| 1 | 32K 樣本 |

| 2 | 64K 樣本 |

| 3 | 128K 樣本 |

| 4 | 256K 樣本 |

| 5 | 512K 樣本 |

| 6 | 1M 樣品 |

| 7 | 2M 樣品 |

| 8 | 4M 樣品 |

| 9 | 8M 樣品 |

| 10 | 16M 樣品 |

| 11 | 32M 樣品 |

| 12 | 64M 樣品 |

| 13 | 128M 樣品 |

| 14 | 256M 樣品 |

未知值將被識別為 16K 設置

表 13:FPGA 狀態寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 呼吸道合胞病毒 | 弗拉夫 | 弗雷德富爾 | 德甲司 | 鎖相環2 | 鎖相板1 | 鎖相點0 | 德普爾 |

| 讀/寫 | 讀 | |||||||

| 初始值 | 0x00 | |||||||

FWRFUL:向外部 DDR3 寫入數據的 FIFO 已滿。

FRDFUL:從外部DDR3讀取數據的FIFO已滿。

DDRPLL:DDR 控制器的嵌入式 PLL 已鎖定。

DDRRDY:外部 DDR 已準備好訪問。

PLL0:接受系統CLK的PLL被鎖定。

PLL1:接受 DDCK 的 PLL 已鎖定。

PLL2:接受 fifoclk 的 PLL 被鎖定。

表 14:DAC 關斷寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 呼吸道合胞病毒 | DACPD | ||||||

| 讀/寫 | 寫 | |||||||

| 初始值 | 0x00 | |||||||

RSV:儲備

DACPD:1:打開 DAC

0:關閉 DAC

FPGA 設計實現了用于 FPGA 配置和狀態顯示的全功能 LCD 驅動器。它支持連接到STRATIX IV GX FPGA開發板的Lumex LCD模塊SML-LX1206GC-TR。

LCD驅動器電路lcdrw_ctrl,lcdfl_ctrl由FPGA板載100MHz振蕩器的專用時鐘域SYSCLK計時。下圖是兩行32個字符的液晶顯示屏:

圖 19:液晶顯示屏

| F | P | G | 一個 | : | X | X | X | M | O | D | E | : | Y | Y | |

| B | U | F | S | 我 | Z | E | : | Z | Z | Z | Z | S | P | s |

表15:液晶屏顯示信息

| 字符 | 顯示 | 描述 |

| 三十 | ||

| FST | 配置重置 | |

| 英國夏令時 | 按鈕復位 | |

| IF0 | DDR3 控制器未就緒 | |

| .CFG | 配置期間 | |

| 時鐘 | 無 LTC2000 時鐘輸入 | |

| 跑 | 正常運行期間 | |

| YY | ||

| 中頻 | 環回模式 | |

| 順豐 | 單幀模式 | |

| 茲茲 | (樣本計數) | 請參閱表3 緩沖區大小 |

參考設計

表 16:參考設計矩陣

| 參數 | 描述 |

| 常規 | |

| 開發者名稱 | 俞斌 |

| 目標設備 | 斯特拉蒂克斯 IV GX FPGA EP4SGX230KF40 |

| 提供的源代碼 | 是的 |

| 源代碼格式 | 是的 |

| 設計使用現有參考中的代碼或 IP 設計、應用說明、第三方或 超級向導?軟件 | 是的 |

| 模擬 | |

| 執行功能模擬 | 是的 |

| 執行時序仿真 | 是的 |

| 為功能和時序仿真提供測試平臺 | 是的 |

| 測試平臺格式 | 威瑞洛格 |

| 模擬器軟件和版本 | NCVerilog (64位) 08.20-s014 |

| 香料/宜必思模擬 | 不 |

| 實現 | |

| 合成軟件工具和版本 | 四重奏 II v13.1.0 |

| 實施軟件工具和版本 | 四重奏 II v13.1.0 |

| 執行靜態時序分析 | 是的 |

| 硬件驗證 | |

| 硬件驗證 | 是的 |

| 用于驗證的硬件平臺 | 凌力爾特DC2085A板和STRATIX IV GX FPGA開發板 |

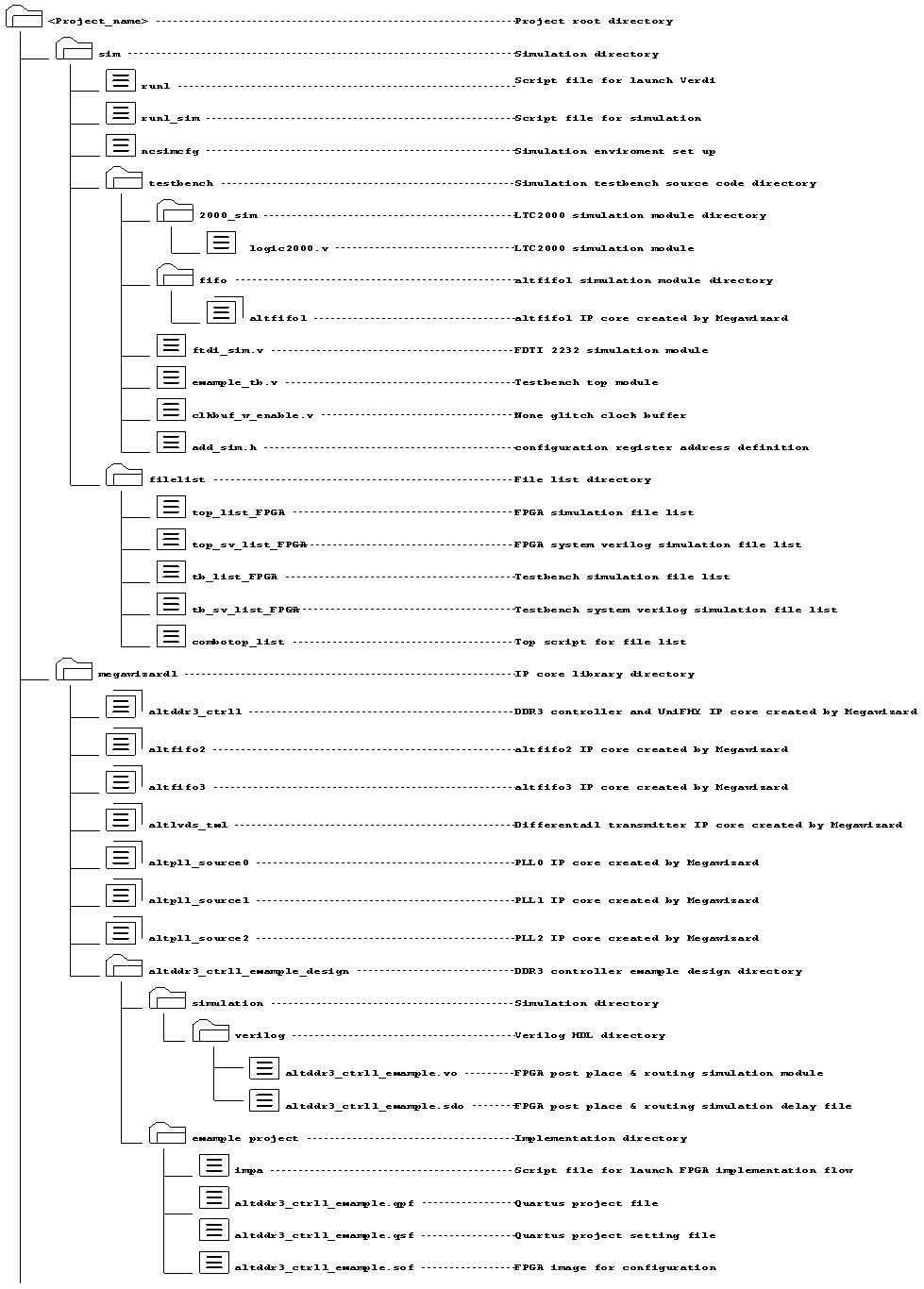

整個設計、仿真和實現環境在 redhat LINUX 操作系統上呈現。目錄的設置如圖 20 所示。

圖 20:設計和仿真文件文件夾

系統配置流程

接通 LTC2000 更新時鐘源。

打開 FPGA 板電源(系統時鐘應存在)。

打開 FPGA 板電源(系統時鐘應存在)。

打開 DC2085A 板電源。

加載 FPGA 映像。

將 FTDI 配置為 MPSSE 模式。

在FTDI的GPIOL3/BDBUS7上生成FPGA的復位脈沖。

通過 FTDI 配置端口檢查 FPGA ID 寄存器,以驗證 FPGA 映像是否正確。

設置 FPGA 控制寄存器位 MEMSIZE 和 MODE,以配置緩沖器大小和傳輸模式。

通過設置 DAC 關斷寄存器位 DACPD 來接通 LTC2000。

通過 FTDI 配置 LTC2000 至 SPI。

通過FTDI配置端口檢查FPGA時鐘狀態寄存器位DDRRDY,PLL0,PLL1,DDRPLL以驗證系統時鐘;檢查 STRATIX FPGA 板和 LTC2000 的 DDR3 控制器參考時鐘和 DDCK 是否可用。DDR3 初始化完成。

將 FTDI 配置為 FIFO 模式。

開始通過FTDI向FPGA發送DAC數據。

監視 LCD 顯示和來自 LTC2000 輸出的波形。

結論

Altera Stratix 4 GX FPGA系列具有許多有用的特性,允許設計一個與LTC2000的穩健接口。本應用筆記中的設計可直接用作DAC的評估工具。高速數據接口可用作客戶設計的起點。

審核編輯:郭婷

-

FPGA

+關注

關注

1645文章

22026瀏覽量

617620 -

轉換器

+關注

關注

27文章

9027瀏覽量

151564 -

lvds

+關注

關注

2文章

1124瀏覽量

67386

發布評論請先 登錄

M12連接器貴不貴

TSW1400單獨與ADC 4229連接時,ADC所需的時鐘頻率低頻可以嗎?

M12連接器:工業應用的多功能連接器

LFH200連接器應用于PXI板卡端口

工業級RJ45連接器優勢這么強?揭秘“RJ45連接器天花板”-凌科BD系列產品

詳解FPGA的基本結構

如何利用FPGA系列的專用I/O功能將LTC2000連接至FPGA上

如何利用FPGA系列的專用I/O功能將LTC2000連接至FPGA上

評論